Desde a sua estreia na década de 1980, com LANs compartilhadas de 10 Mbps sobre cabos coaxiais, a Ethernet tem visto avanços consistentes, agora com potencial para suportar velocidades de até 1.6 Tbps. Esta progressão permitiu que a Ethernet atendesse a uma gama mais ampla de aplicações, como transmissão ao vivo, redes de acesso por rádio e controle industrial, enfatizando a importância da transferência confiável de pacotes e da qualidade do serviço. Com a atual largura de banda da Internet girando em torno de 500 Tbps, há uma demanda crescente por uma melhor manipulação do tráfego intradatacenter de back-end. Embora os servidores individuais ainda não estejam operando em níveis de Terabit por segundo, o tráfego geral do datacenter está se aproximando dessa escala, levando o grupo 802.3dj do IEEE a empreender esforços de padronização e necessitando de controladores Ethernet robustos e SerDes para gerenciar o fluxo de dados em expansão. Em meio a esse cenário de demandas crescentes, a comunicação entre processadores já está atingindo essas velocidades.

A comunicação entre processadores está liderando a necessidade de taxas de 1.6T com latência mínima. Embora os dispositivos individuais sejam limitados pelas suas capacidades de processamento inerentes e pelo tamanho do chip, a combinação de chips pode ampliar significativamente essas capacidades. Espera-se que a primeira geração de aplicativos seja seguida por conexões switch a switch intradatacenter, permitindo o agrupamento de processadores e memória de alto desempenho, aumentando a escalabilidade e a eficiência na computação em nuvem.

Iniciativa 802.3dj do IEEE: Avanço dos padrões Ethernet para interoperabilidade de 1.6 Tbps

A conformidade com os esforços de padronização em evolução é fundamental para a interoperabilidade contínua do ecossistema. O grupo 802.3dj do IEEE está em processo de formulação do próximo padrão Ethernet, que abrange camadas físicas e parâmetros de gerenciamento para velocidades de 200G até 1.6 Terabits por segundo. O objetivo do grupo é uma taxa de dados Ethernet MAC de 1.6 Tbps, visando uma taxa máxima de erro de bit não superior a 10-13 na camada MAC. Outras provisões incluem Interfaces de Unidade de Anexação (AUI) opcionais de 16 e 8 pistas adequadas para diferentes aplicações de chip, aproveitando SerDes 112G e 224G. Fisicamente, a especificação de 1.6 Tbps envolve transmissão através de 8 pares de cabos twinax de cobre para até um metro e 8 pares de fibra para distâncias entre 500 metros e 2 km. Embora a ratificação completa da norma esteja prevista para a primavera de 2026, o conjunto principal de recursos está previsto para ser concluído em 2024.

Sobrecarga de largura de banda e correção de erros em subsistemas Ethernet 1.6T

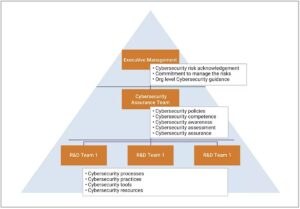

Figura 1: Diagrama representando os componentes de um subsistema Ethernet 1.6T.

Nas iterações anteriores da Ethernet, o PCS concentrava-se principalmente na codificação de dados para detecção confiável de pacotes. No entanto, com a escalada para velocidades Ethernet de 1.6T, a necessidade de Forward Error Correction (FEC) torna-se evidente, especialmente para neutralizar a degradação do sinal, mesmo em links curtos. Para este propósito, a Ethernet 1.6T continua a utilizar Reed-Solomon FEC. Esta abordagem constrói uma palavra-código composta por 514 símbolos de 10 bits codificados em um bloco de 544 símbolos, resultando em uma sobrecarga de largura de banda de 6%. Essas palavras-código FEC são distribuídas pelos links físicos da AUI para que cada link físico (8 para Ethernet 1.6T) não carregue uma palavra-código inteira. Este método não apenas oferece proteção adicional contra surtos de erros, mas também permite a paralelização no decodificador da extremidade oposta, reduzindo assim a latência.

O Physical Medium Attachment (PMA), com caixa de engrenagens e SerDes, traz o sinal Ethernet para os canais transmitidos. Para Ethernet 1.6T, isso envolve 8 canais, cada um rodando a 212 Gbps, representando uma sobrecarga FEC de 6%. A técnica de modulação empregada é a Modulação de Amplitude de Pulso de 4 Níveis (PAM-4), que codifica dois bits de dados para cada símbolo de transmissão, duplicando efetivamente a largura de banda quando justaposta à abordagem tradicional Non-Return Zero (NRZ). O mecanismo de transmissão depende da conversão digital para analógico, enquanto na extremidade receptora uma conversão analógico-digital combinada com DSPs garante a extração precisa do sinal.

Além disso, é importante observar que o Ethernet PCS introduz um “FEC externo” que se estende de ponta a ponta em um link Ethernet. Para reforçar canais de alcance mais longo, uma camada adicional de correção de erros para linhas físicas individuais está em preparação, provavelmente adotando um código de Hamming FEC. Prevê-se que esta correção encontre sua aplicação principal em módulos transceptores ópticos onde tal correção é imperativa.

2: Diagrama mostrando sobrecarga adicional adicionada ao usar um FEC concatenado para alcance estendido.

No sistema exemplar representado na figura 2, o MAC e o PCS são conectados através de um módulo óptico e um trecho de fibra. O PCS tem uma taxa de erro de bit de 10-5 no link do módulo óptico, além de erros do próprio link óptico. Usar um único RS-FEC de ponta a ponta não seria suficiente para atingir os 10-13 Padrão Ethernet, tornando o link não confiável. Uma opção seria uma implementação tripla de RS FEC separado em cada salto, aumentando significativamente os custos e a latência. Uma solução mais eficaz é a integração de um Código de Hamming FEC concatenado especificamente para o enlace óptico, atendendo aos erros aleatórios típicos das conexões ópticas. Esta camada FEC interna cria uma expansão adicional da taxa de linha de 212 Gbps para 226 Gbps, portanto é essencial que o SerDes possa suportar esta taxa de linha.

Desafios de latência em sistemas Ethernet 1.6T

Figura 3: Caminho de latência para subsistema Ethernet 1.6T.

Vários componentes contribuem para a latência da Ethernet: a fila de transmissão, a duração da transmissão, o tempo médio de passagem e vários tempos de processamento e recebimento. Para visualizar isso, considere a figura 3, que exibe um subsistema Ethernet 1.6T abrangente. Embora a latência possa ser influenciada pelo tempo de reação da aplicação remota, esse fator é externo à Ethernet e, portanto, frequentemente excluído durante a análise de latência. Minimizar a latência na interface Ethernet requer a compreensão das circunstâncias específicas. Por exemplo, a latência pode não ser a principal preocupação para conexões de tronco entre switches devido a atrasos inerentes em links de clientes mais lentos. A distância também desempenha um papel; comprimentos maiores introduzem mais latência. Claro, isso não significa que devemos ignorar a latência em outros cenários, reduzir a latência é sempre um objetivo.

A latência de transmissão está inerentemente ligada à taxa Ethernet e ao tamanho do quadro. Especificamente, para um sistema Ethernet 1.6T, a transmissão de um pacote de tamanho mínimo requer 0.4ns – essencialmente, um quadro Ethernet por tick de um clock de 2.5 GHz. Por outro lado, a transmissão de um quadro padrão de tamanho máximo leva 8ns, estendendo-se até 48ns para Jumbo Frames. O meio escolhido determina ainda mais a latência. Por exemplo, a fibra óptica normalmente incorre numa latência de 5ns por metro, enquanto o cabeamento de cobre é ligeiramente mais rápido, a 4ns por metro.

Um segmento substancial da latência geral está enraizado no controlador do receptor. O decodificador RS FEC introduz latência inerentemente. Para iniciar a correção de erros, o sistema deve receber 4 palavras-código, o que, em 1.6Tbps, equivale a 12.8ns. As atividades subsequentes, incluindo correção de erros e armazenamento em buffer, amplificam essa latência. Embora a duração do armazenamento da palavra-código FEC permaneça consistente, a latência durante a recepção da mensagem depende da implementação específica. No entanto, a latência pode ser otimizada através do emprego de estratégias meticulosas de design digital.

Em essência, existe uma latência inerente e inevitável devido ao mecanismo FEC e à distância física ou comprimento do cabo. Além desses fatores, a experiência em design desempenha um papel fundamental para minimizar a latência do controlador Ethernet. Aproveitar uma solução completa que integra e otimiza MAC, PCS e PHY abre caminho para a implementação mais eficiente e de baixa latência.

Resumo

4: Sucesso de silício de primeira passagem para Synopsys 224G Ethernet PHY IP em processo de 3 nm apresentando olhos PAM-4 altamente lineares.

A Ethernet de 1.6 Tbps é adaptada para as aplicações mais exigentes em termos de largura de banda e sensíveis à latência. Com o surgimento da tecnologia 224G SerDes, em conjunto com os avanços no MAC e PCS IP, agora estão acessíveis soluções abrangentes que estão continuamente em conformidade com os padrões Ethernet 1.6T em evolução. Além disso, devido à latência intrínseca ao protocolo e aos métodos de correção de erros, o projeto IP digital e analógico deve ser cuidadosamente elaborado por projetistas especializados para evitar a introdução de latência desnecessária no caminho de dados.

Alcançar o melhor desempenho para projetos de SoC 1.6T requer uma arquitetura eficientemente otimizada e práticas de design meticulosas para cada componente do chip. Isto enfatiza a conservação de energia e minimiza a pegada de silício, tornando as taxas de dados de 1.6T uma realidade. Synopsys 224G Ethernet PHY IP comprovado com silício preparou o cenário para o controlador 1.6T MAC e PCS. Usando técnicas de ponta de design, análise, simulação e medição, a Synopsys continua a oferecer excepcional integridade de sinal e desempenho de jitter, com um solução Ethernet completa incluindo MAC+PCS+PHY.

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoData.Network Gerativa Vertical Ai. Capacite-se. Acesse aqui.

- PlatoAiStream. Inteligência Web3. Conhecimento Amplificado. Acesse aqui.

- PlatãoESG. Carbono Tecnologia Limpa, Energia, Ambiente, Solar, Gestão de resíduos. Acesse aqui.

- PlatoHealth. Inteligência em Biotecnologia e Ensaios Clínicos. Acesse aqui.

- Fonte: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :tem

- :é

- :não

- :onde

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- Acesso

- acessível

- Contabilidade

- preciso

- Alcançar

- em

- atividades

- adicionado

- Adicional

- Adicionalmente

- Adotando

- avanços

- Avançando

- contra

- Visando

- permitidas

- já

- tb

- Apesar

- sempre

- entre

- quantidades

- amplificar

- an

- análise

- e

- Antecipado

- Aplicação

- aplicações

- abordagem

- arquitetura

- SOMOS

- AS

- At

- evitar

- Back-end

- pano de fundo

- Largura de Banda

- BE

- torna-se

- entre

- Pós

- Pouco

- Bloquear

- reforçar

- impulsionar

- Traz

- Constrói

- mas a

- by

- cabo

- cabos

- CAN

- capacidades

- transportar

- desafios

- canais

- lasca

- Chips

- escolhido

- circunstâncias

- cliente

- Relógio

- Na nuvem

- computação em nuvem

- código

- combinado

- combinando

- Comunicação

- completar

- realização

- componente

- componentes

- compreensivo

- composta

- computação

- Interesse

- conjunção

- conectado

- Coneções

- CONSERVAÇÃO

- Considerar

- Considerações

- consistente

- continua

- continuamente

- contribuir

- ao controle

- controlador

- Conversão

- Cobre

- núcleo

- custos

- contrariar

- curso

- Crafted

- cria

- Atual

- dados,

- Datacenter

- estréia

- atrasos

- entregar

- Demanda

- exigente

- demandas

- retratando

- Design

- desenhadores

- projetos

- Detecção

- Dispositivos/Instrumentos

- dita

- diferente

- digital

- diligentemente

- monitores

- distância

- distribuído

- Não faz

- duplicação

- dois

- duração

- durante

- cada

- Mais cedo

- ecossistema

- Eficaz

- efetivamente

- eficiência

- eficiente

- eficientemente

- esforços

- emergência

- enfatiza

- enfatizando

- empregada

- empregando

- permite

- permitindo

- engloba

- final

- end-to-end

- garante

- Todo

- erro

- erros

- escalada

- essência

- essencial

- essencialmente

- Éter (ETH)

- Mesmo

- Cada

- evidente

- evolução

- exemplo

- excepcional

- excluídos

- expansão

- expansão

- esperado

- especialista

- experiência

- estender

- estendendo

- externo

- Extração

- Olhos

- fator

- fatores

- longe

- mais rápido

- Funcionalidades

- Apresentando

- Figura

- Encontre

- Primeiro nome

- Primeira geração

- fluxo

- focado

- seguido

- Pegada

- Escolha

- formulação

- para a frente

- QUADRO

- da

- mais distante

- geração

- dá

- maior

- Grupo

- Do grupo

- Crescente

- mão

- Manipulação

- Alta

- alta performance

- altamente

- Contudo

- HTML

- HTTPS

- imperativo

- implementação

- importância

- importante

- melhorado

- in

- Em outra

- incluir

- Incluindo

- aumentando

- Individual

- industrial

- influenciado

- inerente

- inerentemente

- iniciar

- Iniciativa

- instância

- Integra-se

- integração

- integridade

- Interface

- interfaces de

- Internet

- Interoperabilidade

- para dentro

- intrínseco

- introduzir

- Introduz

- introduzindo

- envolve

- IP

- IT

- iterações

- ESTÁ

- se

- jpg

- Pista

- Latência

- camada

- camadas

- Comprimento

- níveis

- aproveitando

- Provável

- Line

- linhas

- LINK

- Links

- viver

- mais

- Baixo

- mac

- Fazendo

- gerencia

- de grupos

- max-width

- máximo

- Posso..

- significar

- medição

- mecanismo

- média

- Memória

- mensagem

- método

- métodos

- meticuloso

- mínimo

- minimizar

- minimiza

- minimizando

- módulo

- Módulos

- mais

- a maioria

- devo

- aproximando

- você merece...

- redes

- mesmo assim

- não

- nota

- agora

- objetivo

- of

- frequentemente

- on

- ONE

- só

- operando

- otimizado

- Otimiza

- Opção

- or

- Outros

- Acima de

- global

- pares

- parâmetros

- particularmente

- caminho

- PCs

- para

- atuação

- performances

- físico

- Fisicamente

- oleoduto

- essencial

- platão

- Inteligência de Dados Platão

- PlatãoData

- desempenha

- mais

- potencial

- poder

- práticas

- principalmente

- primário

- processo

- em processamento

- processadores

- progressão

- projetado

- proteção

- protocolo

- pulso

- propósito

- Empurrando

- qualidade

- Rádio

- acaso

- alcance

- Taxa

- Preços

- alcançar

- chegando

- reação

- Realidade

- receber

- receber

- recepção

- redução

- confiável

- permanece

- representação

- exige

- restringido

- resultando

- uma conta de despesas robusta

- Tipo

- enraizado

- corrida

- AMPLIAR

- Escala

- cenários

- desatado

- Segundo

- visto

- segmento

- sensível

- separado

- servir

- serviço

- conjunto

- vários

- compartilhado

- Baixo

- rede de apoio social

- apresentando

- Signal

- de forma considerável

- Silício

- simulação

- Tamanho

- So

- solução

- Soluções

- vãos

- encabeçando

- específico

- especificamente

- especificação

- velocidades

- primavera

- Etapa

- padrão

- estandardização

- padrões

- armazenamento

- estratégias

- de streaming

- subseqüente

- substancial

- sucesso

- tal

- adequado

- ajuda

- símbolo

- .

- adaptados

- toma

- técnica

- técnicas

- Tecnologia

- do que

- que

- A

- deles

- Lá.

- assim

- assim sendo

- Este

- isto

- Através da

- Assim

- carrapato

- Amarrado

- tempo

- vezes

- para

- topo

- tradicional

- tráfego

- transferência

- transmite

- triplo

- dois

- típico

- tipicamente

- inevitável

- compreensão

- empreender

- unidade

- os próximos

- sobre

- utilização

- utilizar

- via

- visualizar

- Caminho..

- we

- quando

- qual

- enquanto

- mais largo

- de

- dentro

- seria

- ainda

- zefirnet

- zero