Recentemente, a TSMC realizou seu Simpósio de Tecnologia anual, fornecendo uma atualização sobre a tecnologia de processo de silício e roteiro de embalagens. Este artigo revisará os destaques do desenvolvimento do processo de silício e dos planos de lançamento futuro.

Os artigos subsequentes descreverão as ofertas de embalagens e se aprofundarão no desenvolvimento e qualificação de tecnologia especificamente para o setor automotivo. Há vários anos, a TSMC definiu quatro “plataformas” que receberiam investimentos exclusivos em P&D para otimizar ofertas técnicas específicas: computação de alto desempenho (HPC); móvel; computação de ponta/IoT (consumo/vazamento ultrabaixo); e, automotivo. O foco no desenvolvimento de processos para o mercado automotivo foi tema predominante no Simpósio e será abordado em artigo separado.

Entre parênteses, essas plataformas continuam sendo a base do roteiro da TSMC. No entanto, o segmento móvel evoluiu além dos smartphones (4G) para abranger um conjunto mais amplo de aplicações. O surgimento da “transformação digital de dados” levou a um aumento na demanda por opções de comunicação sem fio entre dispositivos de ponta e recursos de nuvem/data center – por exemplo, redes WiFi6/6E, 5G/6G (industriais e metropolitanas). Como resultado, a TSMC está enfatizando seu investimento no desenvolvimento de tecnologia de processo de RF, para atender a esse segmento em expansão.

Geral

Aqui estão alguns destaques gerais do Simpósio, seguidos de anúncios específicos de tecnologia de processos.

- amplitude de ofertas

Em 2020, a TSMC ampliou seu suporte para abranger 281 tecnologias de processos distintas, enviando 11,617 produtos para 510 clientes. Como nos anos anteriores, a TSMC declarou com orgulho “nunca fechamos uma fábrica”.

A capacidade atual em 2020 excede 12 milhões de wafers (equivalente a 12”), com investimentos de expansão para nós de processos avançados (digitais) e especializados.

- investimento em equipamentos de capital

A TSMC planeia investir um total de 100 mil milhões de dólares nos próximos três anos, incluindo uma despesa de capital de 30 mil milhões de dólares este ano, para apoiar as necessidades globais dos clientes.

![]()

A receita global da TSMC em 2020 foi de US$ 47.78 bilhões – o compromisso anual de US$ 30 bilhões com a expansão da fábrica certamente sugeriria uma expectativa de crescimento significativo e estendido do mercado de semicondutores, especialmente para as famílias de processos de 7nm e 5nm. Por exemplo, as novas fitas (NTOs) para a família de 7 nm aumentarão 60% em 2021.

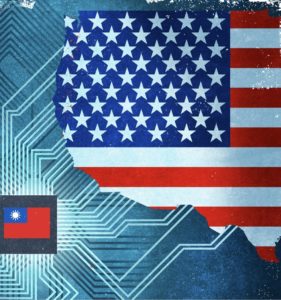

A TSMC iniciou a construção de uma fábrica nos EUA em Phoenix, AZ – a produção em volume do processo N5 começará em 2024 (~20 mil wafers por mês).

- iniciativas ambientais

As fábricas são consumidores exigentes de eletricidade, água e produtos químicos (reativos). A TSMC está focada na transição para fontes de energia 100% renováveis até 2050 (25% até 2030). Além disso, a TSMC está investindo em sistemas de reciclagem e purificação de “desperdício zero”, devolvendo os produtos químicos usados à qualidade de “grau eletrônico”.

Uma nota de advertência… A nossa indústria é notoriamente cíclica, com subidas e descidas económicas amplificadas. A mensagem clara da TSMC no Simpósio é que a adoção acelerada de semicondutores em todas as plataformas – desde centros de computação com uso intensivo de dados até comunicações sem fio/móveis, sistemas automotivos e dispositivos de baixo consumo de energia – continuará no futuro próximo.

Roteiro de tecnologia de processo

- N7/N7+/N6/N5/N4/N3

A figura abaixo resume o roteiro de tecnologia avançada.

![]()

N7+ representa a introdução da litografia EUV no processo de linha de base N7. N5 está em produção em volume desde 2020.

N3 continuará sendo uma oferta de tecnologia baseada em FinFET, com produção em volume começando no 2S2022. Comparado ao N5, o N3 fornecerá:

- +10-15% de desempenho (iso-power)

- -25-30% de potência (desempenho iso)

- +70% de densidade lógica

- +20% de densidade de SRAM

- +10% de densidade analógica

O IP básico da TSMC geralmente oferece duas bibliotecas de células padrão (de diferentes alturas de trilha) para atender ao desempenho exclusivo e à densidade lógica dos segmentos HPC e móveis. Para N3, a necessidade de “cobertura total” da faixa de desempenho/potência (e domínio de tensão de alimentação) levou à introdução de uma terceira biblioteca de células padrão, conforme ilustrado abaixo.

![]()

A capacitação do design para N3 está progredindo em direção ao status v1.0 PDK no próximo trimestre, com um amplo conjunto de IP qualificados até o 2T/3T 2022.

N4 é um “empurrão” único para o processo de produção N5 existente. Um encolhimento óptico está disponível diretamente, compatível com os designs N5 existentes. Além disso, para novos projetos (ou projetos existentes interessados em buscar uma reimplementação física), existem algumas melhorias disponíveis nas atuais regras de projeto N5 e uma atualização nas bibliotecas de células padrão.

Da mesma forma, N6 é uma atualização da família 7nm, com crescente adoção da litografia EUV (acima de N7+). A TSMC indicou: “O N7 continua sendo uma oferta chave para o número crescente de designs de aceleradores móveis e de IA 5G em 2021”.

- N7HPC e N5HPC

Uma indicação dos exigentes requisitos de desempenho da plataforma HPC é o interesse do cliente em aplicar “overdrive” de tensão de alimentação, acima do limite VDD nominal do processo. A TSMC oferecerá variantes de processo exclusivas “N7HPC” (4T21) e “N5HPC” (2T22) com suporte para overdrive, conforme ilustrado abaixo.

![]()

Haverá uma versão correspondente do design SRAM IP para essas tecnologias HPC. Como esperado, os projetistas interessados nesta opção de desempenho (melhoria percentual de um dígito) precisarão abordar o aumento do vazamento estático, os fatores de aceleração da confiabilidade do BEOL e os mecanismos de falha por envelhecimento do dispositivo. É digno de nota o investimento da TSMC no desenvolvimento e qualificação de processos especificamente otimizados para plataformas individuais. (A última variante de processo específica para HPC estava no nó de 28 nm.)

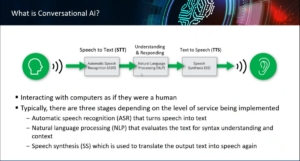

- Tecnologia RF

A demanda do mercado por comunicações sem fio WiFi6/6E e 5G (sub-6GHz e mmWave) levou a TSMC a aumentar o foco nas otimizações de processos para dispositivos de RF. Os switches RF também são uma área de aplicação importante. Protocolos de comunicação sem fio de baixo consumo de energia, como Bluetooth (com funcionalidade significativa de integração digital), também são um foco. Os sistemas de imagem por radar automotivo sem dúvida experimentarão uma demanda crescente. As aplicações mmWave estão resumidas na figura abaixo.

![]()

Os dois parâmetros principais normalmente usados para descrever o desempenho da tecnologia RF são:

- dispositivo Ft (“frequência de corte”), onde ganho de corrente = 1, inversamente proporcional ao comprimento do canal do dispositivo, L

- dispositivo Fmax (“frequência máxima de oscilação”), onde ganho de potência = 1, proporcional à raiz quadrada de Ft, inversamente proporcional à raiz quadrada de Cgd e Rg

![]()

O roteiro da tecnologia RF da TSMC é mostrado abaixo, dividido em diferentes segmentos de aplicação.

![]()

O processo N6RF foi destacado no Simpósio – uma comparação de desempenho do dispositivo com o N16FFC-RF é mostrada abaixo.

![]()

Os processos N28HPC+RF e N16FFC-RC também receberam melhorias recentemente – por exemplo, foram destacadas melhorias na resistência da porta parasita, Rg. Para aplicações de amplificadores de baixo ruído (LNA), a TSMC está evoluindo suas ofertas SOI em 130nm e 40nm.

- Tecnologias ULP/ULL

Prevê-se que as aplicações de IoT e dispositivos de borda se tornem mais difundidas, exigindo maior rendimento computacional com dissipação de energia muito baixa (ULP) combinada com dissipação de energia estática de vazamento ultrabaixo (ULL) para melhorar a vida útil da bateria.

A TSMC forneceu variantes de processo ULP – ou seja, funcionalidade operacional para IP em tensão de alimentação VDD muito baixa. A TSMC também habilitou soluções ULL, com dispositivos/IP utilizando tensões limite otimizadas.

Uma visão geral da plataforma IoT (ULP/ULL) e do roteiro do processo é fornecida abaixo.

![]()

O nó de processo N12e foi destacado pela TSMC, integrando uma tecnologia de memória não volátil incorporada (MRAM ou RRAM), com funcionalidade de célula padrão até 0.55V (usando dispositivos SVT; células de baixo Vt permitiriam menor VDD e potência ativa em maior vazamento) . Foco comparável também foi feito para reduzir o Vmin e a corrente de fuga em standby do N12e SRAM IP.

Resumo

No Simpósio, a TSMC apresentou vários novos desenvolvimentos de processos, com otimizações específicas para HPC, IoT e plataformas automotivas. Os aprimoramentos da tecnologia RF também são um foco, em apoio à rápida adoção de novos padrões de comunicações sem fio. E, com certeza, embora não tenha recebido muita ênfase no Simpósio, há um roteiro de execução claro para os nós de processos principais avançados – N7+, N5 e N3 – com melhorias contínuas adicionais nos processos, conforme refletido no lançamento de nós intermediários. nós N6 e N4.

Para obter mais informações sobre o roteiro de tecnologia digital da TSMC, siga este link.

-chipguy

Compartilhe esta postagem via: Fonte: https://semiwiki.com/semiconductor-manufacturers/tsmc/299944-highlights-of-the-tsmc-technology-symposium-2021-silicon-technology/- 11

- 2020

- 2021

- 5G

- acelerador

- ativo

- Adicional

- Adoção

- Tecnologia avançada

- AI

- Todos os Produtos

- Anúncios

- Aplicação

- aplicações

- ÁREA

- artigo

- artigos

- automotivo

- Linha de Base

- bateria

- bilhão

- Bluetooth

- Capacidade

- capital

- produtos químicos

- Comunicação

- Comunicações

- computação

- formação

- Consumidores

- continuar

- Atual

- Clientes

- dados,

- Demanda

- Design

- Desenvolvimento

- Dispositivos/Instrumentos

- Dígito

- digital

- Econômico

- borda

- eletricidade

- energia

- equipamento

- execução

- expansão

- expansão

- Falha

- famílias

- família

- Figura

- Foco

- seguir

- futuro

- Geral

- Global

- Crescente

- Growth

- Alta

- Computação de Alto Desempenho

- Destaque

- HTTPS

- Imagiologia

- Incluindo

- Crescimento

- industrial

- indústria

- INFORMAÇÕES

- integração

- interesse

- investir

- investimento

- Investimentos

- iot

- IP

- IT

- Chave

- levou

- Biblioteca

- Corrente principal

- mercado

- Móvel Esteira

- redes

- nós

- oferecendo treinamento para distância

- Ofertas

- Opção

- Opções

- acondicionamento

- atuação

- Phoenix

- plataforma

- Plataformas

- poder

- Produção

- Produtos

- qualidade

- R & D

- radar

- alcance

- reciclagem

- reduzir

- energia renovável

- Requisitos

- Recursos

- receita

- rever

- regras

- Semicondutor

- Semicondutores

- conjunto

- Envios

- Smartphones

- Soluções

- quadrado

- padrões

- Status

- supply

- ajuda

- sistemas

- Dados Técnicos:

- Tecnologias

- Equipar

- tema

- pista

- Atualizar

- us

- volume

- Água

- sem fio

- Comunicações sem fios

- ano

- anos