Os sistemas multi-matriz são compostos de diversas matrizes funcionais especializadas (ou chips) que são montadas no mesmo pacote para criar o sistema completo. Os sistemas multi-die surgiram recentemente como uma solução para superar a desaceleração da lei de Moore, fornecendo um caminho para dimensionar a funcionalidade no chip embalado de uma forma que possa ser fabricada com bom rendimento.

Além disso, os sistemas multi-die permitem flexibilidade de SKU do produto em termos de escala de desempenho para atender às necessidades de diferentes segmentos de mercado, otimização do nó de processo por função ao misturar e combinar vários nós de processo no mesmo produto, tempo de lançamento no mercado mais rápido e menor risco.

Para permitir maior densidade de roteamento de matriz a matriz e suportar tráfego de maior largura de banda entre matrizes, a tecnologia de pacotes evoluiu para criar pacotes novos e avançados, baseados em interpositores de silício (com TSVs) ou pontes de silício e, mais recentemente, camadas de redistribuição (RDL). , fanouts e substratos HD.

Um aspecto fundamental para o sucesso dos sistemas multi-matriz é a capacidade de garantir a testabilidade do sistema em diferentes fases de fabricação e montagem, bem como garantir uma operação confiável em campo. Ao usar etapas extras de montagem e tecnologias de colisão e empacotamento mais complexas, os sistemas multi-matriz exigem procedimentos de teste e confiabilidade que vão além do que era o estado da arte para projetos monolíticos.

As matrizes nuas e a própria embalagem devem ser pré-testadas para garantir que todas as matrizes ou embalagens defeituosas sejam detectadas antes de serem montadas em uma embalagem. Se uma matriz defeituosa for detectada somente após a montagem, então o sistema completo de múltiplas matrizes deverá ser descartado, com sério impacto no custo. O processo de teste de matrizes nuas é chamado de teste de matriz em boa qualidade (KGD).

O próprio processo de montagem varia de acordo com a tecnologia de embalagem selecionada. Por exemplo, as tecnologias de chip first, onde as matrizes são colocadas primeiro e a interconexão é construída sobre elas, não permitem testes de “pacotes em bom estado”, potencialmente resultando no descarte de matrizes boas se a interconexão estiver com defeito. Por outro lado, em tecnologias de chip-last, onde a interconexão é construída separadamente e as matrizes são montadas sobre ela, permitem o pré-teste do pacote antes da montagem, reduzindo a probabilidade de matrizes boas serem descartadas.

A solução de testabilidade do sistema multi-matriz pode ser dividida em vários aspectos:

- Teste a cobertura de blocos individuais dentro da matriz

- Cobertura de teste dos dados individuais (dados nus)

- Teste do sistema montado (com cobertura die-to-die)

- Acesso ao tecido de teste em matrizes nuas

- Acesso hierárquico à malha de teste após a montagem

Este artigo descreve os benefícios de uma solução abrangente de testabilidade que aproveita o UCIe IP para garantir a confiabilidade do sistema multi-die.

DFT para a interface UCIe

Uma solução de alta cobertura de teste para a interface UCIe é alcançada através da implementação de extensos recursos de testabilidade no UCIe IP para eliminar matrizes defeituosas na fase de teste de matriz nua. Alguns dos recursos incluem:

- Cadeias de varredura cobrindo todos os circuitos digitais sintetizados

- Funcionalidade BIST específica de bloco dedicado

- Funcionalidade de autoteste integrada de loopback (BIST) cobrindo toda a cadeia de sinal até o pino IO

- Sequência binária pseudoaleatória programável (PRBS) e geradores e verificadores de padrões de teste definidos pelo usuário

- Injeção de erros para eliminar passes falsos

Além disso, a funcionalidade para estender a cobertura ao link matriz a matriz, após a montagem do pacote, pode ajudar a alcançar um alto nível de cobertura de teste, incluindo:

- Funcionalidade de loopback BIST do lado oposto (die-to-die)

- Link de morrer para morrer BIST

- Margem ocular 2D para analisar marginalidades

- Funcionalidade de teste e reparo por pista

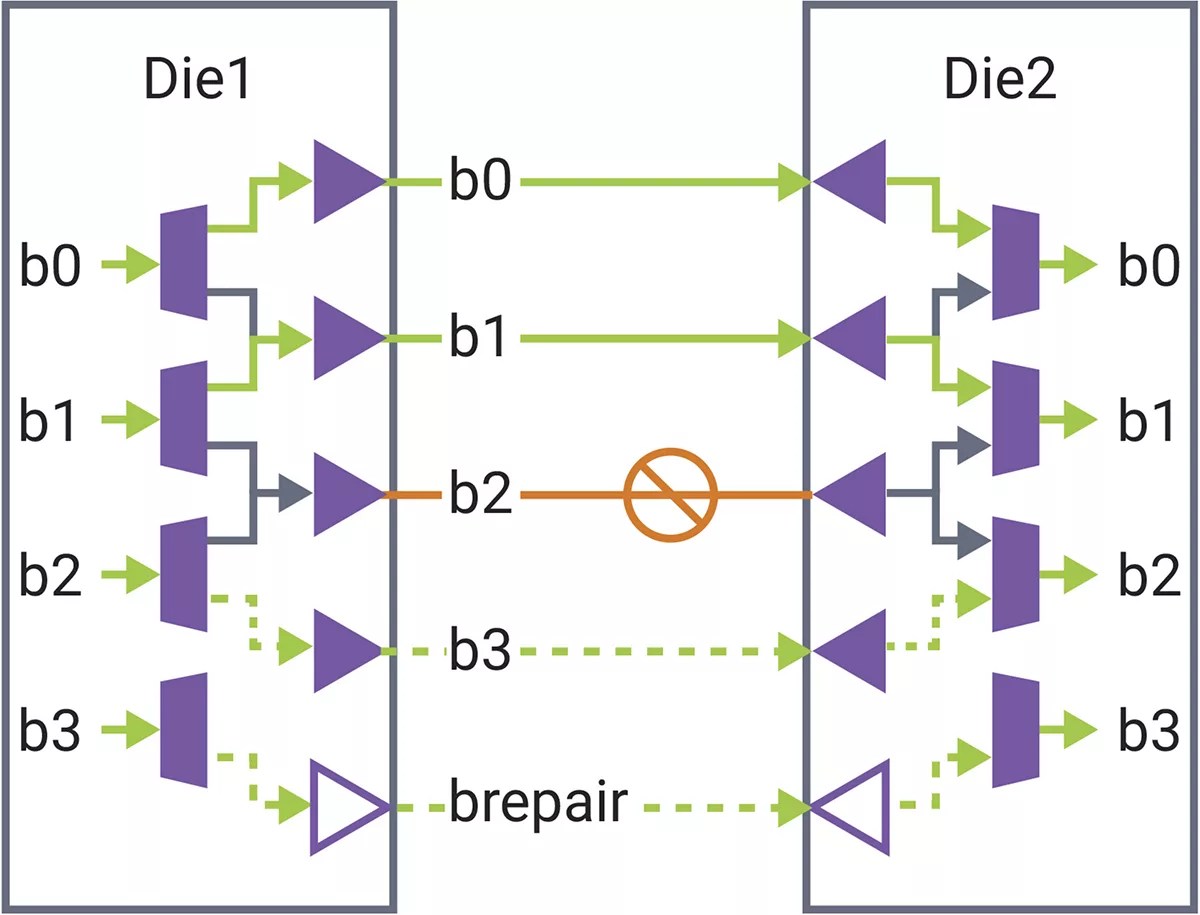

Teste e reparo UCIe

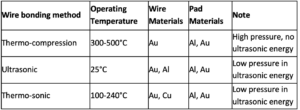

Pacotes avançados permitem roteamento de alta densidade com micro-bumping de passo fino e roteamento em interpositores de silício ou RDL. Durante o processo de montagem, algumas conexões de micro-colisões podem não estar bem formadas e podem quebrar. UCIe oferece a capacidade de testar e reparar essas conexões após a montagem de uma forma que recupere a perda potencial de rendimento.

O teste e reparo do UCIe são executados durante o teste de produção e na inicialização do link. Na fase de teste, cada link individual é verificado quanto a defeitos em baixa velocidade. Os links defeituosos são reparados redirecionando os dados para links sobressalentes predefinidos pelo padrão UCIe.

As configurações UCIe voltadas para pacotes avançados incluem até 8 pinos sobressalentes por direção (TX e RX) para permitir o reparo de todos os links funcionais:

- Quatro pinos sobressalentes para reparo de pinos de dados, 2 pinos para cada grupo de 32 pinos de dados

- Um pino sobressalente para relógios e reparos de pinos de trilha

- Três pinos sobressalentes, cada um para reparo de pino válido, pino de dados de banda lateral e pino de dados de relógio

A execução de teste e reparo ocorre quando não há tráfego válido no link die-to-die. Após a conclusão do reparo e a inicialização do link, presume-se que ele esteja bom e que o tráfego possa passar sem problemas. A configuração PHY resultante, chamada assinatura de reparo PHY, é armazenada em registros internos em ambas as extremidades do link.

A degradação, devido ao envelhecimento ou outro, das características de micro-ressaltos durante a operação pode afetar o desempenho do link. Isto será detectado no nível do protocolo por um aumento na taxa de erro de bit (BER) ou, pior, pela perda de dados. Nesse caso, espera-se que o link seja interrompido e uma nova etapa de teste e reparo seja realizada.

No entanto, algumas aplicações têm requisitos rigorosos em termos de continuidade do tráfego no link die-to-die – elas não podem tolerar a interrupção do tráfego durante a operação. Para esses casos, uma solução de testabilidade adiciona Monitores de Integridade de Sinal (SIM) a cada pino do receptor UCIe.

Fig. 1: Reparo de link usando links sobressalentes integrados.

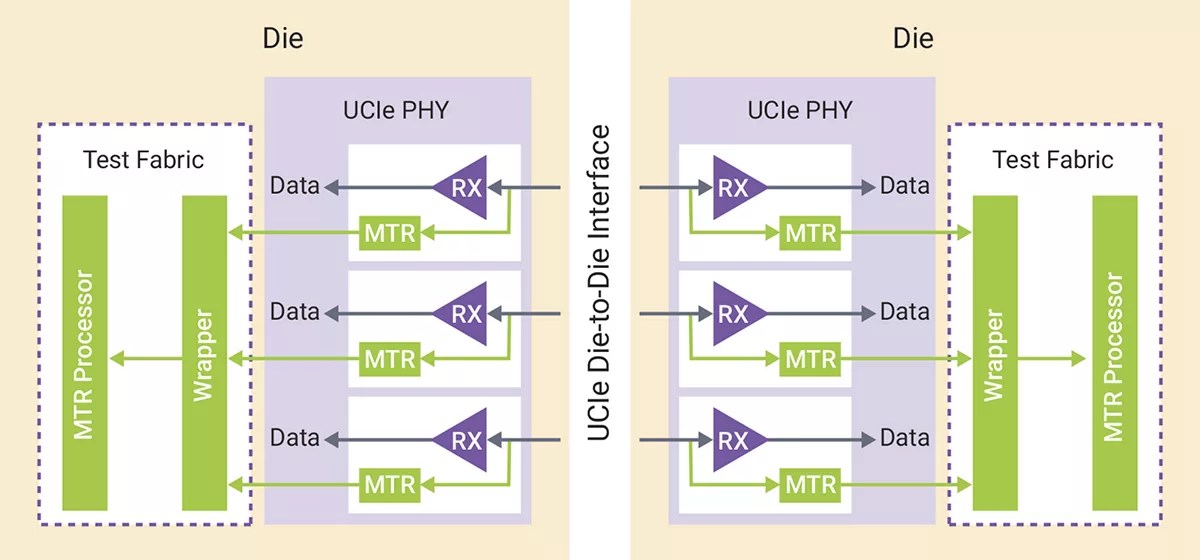

Monitores de integridade de sinal

Os monitores SIM são pequenos blocos incorporados no receptor. Eles detectam constantemente o sinal no pino receptor, durante a operação normal, para identificar variações nas características do sinal que podem impactar o desempenho do link ou indicar que o link não está mais íntegro e pode quebrar em um futuro próximo.

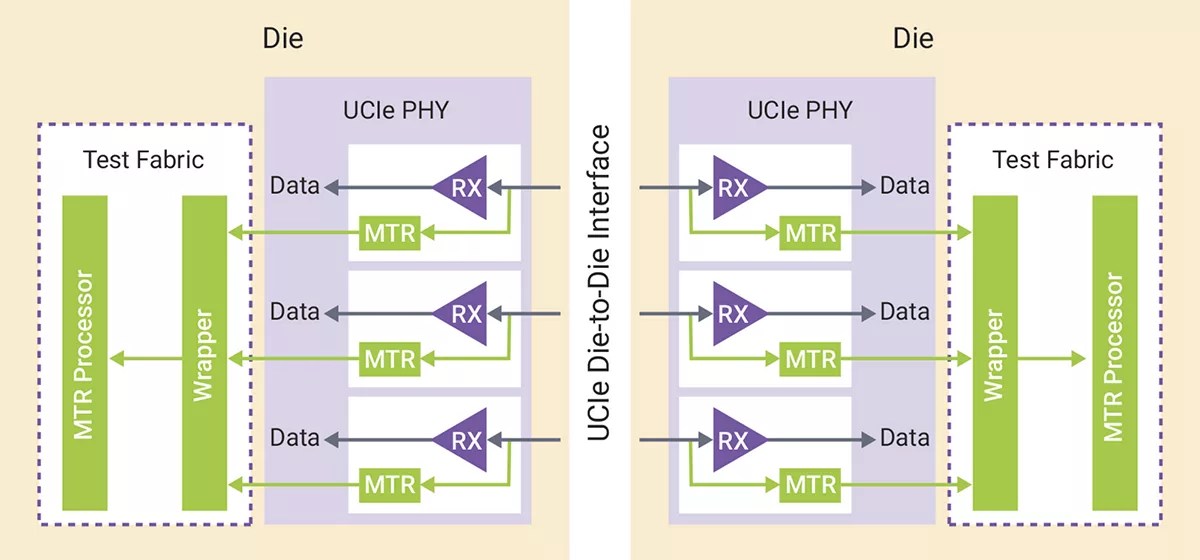

Os dados coletados pelos sensores individuais são coletados em um controlador de Monitoramento, Teste e Reparo (MTR), fora da interface, para processamento posterior. A agregação dos dados de vários links UCIe pode fornecer insights instantâneos sobre a integridade do sistema multi-die e permitir a manutenção preditiva dos links.

Se houver previsão de risco de mau funcionamento de um link específico por meio deste procedimento, ele poderá ser desativado e os dados redirecionados para um dos links sobressalentes, aproveitando o mecanismo de reparo UCIe PHY, mesmo sem interrupção do tráfego.

Figura 2: Solução de monitoramento de integridade para links UCIe.

Acelerando o tempo de despertar

Embora o padrão de tráfego para a maioria dos casos de uso de interfaces die-to-die, por exemplo, na divisão ou escalonamento de servidores, seja considerado estável durante a operação, em alguns casos de uso o tráfego pode apresentar um comportamento em rajadas. Nesses casos, é desejável colocar a interface em modo de baixo consumo de energia para economizar energia enquanto não há tráfego. A reinicialização do link pode ser acelerada evitando o processo de teste e reparo e contando com a assinatura de reparo UCIe PHY que foi criada durante a inicialização PHY anterior.

Este conceito pode ser estendido ainda mais para situações em que a matriz está completamente desligada. Nestes casos, a assinatura de reparo PHY é recuperada do PHY e armazenada em uma memória permanente on-die (eFuse ou flash). A memória poderia armazenar múltiplas assinaturas, cobrindo diferentes casos ou condições de uso, permitindo flexibilidade adicional ao usuário.

Acelerando os testes de matrizes com UCIe

O tempo de teste é um bem caro. É possível acelerar o tempo de teste particionando a estratégia de teste hierarquicamente para executar testes de diferentes matrizes em paralelo. A hierarquia pode ser estendida através de múltiplas matrizes em um sistema de múltiplas matrizes conectando a infraestrutura de teste das duas matrizes hierarquicamente. Tal abordagem permite o acesso a todas as matrizes no sistema de múltiplas matrizes a partir de uma única interface de teste JTAG (ou similar) na matriz principal.

Freqüentemente, a limitação do tempo de teste é o tempo para carregar ou ler os vetores de teste nas matrizes. As interfaces JTAG podem se tornar um gargalo de velocidade. Para superar esta limitação, os projetistas podem usar interfaces de alta velocidade existentes, como PCI Express (PCIe) ou USB, etc., como interfaces para o equipamento de teste. Os vetores e comandos de teste são empacotados para essa interface e desempacotados na matriz durante a fase de teste de produção.

Muitas matrizes não possuem uma interface de alta velocidade, no entanto, a interface matriz a matriz UCIe pode ser usada, durante o teste, para transportar grandes vetores de teste e comandos entre matrizes em alta velocidade. A interface UCI die-to-die estende o acesso DFT de alta velocidade em todo o sistema multi-die sem aumentar o número de pinos, o que é particularmente importante para IO e matrizes com área limitada.

Resumo

Além da interface matriz a matriz UCIe, o denominador comum que permite todos esses recursos de teste e aprimoramento de confiabilidade é uma malha de teste, reparo e monitoramento que pode conectar todos os blocos internos. A malha de teste, reparo e monitoramento abrange as diversas matrizes do sistema multi-ferramentas, fornecendo uma infraestrutura hierárquica estruturada que realiza as seguintes funções importantes:

- Gerencia os testes das matrizes individuais no sistema multi-ferramentas

- Otimiza o agendamento de testes para reduzir o tempo de teste

- Suporta acesso de teste de alta velocidade através das matrizes, através da interface UCIe

- Coleta informações das interfaces de monitoramento de integridade incorporadas na interface UCIe e permite processamento adicional em nível de sistema

- Gerencia o armazenamento da assinatura de reparo PHY em uma memória não volátil

- E muito mais

A Synopsys fornece uma solução de sistema multi-die abrangente e escalável, incluindo EDA e IP, para integração heterogênea rápida. Para uma conectividade ponta a ponta segura e confiável, a Synopsys oferece uma solução completa de Controlador UCIe, PHY e Verificação IP. Como parte da família Synopsys SLM & Test, uma solução completa de monitoramento, teste e reparo (MTR) UCIe está disponível junto com a solução STAR Hierarchical System (SHS). A solução MTR inclui monitor de integridade de sinal para medir a qualidade do sinal nas pistas UCIe, BIST para autoteste e lógica de reparo para alocação redundante de pistas, enquanto a solução SHS serve como estrutura de conectividade que suporta os padrões da indústria IEEE 1687, IEEE 1149.1 e IEEE 1838 interfaces. Esta solução completa permite o monitoramento eficiente e econômico da integridade do UCIe durante todas as fases do ciclo de vida do silício, o que é fundamental para a operação confiável de sistemas multi-die.

Recursos:

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoAiStream. Inteligência de Dados Web3. Conhecimento Amplificado. Acesse aqui.

- Cunhando o Futuro com Adryenn Ashley. Acesse aqui.

- Compre e venda ações em empresas PRE-IPO com PREIPO®. Acesse aqui.

- Fonte: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :tem

- :é

- :não

- :onde

- $UP

- 1

- 8

- a

- habilidade

- acelerar

- acelerado

- Acesso

- Alcançar

- alcançado

- Alcança

- em

- Adição

- Adicional

- Adiciona

- avançado

- Depois de

- Envelhecendo

- Todos os Produtos

- alocação

- permitir

- permite

- juntamente

- an

- analisar

- e

- aplicações

- abordagem

- SOMOS

- artigo

- AS

- aspecto

- aspectos

- montado

- Montagem

- assumiu

- At

- disponível

- evitando

- Largura de Banda

- baseado

- BE

- tornam-se

- antes

- ser

- Benefícios

- entre

- Pós

- Bloquear

- Blocos

- ambos

- Break

- pontes

- trazer

- construído

- construídas em

- by

- chamado

- CAN

- não podes

- casas

- casos

- cadeia

- correntes

- características

- verificado

- lasca

- Relógio

- Clocks

- mercadoria

- comum

- completar

- completamente

- integrações

- compreensivo

- conceito

- condições

- Configuração

- CONTATE-NOS

- Conexão de

- Coneções

- Conectividade

- constantemente

- controlador

- Custo

- relação custo-benefício

- poderia

- cobertura

- cobertura

- crio

- criado

- crítico

- dados,

- definido

- densidade

- desenhadores

- projetos

- detectou

- morrem

- diferente

- digital

- direção

- inválido

- dividido

- do

- down

- dois

- durante

- cada

- eficiente

- eliminado

- incorporado

- emergiu

- permitir

- permite

- permitindo

- termina

- aprimoramento

- garantir

- assegurando

- equipamento

- etc.

- Éter (ETH)

- Mesmo

- evoluiu

- exemplo

- execução

- apresentar

- existente

- esperado

- caro

- expresso

- estender

- extenso

- extra

- olho

- tecidos

- falso

- família

- RÁPIDO

- mais rápido

- defeituoso

- Funcionalidades

- campo

- final

- Primeiro nome

- Flash

- Flexibilidade

- seguinte

- Escolha

- formado

- da

- função

- funcional

- funcionalidade

- funções

- mais distante

- futuro

- colhido

- geradores

- Go

- Bom estado, com sinais de uso

- Grupo

- mão

- Ter

- Saúde

- saudável

- ajudar

- hierarquia

- Alta

- superior

- Contudo

- HTTPS

- identificar

- IEEE

- if

- Impacto

- implementação

- importante

- in

- incluir

- inclui

- Incluindo

- Crescimento

- aumentando

- indicam

- Individual

- indústria

- INFORMAÇÕES

- Infraestrutura

- insights

- instantâneos

- integração

- integridade

- Interface

- interfaces de

- interno

- interrompido

- para dentro

- IP

- IT

- se

- Chave

- conhecido

- Pista

- grande

- Escritórios de

- camadas

- Nível

- aproveita as

- aproveitando

- wifecycwe

- limitação

- LINK

- Links

- carregar

- lógica

- mais

- fora

- perdido

- Baixo

- moldadas

- a Principal

- manutenção

- mercado

- Match

- correspondente

- max-width

- Posso..

- medição

- mecanismo

- Memória

- Moda

- Monitore

- monitoração

- monitores

- Monolítico

- mais

- a maioria

- MTR

- múltiplo

- devo

- Perto

- Cria

- Novo

- não

- nó

- nós

- normal

- número

- of

- Oferece

- on

- ONE

- só

- operação

- otimização

- or

- Outros

- Fora

- lado de fora

- Superar

- pacote

- empacotado

- pacotes

- acondicionamento

- Paralelo

- parte

- particularmente

- passou

- caminho

- padrão

- padrões

- atuação

- permanente

- fase

- pins

- Passo

- platão

- Inteligência de Dados Platão

- PlatãoData

- possível

- possivelmente

- potencial

- potencialmente

- poder

- alimentado

- previsto

- anterior

- Prévio

- probabilidade

- problemas

- procedimentos

- processo

- em processamento

- Produto

- Produção

- protocolo

- fornecer

- fornece

- fornecendo

- qualidade

- Taxa

- Leia

- recentemente

- Recupera

- reduzir

- redução

- registradores

- confiabilidade

- confiável

- reparar

- requerer

- Requisitos

- resultando

- Risco

- roteamento

- Execute

- RX

- mesmo

- Salvar

- escalável

- dimensionamento

- agendamento

- seguro

- segmentos

- selecionado

- sensor

- Seqüência

- grave

- serve

- vários

- rede de apoio social

- lado

- Signal

- Assinaturas

- Silício

- SIM

- semelhante

- solteiro

- situações

- lento

- Retardando

- pequeno

- solução

- alguns

- vãos

- especializado

- específico

- velocidade

- estável

- padrão

- Estrela

- estado-da-arte

- Passo

- Passos

- armazenamento

- loja

- armazenadas

- Estratégia

- estruturada

- sucesso

- tal

- ajuda

- Apoiar

- .

- sistemas

- alvejando

- Tecnologias

- Equipar

- condições

- teste

- ensaio

- testes

- que

- A

- Eles

- então

- Lá.

- Este

- deles

- isto

- Através da

- tempo

- para

- topo

- pista

- tráfego

- transportando

- dois

- TX

- usb

- usar

- usava

- Utilizador

- utilização

- vário

- Verificação

- via

- foi

- Caminho..

- webp

- BEM

- O Quê

- quando

- qual

- enquanto

- precisarão

- com

- dentro

- sem

- o pior

- Produção

- zefirnet