A corrosão por plasma é talvez o processo mais essencial na fabricação de semicondutores e, possivelmente, a mais complexa de todas as operações fabris, depois da fotolitografia. Quase metade de todas as etapas fab dependem de um plasma, um gás ionizado energético, para fazer seu trabalho.

Apesar do transistor e das células de memória cada vez menores, os engenheiros continuam a fornecer processos de gravação confiáveis.

“Para criar chips de forma sustentável com precisão em nível de nanoescala e a estrutura de custos correta, os fabricantes de equipamentos para fabricação de wafer precisam ultrapassar os limites da física de plasma, engenharia de materiais e ciência de dados para fornecer as soluções de equipamentos necessárias”, disse Thomas Bondur, vice-presidente corporativo de Marketing do grupo de produtos Etch em Lam Research. Em nenhum lugar isso é mais evidente do que na gravação de plasma, que trabalha lado a lado com a litografia para criar características exatas e repetíveis em wafers.

Este relatório examina as principais etapas de gravação em NAND 3D, DRAM, FETs de nanofolhas e interconexões, com uma visão avançada de dispositivos 2D e processamento de back-end de baixo orçamento. A indústria também está buscando produtos químicos de corrosão mais sustentáveis para reduzir o CO equivalente2 emissões de suas fábricas.

Para muitos fabricantes de ferramentas, a modelagem do processo desempenha um papel fundamental no desenvolvimento do processo de corrosão. O objetivo é reduzir o tempo de lançamento no mercado e, ao mesmo tempo, reduzir os custos de wafer e máscara.

“A otimização do processo de gravação em algumas das etapas mais complicadas pode levar um ano ou mais para ser concluída”, disse Barrett Finch, diretor sênior de marketing da Lam Research. “Recentemente, concluímos um trabalho de simulação de processo em três semanas, que deveria levar três meses usando testes e desenvolvimento típicos baseados em silício.”

Isso pode chegar a centenas de milhares, ou mesmo milhões de dólares, apenas para os custos de máscara e wafer de um fabricante de dispositivos.

Noções básicas de gravação

O processo de gravação funciona de mãos dadas com a litografia. A corrosão normalmente é precedida pela deposição de um filme (por epitaxia, deposição química ou física de vapor, etc.). Normalmente, um CVD filme é revestido com fotorresistente e, em seguida, exposto através de um padrão retículo (máscara) usando litografia óptica (248 nm ou 193 nm UV, 13.5 nm EUV). Resistir ao desenvolvimento então revela o padrão. Em uma única câmara de gravação de plasma de wafer, normalmente os produtos químicos e íons de gravação bombardeiam e removem o filme CVD onde o fotorresiste está faltando (em resistência de tom positivo). Após a corrosão, resista à cinza, limpeza química úmida e/ou corrosão úmida remova os resíduos.

Os processos de gravação por plasma podem ser agrupados grosseiramente como dielétricos, silício ou condutores. Dielétricos como dióxido de silício e nitreto de silício são melhor gravados usando gases fluorados, enquanto camadas de silício e metal reagem melhor com produtos químicos de cloro. Existem essencialmente três modos de corrosão seca — corrosão por íons reativos, corrosão por plasma e corrosão por pulverização (feixe de íons). Os processos de corrosão são todos sobre as interações complexas entre os reagentes químicos, plasma e materiais de bolacha. Quando a polarização de RF é aplicada a um gás reativo, elétrons e íons carregados positivamente bombardeiam o wafer para remover fisicamente (gravar) o material, enquanto as espécies químicas e os radicais livres reagem com o material exposto para formar subprodutos voláteis. A corrosão pode ser isotrópica (reagindo igualmente vertical e horizontalmente), anisotrópica (somente vertical) ou em algum lugar intermediário.

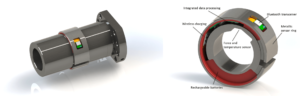

Fig. 1: A transição de finFET para GAA conduz os requisitos críticos de gravação seletiva isotrópica. Fonte: Lam Research

As métricas com as quais os engenheiros de gravação mais se preocupam são taxa de gravação, controle de perfil, uniformidade (através do wafer) e seletividade de gravação, porque afetam o rendimento e a produtividade. A seletividade de corrosão é simplesmente a taxa de remoção do material que você deseja gravar em relação à sua camada inferior - por exemplo, SiO2 em silício. Durante a corrosão, também é vantajoso não remover muito fotorresistente. Mas, quando esse é o caso, muitas vezes o padrão é transferido para uma máscara rígida (dióxido de silício, nitreto de silício, SiOC, TiN) antes de ser transferido para o filme subjacente.

As especificações de seletividade variam de 2:1 até 1,000:1 (gravação altamente seletiva). A cada novo nó, essas especificações ficam mais rígidas. “Com o EUV de alto NA começando a substituir o EUV regular nos próximos quatro anos, o foco é muito menor, então você não pode mais expor fotorresistente espesso – e por espesso quero dizer 30 nanômetros”, disse Philippe Bézard, engenheiro de pesquisa e desenvolvimento de corrosão seca da imec. “Mas você ainda precisa padronizar a mesma espessura de filme abaixo. Portanto, agora você está pedindo uma seletividade muito maior no sentido de que, em vez de 2:1, temos que atingir mais de 10:1, o que é uma melhoria repentina de seletividade de 4 a 5 vezes.”

Da prova de conceito (POC) à fabricação de alto volume (HVM)

Bézard descreve três fases do desenvolvimento do processo de gravação:

- Determinar quais agentes corrosivos, gases, camadas auxiliares, etc., são necessários para realizar a corrosão;

- Demonstrar desempenho na remoção total do filme dentro das especificações com uniformidade de processo em um wafer e

- Determinar como o processo pode ser repetido em milhares de wafers em HVM com alto rendimento e pouco desvio.

Normalmente, engenheiros qualificados de gravação e integração lidam com as duas primeiras fases do desenvolvimento. A terceira fase pode novamente utilizar conhecimentos de engenharia, mas o aprendizado de máquina pode ajudar.

“O aprendizado de máquina e a análise de dados em geral só são úteis na terceira fase”, disse ele. “É muito poderoso porque tem acesso a uma tonelada de dados e pode dar sentido a um milhão de pequenas coisas simples que estão interagindo. Então, para um cérebro humano tentar descobrir isso é muito difícil, mas é mais gerenciável para um programa de computador. Mas nos casos em que você tem uma nova aplicação, um novo material sendo gravado ou uma nova integração, não mostra nenhuma melhoria em relação aos humanos.”

O uso de ML também se refere ao custo de fabricação porque milhares de wafers são usados na fase três — pelo menos uma ordem de grandeza maior do que os usados nas fases um e dois.

Barrett Finch, diretor sênior do Etch Product Group na Lam Research, descreve o novo pathfinding do processo como obter uma prova de conceito de um fluxo nominal de processo e layout e desenvolver um ou mais dispositivos de trabalho em um wafer. Este POC é então transferido para uma equipe de desenvolvimento de produto na fábrica para ampliar o processo e melhorar o rendimento.

“A quantidade de trabalho necessária para transformar uma prova de conceito nominal em um produto de rendimento viável é frequentemente subestimada e isso cria uma grande lacuna na lucratividade”, disse Finch. “A modelagem de janela de processo procura fechar essa lacuna, introduzindo variação fab nos estágios iniciais de descoberta de caminhos de P&D.” Ele sugere que DOEs virtuais e análises baseadas em Monte Carlo em vários parâmetros de processo testam um POC simulando a variabilidade esperada.

“A modelagem da janela do processo pode responder à pergunta: 'Qual CD ou nível de variabilidade devo manter para atingir o desempenho e o rendimento mínimos do dispositivo?' Concluímos testes de janela de processo virtual com mais de 1 milhão de wafers virtuais em poucos dias, o que seria impossível de realizar na vida real”, disse ele.

Vários parâmetros afetam a taxa de corrosão, perfil e seletividade. Uma chave é a temperatura. “O impacto dos efeitos térmicos no processamento de corrosão é visto por nossos clientes, pois eles controlam as taxas de corrosão, seletividades e perfis corroídos. Todos esses parâmetros podem afetar o rendimento do dispositivo e a produtividade da fábrica”, disse Benjamin Vincent, gerente sênior de processo de semicondutores e engenharia de integração da Lam Research. Ele afirma que a simulação pode ser especialmente útil quando uma etapa do processo tem várias configurações possíveis (o espaço do processo é grande) ou quando os resultados a jusante da etapa são altamente imprevisíveis.

“O processo de gravação depende da temperatura da superfície do wafer, que depende de vários fluxos de calor – incluindo condução térmica, energias de impacto de íons, reações de superfície e fluxos de calor radiativo de plasma”, disse Alex Guermouche, gerente de marketing de produto da Esgee Technologies, uma Empresa de Pesquisa Lam. “Como resultado, os modelos de plasma precisam incorporar todos esses recursos físicos para representar com precisão as mudanças de temperatura na superfície do wafer. O software de simulação de processo pode modelar uma variedade de atributos de gravação, permitindo-nos obter um resultado de gravação melhor mais rapidamente e acelerar a capacidade do cliente de aumentar a produção ou otimizar o rendimento.”

Temporização precisa do processo de gravação

Com geometrias mais compactas e filmes mais finos, é necessário equilibrar a taxa de corrosão com grande controle sobre outros parâmetros operacionais.

“Com a redução das regras de design, muitos processos de corrosão estão se movendo para etapas de processo de gravação de plasma muito rápidas que exigem controle altamente preciso de todas as entradas de reação: energia, pressão, química e temperatura”, disse Finch, observando que também há uma tendência para plasma otimizado comportamento pulsante para gerar uma proporção específica de íon para neutro e, em seguida, varrer os subprodutos. “A modelagem avançada de tais condições será fundamental para permitir maior dimensionamento do dispositivo.”

Os fabricantes de sistemas de gravação vêm usando software de modelagem há algum tempo para acelerar o desenvolvimento do próximo nó ou aumentar os rendimentos. Isso não é surpresa, dada a complexidade do processo e todas as suas variáveis.

“Simplesmente não há tempo ou wafers suficientes para executar todos os experimentos de processo possíveis ao desenvolver tecnologias de próximo nó”, disse Finch. “O número de combinações de configurações de equipamentos de gravação pode chegar a milhões, ou mesmo bilhões, e o desenvolvimento de wafer de força bruta usando todas as possibilidades de processo é simplesmente impossível.”

Claro, todos os bons modelos são verificados em chips reais. “Um modelo preciso deve ser preditivo e deve resolver o problema-alvo que um usuário deseja resolver”, disse Finch. “Cada vez que uma mudança de processo ou projeto é recomendada com base no trabalho de simulação, os dados reais da fábrica devem refletir os resultados da recomendação. No nosso caso, conseguimos prever com precisão o efeito das mudanças no processo usando resultados baseados em modelos e resolver rapidamente problemas difíceis de desenvolvimento de processo e tecnologia.”

Os fornecedores de ferramentas também estão trabalhando em processos avançados de gravação para integrar linhas mais estreitamente e transformar o que antes era um processo de nível de duas máscaras (duas etapas de litografia) em um para simplificação do processo e redução de custos.

“Em vez de adaptar o hardware existente para tornar o canivete suíço ainda mais equipado, as empresas estão introduzindo tecnologias que são específicas da aplicação, como novos sistemas para resolver problemas de ponta a ponta”, disse Bézard. O objetivo é aproximar duas linhas voltadas uma para a outra, o que atualmente envolve uma etapa de padronização de linhas seguida de uma máscara de corte. “O que a Applied Materials e outros estão introduzindo é uma maneira de gravar diretamente na direção horizontal.” Tais processos também podem se alargar através de orifícios.

Etapas de gravação para FETs de nanofolhas

As etapas de gravação mais críticas em nanofolha os fluxos do processo incluem a gravação do portão fictício, gravação do pilar anisotrópico, gravação do espaçador isotrópico e a etapa de liberação do canal. [1] A gravação do perfil através de camadas alternadas de silício e SiGe é anisotrópica e usa química fluorada. A gravação do espaçador interno (indentação) e a etapa de liberação do canal são otimizadas para remover o SiGe com perda de silício extremamente baixa.

A etapa de liberação do canal é crítica. “O lançamento da nanofolha exige uma seletividade extremamente alta”, disse Bézard. “A maioria das nanofolhas são de silício, depois silício-germânio e silício. Você tem camadas alternadas e precisa remover uma sem modificar a outra”. Algumas publicações discutiram a realização de um ataque de SiGe em várias etapas para reduzir o estresse na estrutura induzido por uma única etapa de ataque.

A seguir no processo está a formação de contatos auto-alinhados. “Aqui, o que estamos tentando fazer é basicamente gravar dióxido de silício e não tocar ou recuar o nitreto de silício. As especificações atuais são, digamos, 3 nm de recesso, mas as pessoas estão pedindo perda zero”, disse Bézard. “Neste caso nem estamos usando a palavra seletividade. Nós apenas falamos sobre recesso – e zero recesso nisso.”

3D NAND

Escolha 3D NAND flash, o número de camadas continua a crescer e exige a adoção de várias camadas empilhadas no futuro, eventualmente criando sequências verticais de dispositivos empilhados. “Além disso, há muito esforço para dimensionar o pitch da linha de palavras ou vertical/Z-pitch das camadas à medida que o número de camadas aumenta para continuar aumentando a densidade de bits”, disse Robert Clark, membro sênior da equipe técnica e diretor de tecnologia na TEL. “Do ponto de vista do processo, os processos de corrosão e deposição precisarão de melhorias constantes para acomodar as proporções cada vez mais altas em dimensões críticas cada vez menores que o dimensionamento contínuo exige.”

Clark descreveu mudanças futuras. “Olhando para nós avançados de dispositivos de armadilha de carga com vários níveis, a engenharia das pilhas de portas será necessária para atingir comprimentos de porta mais curtos, mais níveis por célula e eficiência de programação aprimorada – potencialmente através da adoção de materiais de alto k. Canais de condutividade mais alta provavelmente também serão necessários para substituir os canais poli-Si no futuro”, disse ele.

Uma das gravações mais críticas em NAND 3D envolve a gravação profunda de orifícios de cerca de 100 nm através de pilhas de nitreto de óxido multicamadas (mais de 200 camadas), que podem ter até 10 µm de profundidade. Bézard, da Imec, disse que essa etapa de gravação é particularmente cara.

“Temos um fenômeno físico que ocorre, chamado efeito de carregamento diferencial”, disse ele. “No plasma temos elétrons, íons e espécies neutras para simplificar bastante. Os elétrons se movem em todas as direções, mas os íons são acelerados perpendicularmente à superfície. Então você tem carga positiva no fundo do buraco e cargas negativas no topo, e você obtém um campo elétrico que está tentando repelir os íons que chegam.”

Como resultado, são necessários altos níveis de potência para gravar totalmente a trincheira. “Estamos tentando sustentar de 30 a 50 gigawatts de potência sem arco elétrico e, portanto, o mandril deve ser extremamente bem polido e bem fabricado”, disse ele.

As gravações profundas também induzem tensões que precisam ser minimizadas, especialmente porque a fabricação de NAND multicamadas subsequentemente requer afinamento de wafer, alinhamento preciso e ligação híbrida para a próxima camada.

Outros processos

Nem todos os fabricantes de chips produzem chips de ponta que requerem litografia EUV. Muitas fábricas estão estendendo seus processos de litografia e gravação de 193nm.

“Temos um material SOC de alta temperatura que começamos a introduzir recentemente, que estende sua capacidade de padronização e pode suportar temperaturas mais altas, seja usado como subcamada para uma camada CVD ou máscara”, disse Brian Wilbur, diretor de diversificação de produtos semicondutores da Ciência cervejeira.

beol para as linhas de metal mais estreitas, espera-se que passe por uma transição dramática de esquemas de integração de damasceno duplo para deposição subtrativa e corrosão de interconexão diferente de cobre. Aqui, dois metais - rutênio e molibdênio - foram os mais desenvolvidos. No entanto, o molibdênio tem maior probabilidade de oxidar durante a corrosão, tornando-o mais compatível com esquemas damascenos duplos. O rutênio é um metal nobre, por isso não apresenta os mesmos problemas de corrosão, mas é mais caro.

As estruturas dos dispositivos também estão se tornando intolerantes a erros de posicionamento de borda. Novos esquemas de auto-alinhamento de camada para camada e entre vias e linhas serão necessários, de acordo com Clark da TEL. “As primeiras implementações provavelmente serão para coisas como linhas de palavras enterradas em DRAM e as camadas de metal MOL de pequeno passo para lógica onde há necessidade de maior estabilidade térmica, bem como menor resistividade ou metais sem revestimento”.

Desenvolvimentos de próxima geração

A longo prazo, o setor idealmente fará a transição para processos de back-end de orçamento térmico mais baixo (mais próximo de 300°C do que de 400°C) para integrar dispositivos em camadas de interconexão de back-end.

“A indústria tem uma necessidade real de começar a construir dispositivos em mais camadas”, disse Clark da TEL. “Isso significa que precisamos de memória e dispositivos lógicos construídos dentro dos orçamentos térmicos BEOL at BEOL.”

Até agora, os dispositivos feitos com óxidos semicondutores parecem promissores, tanto para integrar dispositivos de memória em um fluxo lógico BEOL quanto para construir matrizes CMOS no topo da matriz de memória em DRAMs.

Outra mudança substancial envolve a integração de materiais 2D, que as casas de pesquisa e os principais fabricantes de chips já estão começando a testar. Processos de corrosão para materiais como dissulfeto de tungstênio ou dissulfeto de molibdênio estão sendo considerados. Os filmes consistem em uma monocamada de material, portanto, desenvolver processos fabulosos para integrá-los é extremamente desafiador.

Sustentabilidade

Fabricantes de chips e fornecedores de materiais estão buscando produtos químicos alternativos para reduzir as emissões de carbono. Na corrosão, os principais culpados são os gases fluorados com alto potencial de aquecimento global.

“Uma razão pela qual você tem PFOS (ácido perfluorooctano sulfônico), que é problemático, é porque a molécula é muito estável”, disse Bézard do imec. “A luz ou as reações químicas na atmosfera não são suficientes para quebrá-lo.”

Ele disse que várias misturas alternativas de gás com maior teor de oxigênio são mais facilmente dissociadas e têm menor GWP. “No entanto, qualquer candidato precisa apresentar um desempenho tão bom ou até superior para começar.”

Mas a sustentabilidade não é particularmente um desafio de corrosão ou deposição. É um desafio holístico da indústria, desde a litografia até a embalagem, onde o impacto de um novo material influencia todo o processamento do dispositivo.

Referência

1.K.Derbyshire, “O que há de diferente nos transistores de última geração”, Engenharia de semicondutores, 20 de outubro de 2022.

Histórias relacionadas

Etch altamente seletivo é lançado para chips de última geração

A fabricação de estruturas 3D exigirá controle em nível atômico do que é removido e do que permanece em um wafer.

- Conteúdo com tecnologia de SEO e distribuição de relações públicas. Seja amplificado hoje.

- PlatoAiStream. Inteligência de Dados Web3. Conhecimento Amplificado. Acesse aqui.

- Cunhando o Futuro com Adryenn Ashley. Acesse aqui.

- Compre e venda ações em empresas PRE-IPO com PREIPO®. Acesse aqui.

- Fonte: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :tem

- :é

- :não

- :onde

- $UP

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- Materiais 2D

- 30

- 3d

- 50

- a

- habilidade

- Capaz

- Sobre

- acelerar

- acelerado

- Acesso

- acomodar

- realizar

- Segundo

- preciso

- exatamente

- em

- real

- endereço

- Adoção

- avançado

- vantajoso

- afetar

- novamente

- visar

- alex

- Todos os Produtos

- Permitindo

- já

- tb

- alternativa

- quantidade

- an

- análise

- e

- Outro

- responder

- qualquer

- aparecer

- Aplicação

- específico do aplicativo

- aplicado

- SOMOS

- Exército

- Ordem

- AS

- aspecto

- auxiliar

- At

- Atmosfera

- atributos

- longe

- Back-end

- Equilíbrio

- baseado

- Basicamente

- BE

- viga

- Porque

- tornando-se

- sido

- antes

- Começo

- ser

- abaixo

- Benjamin

- MELHOR

- Melhor

- entre

- viés

- Grande

- bilhões

- Pouco

- ambos

- Inferior

- limites

- Cérebro

- Break

- Brian

- força bruta

- orçamento

- Orçamentos

- Prédio

- construído

- mas a

- by

- chamado

- CAN

- candidato

- carbono

- as emissões de carbono

- Cuidado

- casas

- casos

- CD

- Células

- desafiar

- desafiante

- Câmara

- alterar

- Alterações

- Canal

- canais

- carregar

- carregada

- acusações

- cobrando

- químico

- produtos químicos

- química

- Chips

- Limpeza

- Fechar

- de perto

- mais próximo

- combinações

- Empresas

- Empresa

- compatível

- completar

- Efetuado

- integrações

- complexidade

- computador

- conceito

- condições

- condutividade

- condutor

- considerado

- constante

- contatos

- conteúdo

- continuar

- continuou

- continua

- ao controle

- Cobre

- Responsabilidade

- corrosão

- Custo

- redução de custos

- custos

- poderia

- curso

- crio

- cria

- Criar

- crítico

- Atual

- Atualmente

- Clientes

- Cortar

- dados,

- análise de dados

- ciência de dados

- dias

- profundo

- entregar

- densidade

- depende

- descrito

- Design

- desenvolvido

- em desenvolvimento

- Desenvolvimento

- dispositivo

- Dispositivos/Instrumentos

- diferente

- difícil

- dimensões

- direção

- diretamente

- Diretor

- discutido

- diversificação

- do

- parece

- dólares

- down

- dramaticamente

- distância

- secar

- durante

- cada

- Cedo

- facilmente

- efeito

- efeitos

- eficiência

- ou

- Elétrico

- elétrons

- emissões

- permitindo

- engenheiro

- Engenharia

- Engenheiros

- suficiente

- igualmente

- equipamento

- equipado

- Equivalente

- especialmente

- essencial

- essencialmente

- etc.

- Mesmo

- eventualmente

- Cada

- exigente

- Examina

- executar

- existente

- esperado

- caro

- experimentos

- experiência

- exposto

- estendendo

- extremamente

- enfrentando

- longe

- RÁPIDO

- mais rápido

- Funcionalidades

- poucos

- campo

- Figura

- Filme

- filmes

- Primeiro nome

- Flash

- fluxo

- Fluxos

- Foco

- seguido

- seguinte

- Escolha

- força

- formulário

- treinamento

- para a frente

- quatro

- Gratuito

- da

- totalmente

- mais distante

- futuro

- lacuna

- GAS

- Geral

- gerar

- ter

- dado

- Global

- aquecimento global

- meta

- Bom estado, com sinais de uso

- ótimo

- Grupo

- Cresça:

- Cresce

- Metade

- manipular

- Queijos duros

- Hardware

- Ter

- he

- útil

- SUA PARTICIPAÇÃO FAZ A DIFERENÇA

- Alta

- Alto rendimento

- superior

- altamente

- Buraco

- Buracos

- holística

- Horizontal

- casas

- Como funciona o dobrador de carta de canal

- Contudo

- HTTPS

- humano

- Humanos

- Centenas

- HÍBRIDO

- i

- Impacto

- impossível

- melhorar

- melhorado

- melhoria

- in

- incluir

- Incluindo

- Entrada

- incorporar

- aumentando

- indústria

- inputs

- instância

- em vez disso

- integrar

- Integração

- integração

- interagindo

- interações

- interliga

- para dentro

- introduzindo

- questões

- IT

- ESTÁ

- jpg

- apenas por

- Chave

- Fuga

- grande

- Maior

- camada

- camadas

- traçado

- principal

- aprendizagem

- mínimo

- Nível

- níveis

- vida

- como

- Provável

- Line

- linhas

- LITO

- pequeno

- lógica

- mais

- olhar

- fora

- lote

- Baixo

- máquina

- aprendizado de máquina

- moldadas

- a Principal

- a manter

- fazer

- Makers

- Fazendo

- Gerente

- fabricado

- Fabricante

- fabrica

- muitos

- mercado

- Marketing

- Diretor de Marketing

- máscara

- material

- materiais

- max-width

- Posso..

- significar

- significa

- membro

- Memória

- metal

- Metais

- Métrica

- poder

- milhão

- milhões

- mínimo

- desaparecido

- modelo

- modelagem

- modelos

- modos

- MOL

- molécula

- mês

- mais

- a maioria

- mover

- em movimento

- muito

- múltiplo

- quase

- você merece...

- necessário

- Cria

- negativo

- Neutro

- Novo

- Próximo

- não

- Nobre

- nó

- nós

- agora

- número

- Outubro

- of

- frequentemente

- on

- uma vez

- ONE

- só

- operando

- Operações

- otimização

- Otimize

- otimizado

- or

- ordem

- Outros

- Outros

- A Nossa

- Fora

- Acima de

- Oxygen

- acondicionamento

- parâmetros

- particular

- particularmente

- padrão

- Pessoas

- realizar

- atuação

- realização

- possivelmente

- perspectiva

- fase

- fenómeno

- Philippe

- físico

- Fisicamente

- Física

- Pilar

- Passo

- essencial

- Plasma

- platão

- Inteligência de Dados Platão

- PlatãoData

- desempenha

- PoC

- positivo

- possibilidades

- possível

- possivelmente

- potencial

- potencialmente

- poder

- poderoso

- preciso

- Precisão

- predizer

- presidente

- pressão

- Problema

- problemas

- processo

- processos

- em processamento

- produzir

- Produto

- desenvolvimento de produtos

- Produção

- produtividade

- Produtos

- Perfil

- Perfis

- rentabilidade

- Agenda

- Programação

- promissor

- prova

- prova de conceito

- publicações

- Empurrar

- questão

- rapidamente

- R & D

- Rampa

- alcance

- Taxa

- Preços

- relação

- alcançar

- Reagir

- reação

- reações

- reais

- vida real

- razão

- recentemente

- Recomendação

- Recomenda

- reduzir

- redução

- redução

- refletir

- regular

- liberar

- confiável

- depender

- remoção

- remover

- Removido

- removendo

- Repetivel

- repetido

- substituir

- Denunciar

- requerer

- requeridos

- Requisitos

- exige

- pesquisa

- resultar

- Resultados

- revela

- certo

- ROBERT

- Tipo

- rolos

- grosseiramente

- regras

- Execute

- Dito

- mesmo

- dizer

- Escala

- dimensionamento

- esquemas

- Ciência

- Procura

- visto

- seletivo

- Semicondutor

- senior

- sentido

- contexto

- vários

- mudança

- rede de apoio social

- Silício

- simples

- simplificar

- simplesmente

- simulação

- solteiro

- hábil

- pequeno

- So

- Software

- Soluções

- RESOLVER

- alguns

- algum lugar

- fonte

- Espaço

- específico

- especificações

- óculos

- velocidade

- Estabilidade

- estável

- empilhado

- Pilhas

- Staff

- Estágio

- começo

- começado

- Passo

- Passos

- Ainda

- estresse

- estrutura

- Subseqüentemente

- substancial

- tal

- súbito

- suficiente

- Sugere

- fornecedores

- superfície

- surpresa

- Sustentabilidade

- sustentável

- Varrer

- suíço

- sistemas

- Tire

- tomar

- Converse

- visadas

- Profissionais

- Dados Técnicos:

- Tecnologias

- Equipar

- Desenvolvimento Tecnológico

- prazo

- teste

- ensaio

- testes

- do que

- que

- A

- O Futuro

- deles

- Eles

- então

- Lá.

- térmico

- Este

- deles

- coisas

- Terceiro

- isto

- completamente

- milhares

- três

- Através da

- camada

- mais apertado

- tempo

- cronometragem

- para

- juntos

- Tom

- TOM

- também

- topo

- tocar

- para

- transferido

- Transformar

- transição

- Trend

- tentar

- dois

- típico

- tipicamente

- subjacente

- imprevisível

- sobre

- para cima

- us

- usar

- usava

- Utilizador

- utilização

- utilizar

- verificado

- vertical

- verticalmente

- muito

- via

- viável

- Vice-Presidente

- vincent

- Virtual

- volátil

- queremos

- quer

- foi

- Caminho..

- we

- semanas

- BEM

- O Quê

- quando

- se

- qual

- enquanto

- inteiro

- porque

- precisarão

- de

- dentro

- sem

- Word

- Atividades:

- trabalhar

- trabalho

- seria

- ano

- anos

- Produção

- produzindo

- rendimentos

- Você

- zefirnet

- zero