S2C jest światowym liderem w prototypowaniu FPGA od prawie dwudziestu lat, a jej platformy prototypowania FPGA dokładnie śledzą dostępność najnowszych układów FPGA – w tym najnowszych układów FPGA firm Xilinx i Intel. I zdecydowanie wywiązują się z obietnicy, że udoskonalą swoje rozwiązania w zakresie prototypowania w zakresie prototypowania projektów w skali hiperskalowej – skalowanie prototypowanie wydajności i możliwości platformy w celu obsługi wielomiliardowych projektów bramek.

Patrząc wstecz na początek czwartego kwartału 4 r., firma S2020C ogłosiła wsparcie dla nowych wówczas układów FPGA Xilinx VU2P UltraScale+, oferujących pojedyncze, podwójne i poczwórne platformy prototypowania FPGA. Następnie, w grudniu 19 r., firma S2020C ogłosiła rodzinę platform prototypowych Prodigy Logic Matrix o dużej gęstości, z 2 układami FPGA na Logic Matrix, 8 Logic Matrix na pojedynczą szafę serwerową (8 układy FPGA) i możliwością połączenia wielu szafy serwerowe razem. Pierwsze wersje Logic Matrix zostały dostarczone z układami FPGA Xilinx VU64 (nazwanymi LX1) dla pierwszych klientów, którzy nie mogli się doczekać wersji VU19P (nazwanej LX2).

Teraz S2C udoskonala swoją grę Logic Matrix dzięki LX2, która zwiększa użyteczną pojemność bramy prototypowej o 60% w porównaniu z wersją VU440! Więcej użytecznych bramek na FPGA oznacza mniej FPGA, mniej połączeń FPGA i wyższą wydajność przy tym samym prototypowym projekcie. Przy szacunkowej przepustowości bramek wynoszącej 392 miliony bramek na LX2, w pełni wypełniona standardowa szafa serwerowa z 8 LX2 umożliwia szacunkową zdolność prototypowania ponad 3 miliardów bramek ASIC!

Rysunek 1: Matryca logiczna Prodigy LX2

| Rodzina macierzy logicznych Prodigy | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Szacowane bramki ASIC (M) | 240 | 392 |

| Liczba układów FPGA | 8 | 8 |

| Komórki logiczne systemu (K) | 44,328 | 71,504 |

| Pamięć FPGA (Mb) | 709 | 1,327.2 |

| Plasterki DSP | 23,040 | 30,720 |

| Zewnętrzne wejścia/wyjścia użytkownika | 9,216 | 10,368 |

| Transceivery SerDes | 384 GTH | 640 GTY |

| Złącza Prodigy | 64 | 72 |

| Złącza PGT | 8 | 0 |

| Złącza nadajnika-odbiornika | 80 MSAS każdy z 4 GTH + 8 IO | 160 MCIO każdy z 4 GTY + 8 IO |

| Wydajność SerDes | 16 Gbps | 28 Gbps |

Postać 2: Rodzina macierzy logicznych

Elastyczne, szybkie połączenia wzajemne są kluczem do prototypowania FPGA o dużej gęstości, a Logic Matrix obsługuje hierarchiczną, 3-poziomową strategię połączeń: Krótki Most do połączeń między sąsiednimi układami FPGA; SysLink do szerokopasmowych połączeń kablowych FPGA oraz TransLink dla połączeń FPGA SerDes na dłuższych dystansach za pośrednictwem kabli MCIO. Aby uprościć wzajemne połączenia FPGA i zmaksymalizować wartość TransLinkPrzepływ partycjonowania S2C obsługuje nowo wprowadzoną przez Xilinx technologię High-Speed Transceiver Pin Multiplexing (HSTPM), upraszczającą przesyłanie sygnału z dokładnością do cyklu, multipleksowanie pinów i łączność SerDes FPGA o niskim opóźnieniu.

Aby zminimalizować czas tworzenia prototypów i zmaksymalizować produktywność prototypowania, inne narzędzia S2C do zwiększania wydajności prototypowania zostały zaprojektowane z myślą o Logic Matrix, w tym Czas działania Player Pro oprogramowanie – i dodatkowe narzędzia do prototypowania S2C, w tym ProtoBridge, MDMProi S2C Protokół IP gotowy na prototyp.

Czas działania Player Pro oprogramowanie jest dołączone LX2, zapewniając wygodne funkcje, takie jak zaawansowane zarządzanie zegarem, zintegrowany autotest, automatyczne wykrywanie płytki, programowanie napięcia we/wy, wielokrotne pobieranie FPGA oraz zdalne monitorowanie systemu i zarządzanie. Dołączone jest także AXEVision, wbudowane narzędzie do debugowania AXI-over-Ethernet, które upraszcza zdalne debugowanie projektów związanych z AXI.

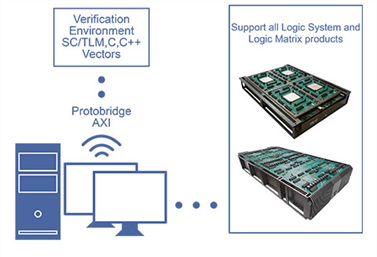

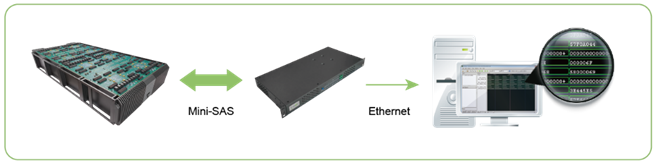

ProtoBridge obsługuje transfery danych o dużej przepustowości (do 1 GB/s) pomiędzy komputerem głównym a komputerem LX2 – umożliwienie przesyłania dużych ilości transakcji modelowanych programowo, strumieni wideo lub innych bodźców testowych w celu walidacji systemu.

Rysunek 3: ProtoBridge

MDMPro oferuje głębokie debugowanie śladów z wyzwalaniem krzyżowym dla maksymalnie ośmiu układów FPGA, przeglądanie śladów sygnałów wielu FPGA w jednym oknie podglądu, 64 GB zewnętrznej pamięci przebiegów śledzenia, częstotliwości próbkowania śladów do 125 MHz oraz obsługuje języki maszyny stanu wyzwalania w celu złożonego przechwytywania śladów wymagania.

Rysunek 4: MDM Pro

S2C oferuje również bogatą bibliotekę Protokół IP gotowy na prototyp dla LX2 – karty-córki typu plug-and-play – przyspieszające tworzenie środowiska prototypowego wokół prototypu FPGA.

Rysunek 5: Gotowe do prototypowania karty-córki IP

Matryca logiczna Prodigy LX2 jest już dostępny. Aby uzyskać więcej informacji, skontaktuj się z lokalnym przedstawicielem handlowym S2C lub odwiedź witrynę www.s2ceda.com.

Udostępnij ten post przez: Źródło: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Dodatek

- ogłosił

- Zapowiedź

- na około

- ASIC

- dostępność

- Miliard

- deska

- przewody

- Pojemność

- połączenie

- Łączność

- Klientów

- dane

- dostarczanie

- Wnętrze

- Wykrywanie

- dystans

- Wcześnie

- Środowisko

- członków Twojej rodziny

- Korzyści

- Figa

- i terminów, a

- pływ

- FPGA

- gra

- Bramy

- Globalne

- HTTPS

- Włącznie z

- Informacja

- Intel

- IP

- Klawisz

- Języki

- duży

- firmy

- Biblioteka

- miejscowy

- i konserwacjami

- Matrix

- milion

- monitorowanie

- oferuje

- Oferty

- Inne

- PC

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- Platforma

- Platformy

- Pro

- wydajność

- Narzędzia zwiększające wydajność

- Programowanie

- prototypowanie

- ceny

- wymagania

- sole

- powiększanie

- Tworzenie

- Rozwiązania

- Stan

- bodziec

- przechowywanie

- Strategia

- Strumienie

- wsparcie

- podpory

- system

- test

- transakcje

- wartość

- Wideo

- czekać

- KIM