Stare powiedzenie, że lekarstwo jest gorsze niż choroba, ma zastosowanie przy omawianiu MBIST dla dużych SOC, w których równoległe przeprowadzanie wielu testów MBIST może przekroczyć możliwości sieci dystrybucji energii (PDN). Wbudowany autotest pamięci (MBIST) zwykle uruchamia się automatycznie podczas zdarzeń włączania zasilania. Ze względu na chęć przyspieszenia czasu testów i rozruchu układu, testy te są często przeprowadzane równolegle. Problem polega na tym, że mogą z łatwością wytworzyć aktywność przełączania, która jest o rząd wielkości wyższa niż poziom występujący podczas normalnej pracy chipa. Rzeczywiście, te wyższe poziomy aktywności przełączania mogą nie tylko powodować spadek zasilania wpływający na wyniki testów, ale także wytwarzane ciepło może uszkodzić chipy. Efekty te mogą prowadzić do nieprawidłowego kategoryzowania lub bezpośrednich i ukrytych awarii zdarzeń.

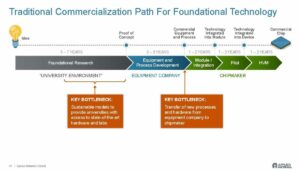

Rozwiązaniem jest symulacja aktywności MBIST w celu przewidywania obciążenia PDN i powiązanych efektów termicznych. Dysponując wynikami symulacji, projektanci mogą prawidłowo zdecydować, ile i które bloki pamięci mogą być testowane równolegle. Jednak nie zawsze jest to wykonalne w dużych SOC z wieloma blokami pamięci, ponieważ czasy symulacji mogą być wygórowane. Przy poziomie bramki i jeszcze mniej dokładnej symulacji RTL uruchomienie wystarczającej liczby cykli w celu uzyskania potrzebnych informacji może nie być możliwe.

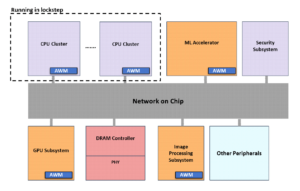

W białej księdze zatytułowanej „Analiza wpływu wykorzystania MBIST na moc” Siemens EDA analizuje, w jaki sposób projektanci mogą przeprowadzić wystarczającą symulację, aby podejmować świadome decyzje dotyczące strategii testowania przed wyłączeniem taśmy. Siemens współpracował z ARM nad jednym z ich chipów testowych, aby stworzyć przypadek testowy, w którym mogliby zastosować emulację sprzętową za pomocą aplikacji DFT i Power dla emulatora sprzętowego Siemens Veloce. Po pierwsze, aplikacja Veloce DFT jest używana do wyprowadzania wewnętrznej aktywności podczas emulacji MBIST. Aplikacja korzysta ze standardowego języka interfejsu testowego (STIL) i tworzy standardowe w branży pliki wyjściowe.

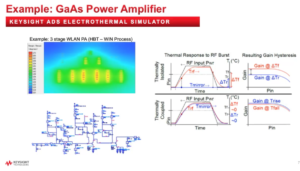

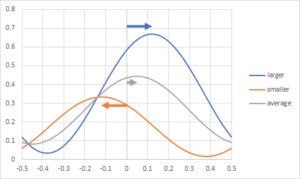

Aplikacja Veloce Power pobiera informacje o aktywności z przebiegów MBIST w celu generowania przebiegów, profili mocy i map ciepła, które mogą wskazywać, kiedy występują skoki mocy powyżej określonych limitów. Dzięki tym informacjom inżynierowie ds. testów mogą podejmować świadome decyzje dotyczące sekwencjonowania MBIST.

Przypadek testowy ARM opisany w białej księdze Siemensa zawiera 176 milionów bramek. W tym przypadku Siemens użył systemu Veloce z 6 płytkami Veloce Strato. Uruchomienie emulatora Veloce zajęło tylko 26 godzin, czyli 15,600 XNUMX razy szybciej niż symulacja poziomu bramki. Kolejną zaletą przepływu Veloce jest to, że informacje o aktywności są przesyłane strumieniowo przez aplikację Power do elektronarzędzi w przepływie, oszczędzając miejsce na dysku i czas. Wyniki z przypadku testowego wykazały kilka skoków mocy, które naruszyły specyfikacje projektowe SOC. Wyjście z aplikacji Veloce Power pokazuje całkowite poziomy mocy poprzez symulację wraz z oddzielnymi udziałami mocy dla zegara, logiki kombinacyjnej i pamięci. Podobnie jest informacja o tym, gdzie na kostce używana jest moc. Te informacje ułatwiają określenie, gdzie występują problemy.

Znalezienie takich problemów wymaga uruchomienia milionów lub miliardów cykli zegara. Ograniczenia symulatorów programowych uniemożliwiają przeprowadzenie niezbędnej analizy. Emulacja oferuje unikalną możliwość dokładnego zbadania wpływu MBIST na moc i innych operacji testowych na długo przed wprowadzeniem krzemu. Biała księga firmy Siemens oferuje wgląd w metodę zasilania stosowaną w prawdziwym przypadku testowym. Biała księga jest dostępna do pobrania do przeczytania na stronie internetowej firmy Siemens.

Udostępnij ten post przez: Źródło: https://semwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- O nas

- analiza

- Aplikacja

- mobilne i webowe

- ARM

- dostępny

- jest

- Spowodować

- żeton

- Frytki

- zegar

- zawiera

- mógłby

- lekarstwo

- Wnętrze

- choroba

- podczas

- z łatwością

- Inżynierowie

- wydarzenie

- wydarzenia

- szybciej

- i terminów, a

- pływ

- znaleziono

- Bramy

- Generować

- sprzęt komputerowy

- Wysoki

- W jaki sposób

- HTTPS

- przemysł

- Informacja

- IT

- język

- duży

- prowadzić

- poziom

- poziomy

- załadować

- długo

- Mapy

- milion

- miliony

- potrzebne

- sieć

- Oferty

- operacje

- zamówienie

- Inne

- Papier

- power

- Problem

- profile

- Czytający

- Efekt

- run

- bieganie

- oszczędność

- Siemens

- symulacja

- Tworzenie

- Typ przestrzeni

- prędkość

- Strategia

- strumieniowo

- Dostawa

- system

- test

- Testowanie

- Testy

- termiczny

- Przez

- czas

- narzędzia

- wyjątkowy

- zazwyczaj

- Strona internetowa

- biały papier

- pracował