Od czasu debiutu w latach 1980. XX w., kiedy to współdzielono sieci LAN o przepustowości 10 Mb/s za pośrednictwem kabli koncentrycznych, Ethernet odnotowuje ciągły postęp i obecnie może obsługiwać prędkości do 1.6 Tb/s. Postęp ten umożliwił Ethernetowi obsługę szerszego zakresu zastosowań, takich jak transmisja strumieniowa na żywo, sieci dostępu radiowego i sterowanie przemysłowe, podkreślając znaczenie niezawodnego przesyłania pakietów i jakości usług. Przy obecnej przepustowości Internetu wynoszącej ~500 Tb/s rośnie zapotrzebowanie na lepszą obsługę ruchu wewnątrz centrum danych zaplecza. Chociaż poszczególne serwery nie działają jeszcze z szybkością terabitów na sekundę, ogólny ruch w centrum danych zbliża się do tej skali, co skłoniło grupę IEEE 802.3dj do podjęcia wysiłków standaryzacyjnych i spowodowało konieczność stosowania solidnych kontrolerów Ethernet i SerDes do zarządzania rosnącym przepływem danych. W kontekście rosnących wymagań komunikacja międzyprocesorowa już osiąga tę prędkość.

Komunikacja międzyprocesorowa jest głównym czynnikiem zapotrzebowania na szybkość 1.6 T przy minimalnych opóźnieniach. Chociaż poszczególne urządzenia są ograniczone ze względu na ich nieodłączną zdolność przetwarzania i rozmiar chipa, połączenie chipów może znacznie zwiększyć te możliwości. Oczekuje się, że po pierwszej generacji aplikacji pojawią się połączenia typu switch-to-switch wewnątrz centrum danych, umożliwiające łączenie wysokowydajnych procesorów i pamięci, zwiększając skalowalność i wydajność przetwarzania w chmurze.

Inicjatywa IEEE 802.3dj: udoskonalanie standardów Ethernet w celu zapewnienia interoperacyjności z szybkością 1.6 Tb/s

Zgodność z ewoluującymi wysiłkami normalizacyjnymi ma kluczowe znaczenie dla płynnej interoperacyjności ekosystemów. Grupa IEEE 802.3dj jest w trakcie opracowywania nadchodzącego standardu Ethernet, który obejmie warstwy fizyczne i parametry zarządzania dla prędkości od 200G do 1.6 terabita na sekundę. Celem grupy jest szybkość transmisji danych w sieci Ethernet MAC na poziomie 1.6 Tb/s, a maksymalny współczynnik błędów bitowych nie przekracza 10–13 w warstwie MAC. Dalsze postanowienia obejmują opcjonalne 16- i 8-liniowe interfejsy jednostki przyłączeniowej (AUI), odpowiednie do różnych zastosowań chipów, wykorzystujące SerDes 112G i 224G. Fizycznie specyfikacja 1.6 Tb/s obejmuje transmisję za pośrednictwem 8 par miedzianych kabli typu twinax na dystansie do jednego metra i 8 par włókien światłowodowych na odległości od 500 metrów do 2 km. Chociaż pełną ratyfikację standardu zaplanowano na wiosnę 2026 r., oczekuje się, że zakończenie podstawowego zestawu funkcji nastąpi w 2024 r.

Narzut przepustowości i korekcja błędów w podsystemach Ethernet 1.6T

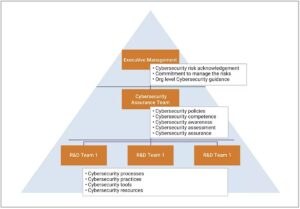

Rys. 1: Schemat przedstawiający elementy podsystemu Ethernet 1.6T.

We wcześniejszych iteracjach Ethernetu PCS skupiał się głównie na kodowaniu danych w celu niezawodnego wykrywania pakietów. Jednakże wraz ze wzrostem prędkości Ethernet do 1.6 T, potrzeba korekcji błędów w przód (FEC) staje się oczywista, szczególnie w celu przeciwdziałania degradacji sygnału nawet na krótkich łączach. W tym celu Ethernet 1.6T w dalszym ciągu wykorzystuje technologię Reed-Solomon FEC. Podejście to buduje słowo kodowe składające się z 514 10-bitowych symboli zakodowanych w 544 bloku symboli, co skutkuje 6% narzutem przepustowości. Te słowa kodowe FEC są rozprowadzane po łączach fizycznych AUI, tak że każde łącze fizyczne (8 w przypadku Ethernetu 1.6T) nie przenosi całego słowa kodowego. Ta metoda nie tylko zapewnia dodatkową ochronę przed seriami błędów, ale także umożliwia równoległość w dekoderze zdalnym, zmniejszając w ten sposób opóźnienie.

Przystawka do nośnika fizycznego (PMA) wyposażona w skrzynię biegów i SerDes doprowadza sygnał Ethernet do transmitowanych kanałów. W przypadku sieci Ethernet 1.6T oznacza to 8 kanałów, każdy działających z szybkością 212 Gb/s, co stanowi 6% narzutu FEC. Zastosowana technika modulacji to 4-poziomowa modulacja amplitudy impulsu (PAM-4), która koduje dwa bity danych dla każdego symbolu transmisji, skutecznie podwajając w ten sposób przepustowość w porównaniu z tradycyjnym podejściem zerowym bez powrotu (NRZ). Mechanizm transmisji opiera się na konwersji cyfrowo-analogowej, natomiast po stronie odbiorczej konwersja analogowo-cyfrowa w połączeniu z procesorami DSP zapewnia dokładną ekstrakcję sygnału.

Co więcej, należy zauważyć, że Ethernet PCS wprowadza „zewnętrzny FEC”, który rozciąga się od końca do końca łącza Ethernet. Aby wzmocnić kanały o większym zasięgu, w przygotowaniu jest dodatkowa warstwa korekcji błędów dla poszczególnych linii fizycznych, prawdopodobnie wykorzystująca kod Hamminga FEC. Oczekuje się, że korekcja ta znajdzie swoje główne zastosowanie w optycznych modułach nadawczo-odbiorczych, gdzie taka korekcja jest konieczna.

Ryc. 2: Diagram przedstawiający dodatkowy narzut dodany w przypadku użycia połączonego FEC w celu uzyskania większego zasięgu.

W przykładowym systemie przedstawionym na rysunku 2 MAC i PCS są połączone za pomocą modułu optycznego i odcinka światłowodu. PCS ma bitową stopę błędów wynoszącą 10-5 na łączu modułu optycznego oraz błędy z samego łącza optycznego. Użycie jedynego, kompleksowego złącza RS-FEC nie wystarczyłoby do osiągnięcia 10-13 standard Ethernet, co powoduje, że łącze jest zawodne. Opcją byłaby potrójna implementacja oddzielnego RS FEC na każdym przeskoku, co znacznie zwiększa koszty i opóźnienia. Bardziej skutecznym rozwiązaniem jest integracja połączonego kodu Hamminga FEC specjalnie dla łącza optycznego, uwzględniającego typowe błędy losowe połączeń optycznych. Ta wewnętrzna warstwa FEC zapewnia dodatkową ekspansję szybkości linii z 212 Gb/s do 226 Gb/s, dlatego istotne jest, aby SerDes mógł obsługiwać tę szybkość linii.

Wyzwania związane z opóźnieniami w systemach Ethernet 1.6T

Rys. 3: Ścieżka opóźnienia dla podsystemu Ethernet 1.6T.

Na opóźnienia w sieci Ethernet wpływają różne komponenty: kolejka transmisji, czas trwania transmisji, średni czas przejścia oraz kilka czasów przetwarzania i odbioru. Aby to sobie wyobrazić, rozważ rysunek 3, który przedstawia kompleksowy podsystem Ethernet 1.6T. Chociaż na opóźnienie może mieć wpływ czas reakcji aplikacji zdalnej, czynnik ten ma charakter zewnętrzny w stosunku do sieci Ethernet i dlatego często jest pomijany podczas analizy opóźnień. Minimalizowanie opóźnień w interfejsie Ethernet wymaga zrozumienia specyficznych okoliczności. Na przykład opóźnienie może nie być głównym problemem w przypadku połączeń trunkingowych między przełącznikami ze względu na nieodłączne opóźnienia na wolniejszych łączach klientów. Odległość również odgrywa rolę; większe długości powodują większe opóźnienia. Oczywiście nie oznacza to, że powinniśmy pomijać opóźnienia w innych scenariuszach. Zmniejszenie opóźnień jest zawsze celem.

Opóźnienie transmisji jest nieodłącznie powiązane z szybkością sieci Ethernet i rozmiarem ramki. W szczególności w przypadku systemu Ethernet 1.6 T przesyłanie pakietu o minimalnym rozmiarze wymaga czasu 0.4 ns – zasadniczo jednej ramki Ethernet na takt zegara 2.5 GHz. Z drugiej strony, transmisja standardowej ramki o maksymalnym rozmiarze zajmuje 8 ns, a w przypadku ramek Jumbo – 48 ns. Wybrane medium dodatkowo dyktuje opóźnienie. Na przykład światłowód zwykle charakteryzuje się opóźnieniem wynoszącym 5 ns na metr, podczas gdy okablowanie miedziane jest nieznacznie szybsze i wynosi 4 ns na metr.

Znaczna część całkowitego opóźnienia ma swoje źródło w kontrolerze odbiornika. Dekoder RS FEC z natury wprowadza opóźnienie. Aby rozpocząć korekcję błędów, system musi otrzymać 4 słowa kodowe, co przy 1.6 Tbps daje czas 12.8 ns. Późniejsze działania, w tym korekcja błędów i buforowanie, zwiększają to opóźnienie. Chociaż czas przechowywania słowa kodowego FEC pozostaje stały, opóźnienie podczas odbioru komunikatu zależy od konkretnej implementacji. Niemniej jednak opóźnienie można zoptymalizować, stosując skrupulatne strategie projektowania cyfrowego.

Zasadniczo występuje nieodłączne, nieuniknione opóźnienie wynikające z mechanizmu FEC i fizycznej odległości lub długości kabla. Poza tymi czynnikami kluczową rolę w minimalizowaniu opóźnień kontrolera Ethernet odgrywa wiedza specjalistyczna w zakresie projektowania. Wykorzystanie kompletnego rozwiązania, które integruje i optymalizuje MAC, PCS i PHY, toruje drogę do najbardziej wydajnej implementacji z niskimi opóźnieniami.

Podsumowanie

Ryc. 4: Sukces krzemu pierwszego przejścia dla Synopsys 224G Ethernet PHY IP w procesie 3 nm, przedstawiający wysoce liniowe oczy PAM-4.

Ethernet 1.6 Tb/s jest dostosowany do zastosowań wymagających największej przepustowości i wrażliwych na opóźnienia. Wraz z pojawieniem się technologii 224G SerDes, w połączeniu z postępem w MAC i PCS IP, dostępne są obecnie kompleksowe rozwiązania, które stale odpowiadają zmieniającym się standardom Ethernet 1.6T. Dodatkowo, ze względu na opóźnienia nieodłącznie związane z protokołem i metodami korekcji błędów, cyfrowe i analogowe projekty IP muszą być starannie opracowane przez doświadczonych projektantów, aby uniknąć wprowadzenia niepotrzebnych opóźnień do ścieżki danych.

Osiągnięcie najwyższej wydajności w projektach SoC 1.6T wymaga skutecznie zoptymalizowanej architektury i skrupulatnych praktyk projektowych dla każdego komponentu chipa. Podkreśla to oszczędność energii i minimalizuje ślad krzemowy, dzięki czemu szybkość transmisji danych 1.6 T staje się rzeczywistością. Sprawdzony przez krzem Synopsys 224G Ethernet PHY IP przygotował grunt dla kontrolera 1.6T MAC i PCS. Wykorzystując najnowocześniejsze techniki projektowania, analizy, symulacji i pomiarów, Synopsys w dalszym ciągu zapewnia wyjątkową integralność sygnału i wydajność jittera, z kompletne rozwiązanie Ethernet obejmujące MAC+PCS+PHY.

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :ma

- :Jest

- :nie

- :Gdzie

- $W GÓRĘ

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- dostęp

- dostępny

- Księgowość

- dokładny

- Osiągać

- w poprzek

- zajęcia

- w dodatku

- Dodatkowy

- do tego

- Przyjęcie

- postępy

- postęp

- przed

- Cel

- dozwolony

- już

- również

- Chociaż

- zawsze

- wśród

- kwoty

- wzmacniać

- an

- analiza

- i

- Przewiduje

- Zastosowanie

- aplikacje

- podejście

- architektura

- SĄ

- AS

- At

- uniknąć

- Back-end

- zasłona

- przepustowość

- BE

- staje się

- pomiędzy

- Poza

- Bit

- Blokować

- grzbiet

- pobudzanie

- Przynosi

- Buduje

- ale

- by

- kabel

- przewody

- CAN

- zdolności

- nieść

- wyzwania

- kanały

- żeton

- Frytki

- wybrany

- okoliczności

- klient

- zegar

- Chmura

- cloud computing

- kod

- połączony

- łączenie

- Komunikacja

- kompletny

- ukończenia

- składnik

- składniki

- wszechstronny

- obejmujący

- computing

- Troska

- spójnik

- połączony

- połączenia

- OCHRONA

- Rozważać

- Rozważania

- zgodny

- ciągły

- bez przerwy

- przyczynić się

- kontrola

- kontroler

- Konwersja

- Miedź

- rdzeń

- Koszty:

- przeciwdziałać

- kurs

- wykonane

- tworzy

- Aktualny

- dane

- Datacenter

- debiut

- opóźnienia

- dostarczyć

- Kreowanie

- wymagający

- wymagania

- przedstawiający

- Wnętrze

- projektanci

- projekty

- Wykrywanie

- urządzenia

- dyktuje

- różne

- cyfrowy

- pilnie

- wyświetlacze

- dystans

- dystrybuowane

- Nie

- podwojenie

- z powodu

- czas trwania

- podczas

- każdy

- Wcześniej

- Ekosystem

- Efektywne

- faktycznie

- efektywność

- wydajny

- skutecznie

- starania

- powstanie

- podkreśla

- podkreślając

- zatrudniony

- zatrudniający

- Umożliwia

- umożliwiając

- obejmuje

- zakończenia

- koniec końców

- zapewnia

- Cały

- błąd

- Błędy

- eskalacja

- istota

- niezbędny

- istotnie

- Eter (ETH)

- Parzyste

- Każdy

- oczywisty

- ewoluuje

- przykład

- wyjątkowy

- wyłączony

- rozszerzenie

- ekspansja

- spodziewany

- ekspert

- ekspertyza

- rozciągać się

- rozsuwalny

- zewnętrzny

- ekstrakcja

- Oczy

- czynnik

- Czynniki

- daleko

- szybciej

- Korzyści

- Wyposażony w

- Postać

- Znajdź

- i terminów, a

- Pierwsza generacja

- pływ

- koncentruje

- następnie

- Ślad stopy

- W razie zamówieenia projektu

- formułowanie

- Naprzód

- FRAME

- od

- dalej

- generacja

- daje

- większy

- Zarządzanie

- Grupy

- Rozwój

- ręka

- Prowadzenie

- Wysoki

- wysoka wydajność

- wysoko

- Jednak

- HTML

- HTTPS

- tryb rozkazujący

- realizacja

- znaczenie

- ważny

- ulepszony

- in

- W innych

- zawierać

- Włącznie z

- wzrastający

- indywidualny

- przemysłowy

- pod wpływem

- nieodłączny

- właściwie

- zainicjować

- inicjatywa

- przykład

- Integruje się

- integracja

- integralność

- Interfejs

- interfejsy

- Internet

- Interoperacyjność

- najnowszych

- wewnętrzny

- przedstawiać

- Przedstawia

- wprowadzenie

- dotyczy

- IP

- IT

- iteracje

- JEGO

- samo

- jpg

- Tor

- Utajenie

- warstwa

- nioski

- Długość

- poziomy

- lewarowanie

- Prawdopodobnie

- Linia

- linie

- LINK

- linki

- relacja na żywo

- dłużej

- niski

- mac

- Dokonywanie

- zarządzanie

- i konserwacjami

- Maksymalna szerokość

- maksymalny

- Może..

- oznaczać

- pomiary

- mechanizm

- średni

- Pamięć

- wiadomość

- metoda

- metody

- skrupulatny

- minimalny

- zminimalizować

- minimalizuje

- minimalizowanie

- moduł

- Moduły

- jeszcze

- większość

- musi

- zbliżony

- Potrzebować

- sieci

- Niemniej jednak

- Nie

- noty

- już dziś

- cel

- of

- często

- on

- ONE

- tylko

- operacyjny

- zoptymalizowane

- Optymalizuje

- Option

- or

- Inne

- koniec

- ogólny

- par

- parametry

- szczególnie

- ścieżka

- komputery

- dla

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- spektakle

- fizyczny

- Fizycznie

- rurociąg

- kluczowy

- plato

- Analiza danych Platona

- PlatoDane

- odgrywa

- plus

- potencjał

- power

- praktyki

- głównie

- pierwotny

- wygląda tak

- przetwarzanie

- Procesory

- progresja

- Przewiduje

- ochrona

- protokół

- puls

- cel

- Popychanie

- jakość

- radio

- przypadkowy

- zasięg

- Kurs

- ceny

- dosięgnąć

- osiągnięcie

- reakcja

- Rzeczywistość

- otrzymać

- odbieranie

- recepcja

- redukcja

- rzetelny

- szczątki

- wykonanie

- Wymaga

- ograniczony

- wynikły

- krzepki

- Rola

- ukorzeniony

- bieganie

- Skalowalność

- Skala

- scenariusze

- bezszwowy

- druga

- widziany

- segment

- wrażliwy

- oddzielny

- służyć

- usługa

- zestaw

- kilka

- shared

- Short

- powinien

- ściąganie

- Signal

- znacznie

- Krzem

- symulacja

- Rozmiar

- So

- rozwiązanie

- Rozwiązania

- rozpiętości

- pionierem

- specyficzny

- swoiście

- specyfikacja

- prędkości

- wiosna

- STAGE

- standard

- normalizacja

- standardy

- przechowywanie

- strategie

- Streaming

- kolejny

- znaczny

- sukces

- taki

- odpowiedni

- wsparcie

- symbol

- system

- dostosowane

- trwa

- technika

- Techniki

- Technologia

- niż

- że

- Połączenia

- ich

- Tam.

- a tym samym

- w związku z tym

- Te

- to

- Przez

- A zatem

- kleszcz

- Związany

- czas

- czasy

- do

- Top

- tradycyjny

- ruch drogowy

- przenieść

- przekazać

- Potroić

- drugiej

- typowy

- zazwyczaj

- nieunikniony

- zrozumienie

- podjąć

- jednostka

- zbliżających

- na

- za pomocą

- wykorzystać

- przez

- wyobrażać sobie

- Droga..

- we

- jeśli chodzi o komunikację i motywację

- który

- Podczas

- szerszy

- w

- w ciągu

- by

- jeszcze

- zefirnet

- zero