Na IEDM 2023 Naoto Horiguchi przedstawił CFET i integrację Middle of Line. Miałem okazję porozmawiać z Naoto na temat tej pracy, a niniejszy opis opiera się na jego prezentacji na IEDM i naszej dyskusji. Zawsze lubię rozmawiać z Naoto. Jest on jednym z liderów w rozwoju technologii logicznych, wyjaśnia technologię w łatwy do zrozumienia sposób, jest responsywny i łatwy w obsłudze.

Dlaczego potrzebujemy CFET

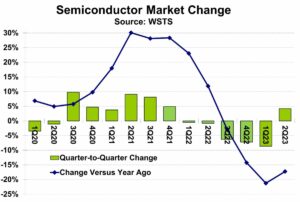

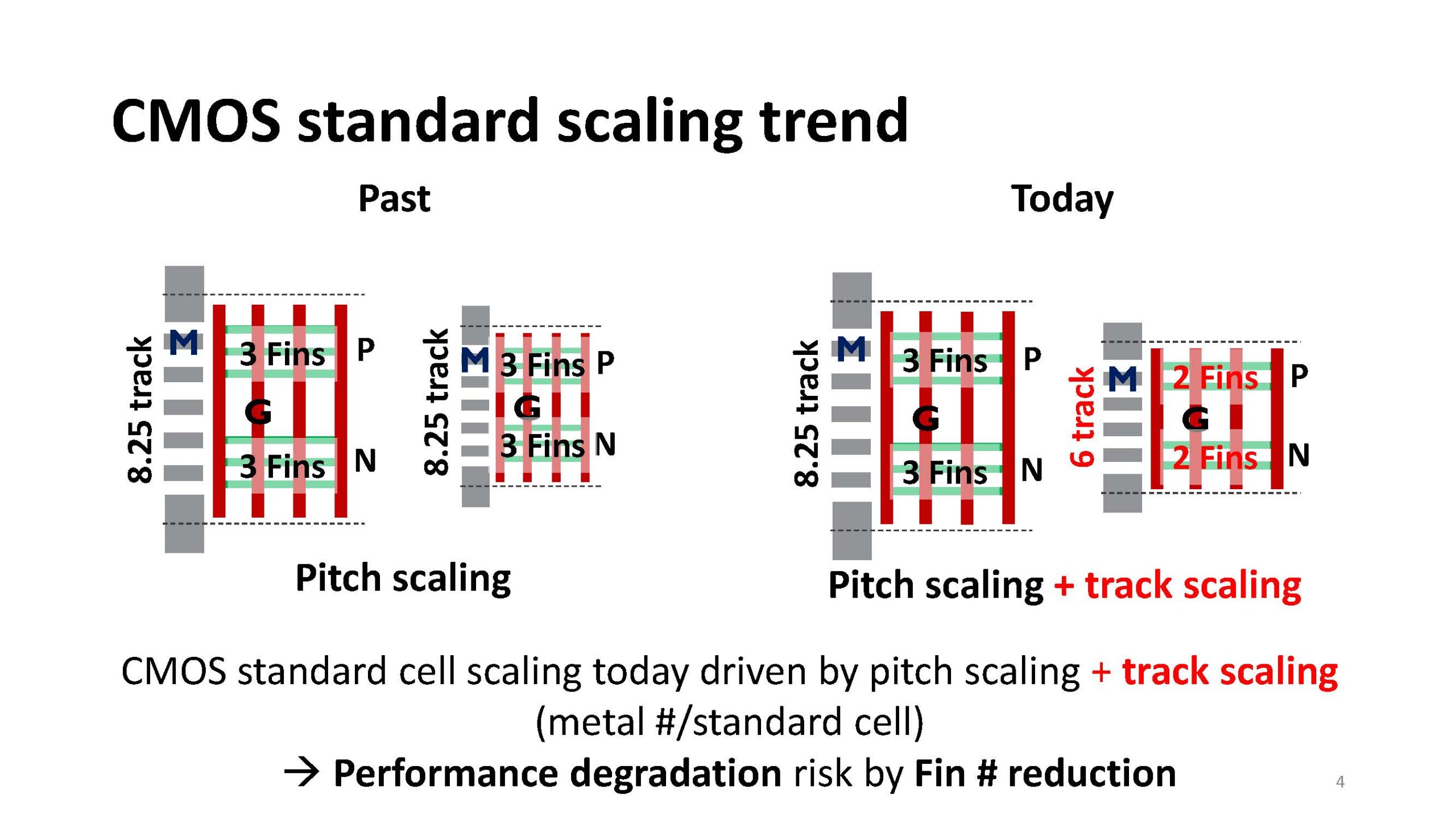

Ponieważ skalowanie CMOS przeszło ze skalowania opartego wyłącznie na skoku do skalowania opartego na skoku i skalowaniu na podstawie ścieżki, konieczne stało się usuwanie populacji żeberek, patrz rysunek 1. Każde zmniejszenie liczby żeber zmniejsza wydajność.

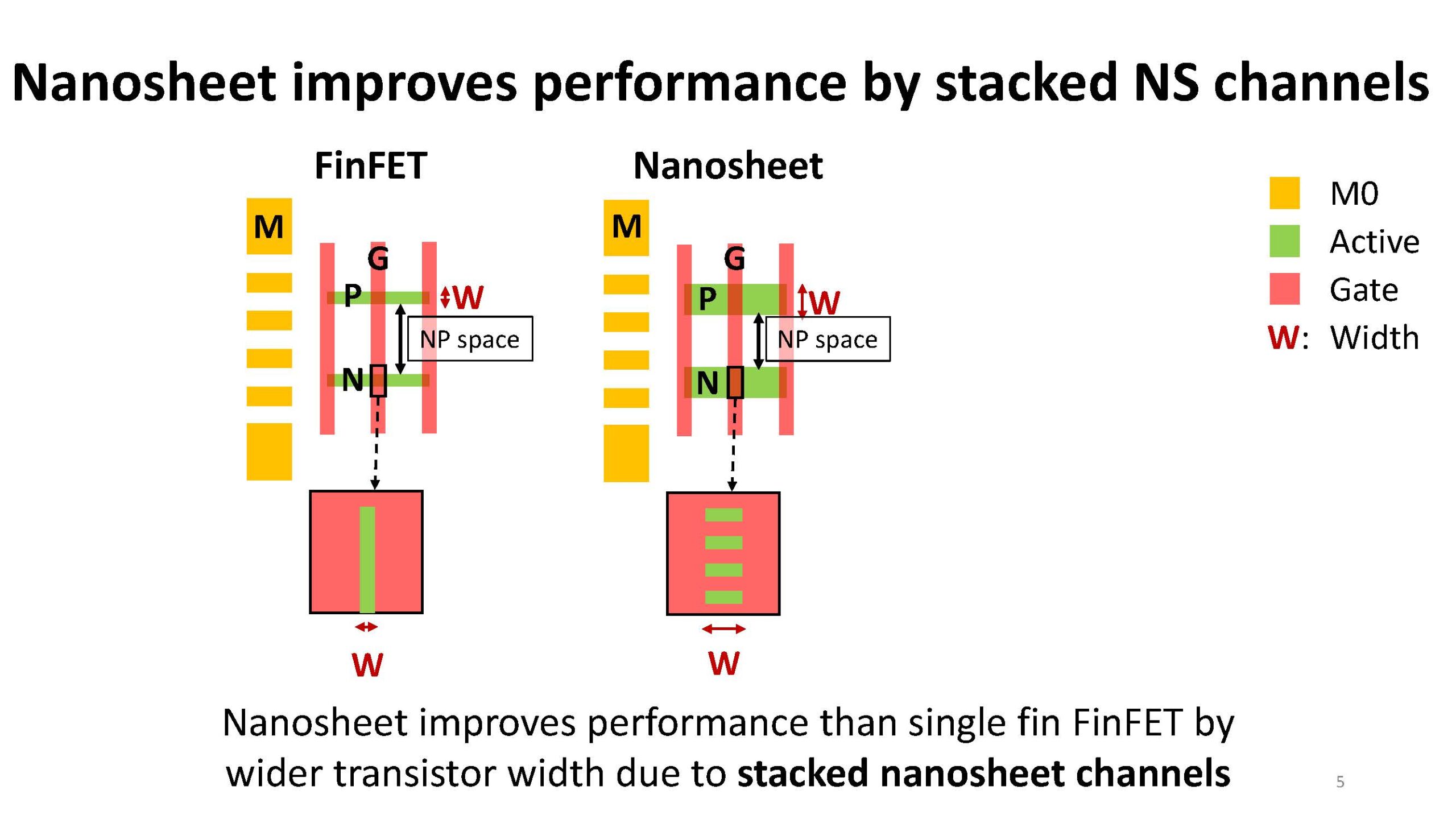

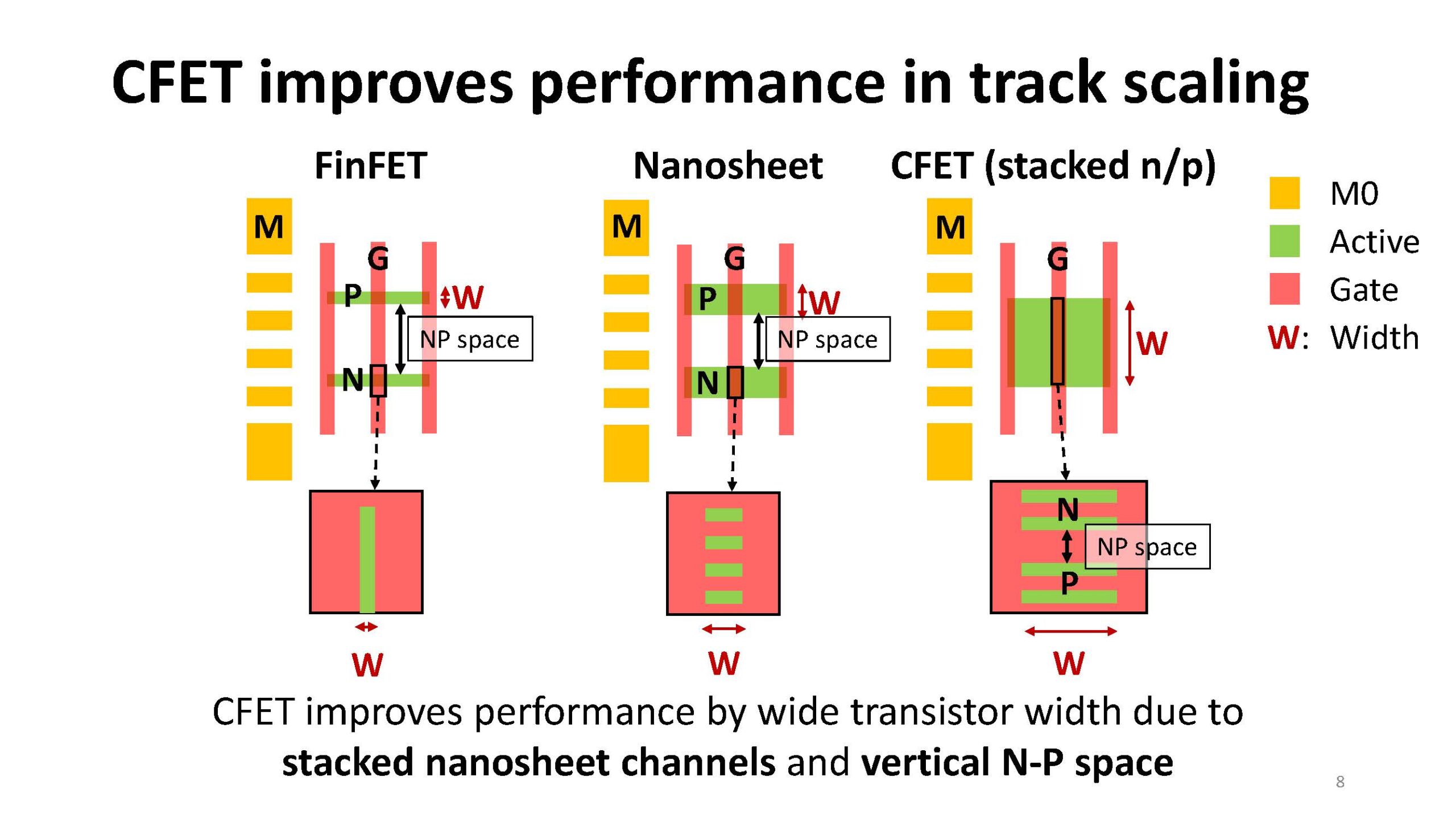

Przechodząc z FinFEts na stosy HWydajność poziomych nanoarkuszów (HNS) można poprawić/odzyskać poprzez szersze stosy nanoarkuszów i ułożenie wielu nanoarkuszów w pionie, patrz rysunek 2.

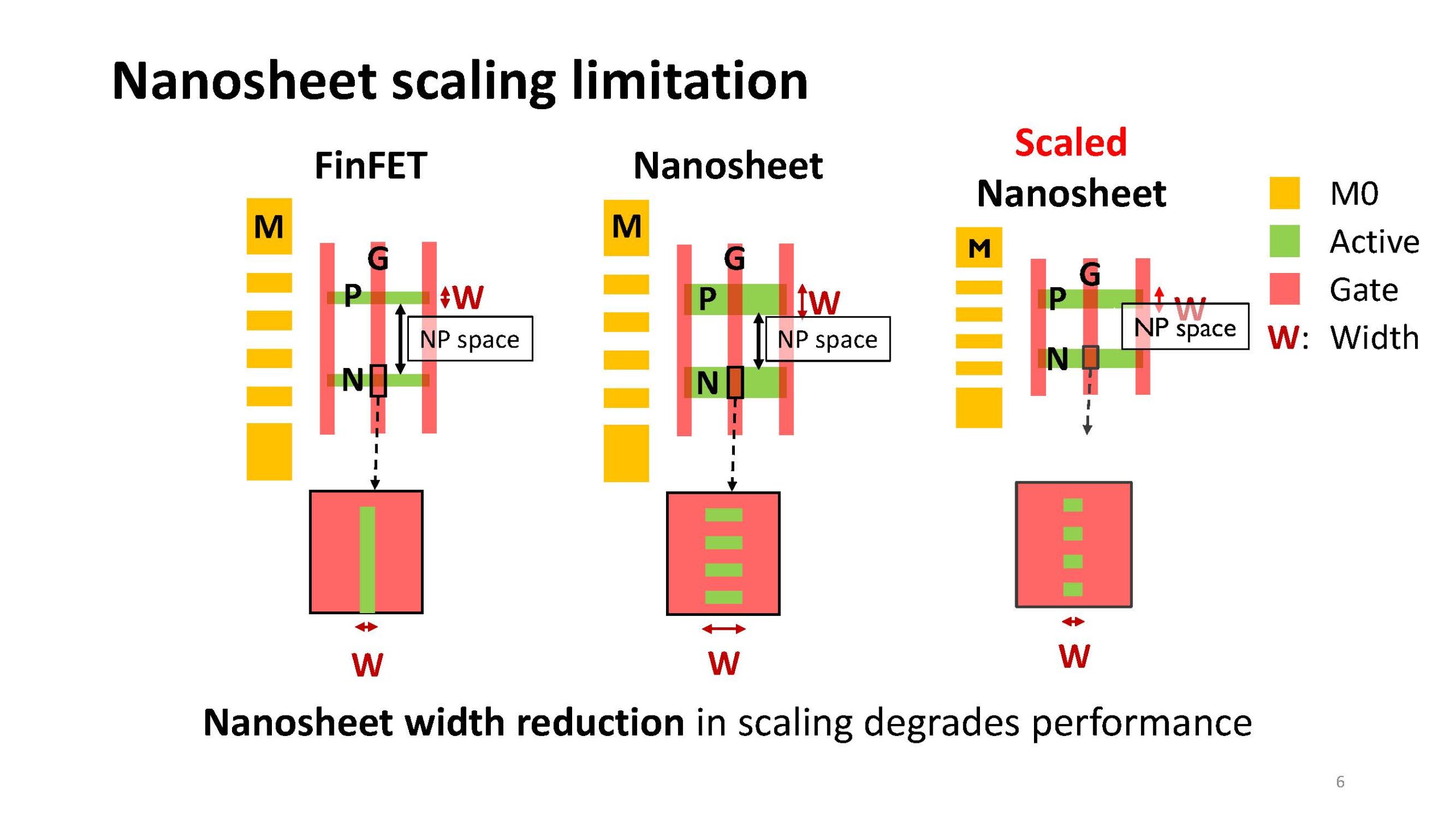

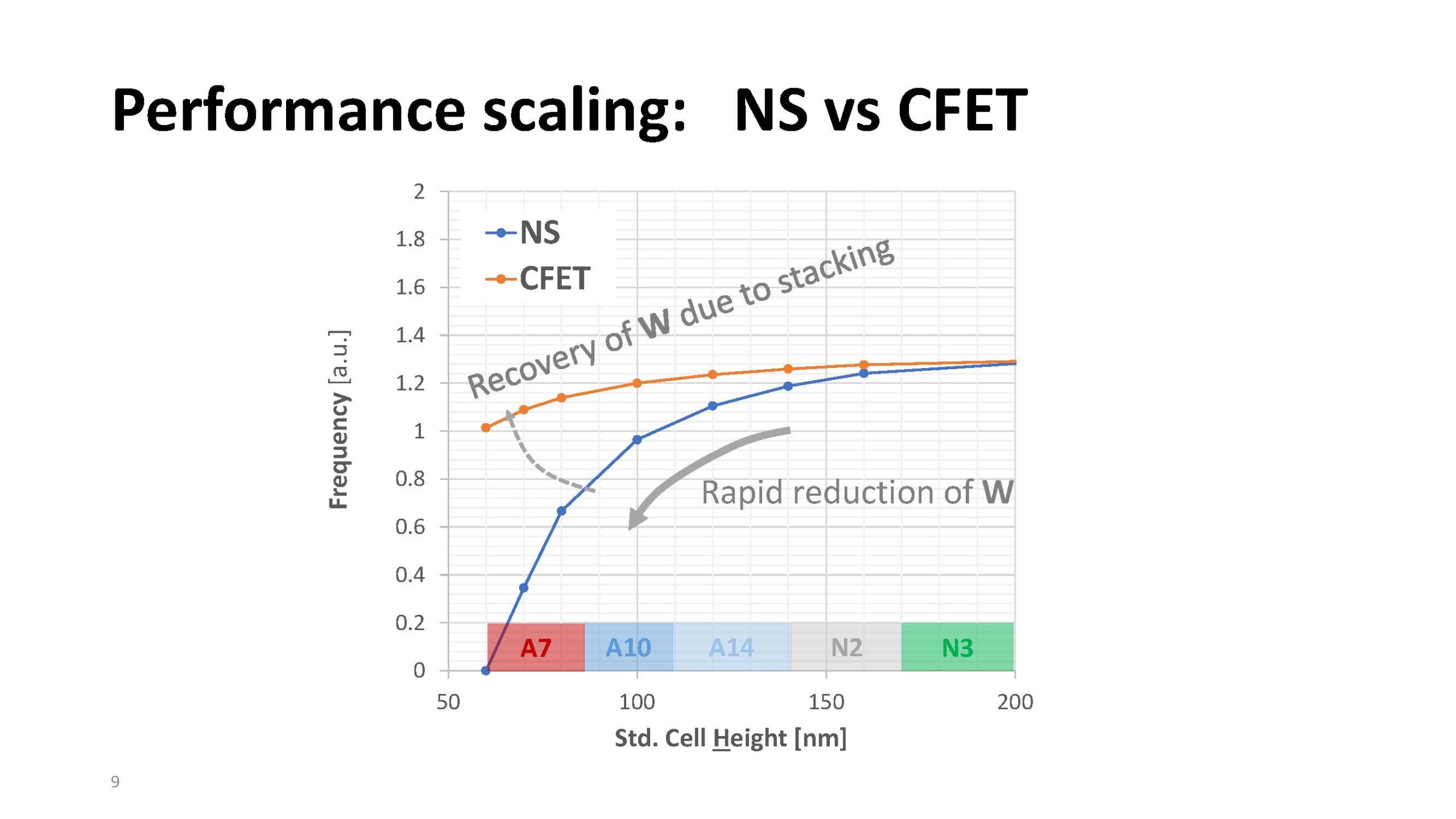

Ale jak widzieliśmy w przypadku skalowania nanoarkuszów FinFET ostatecznie prowadzi do zmniejszonej wydajności, patrz rysunek 3.

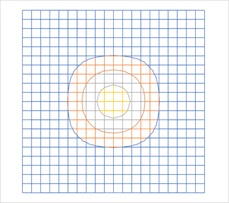

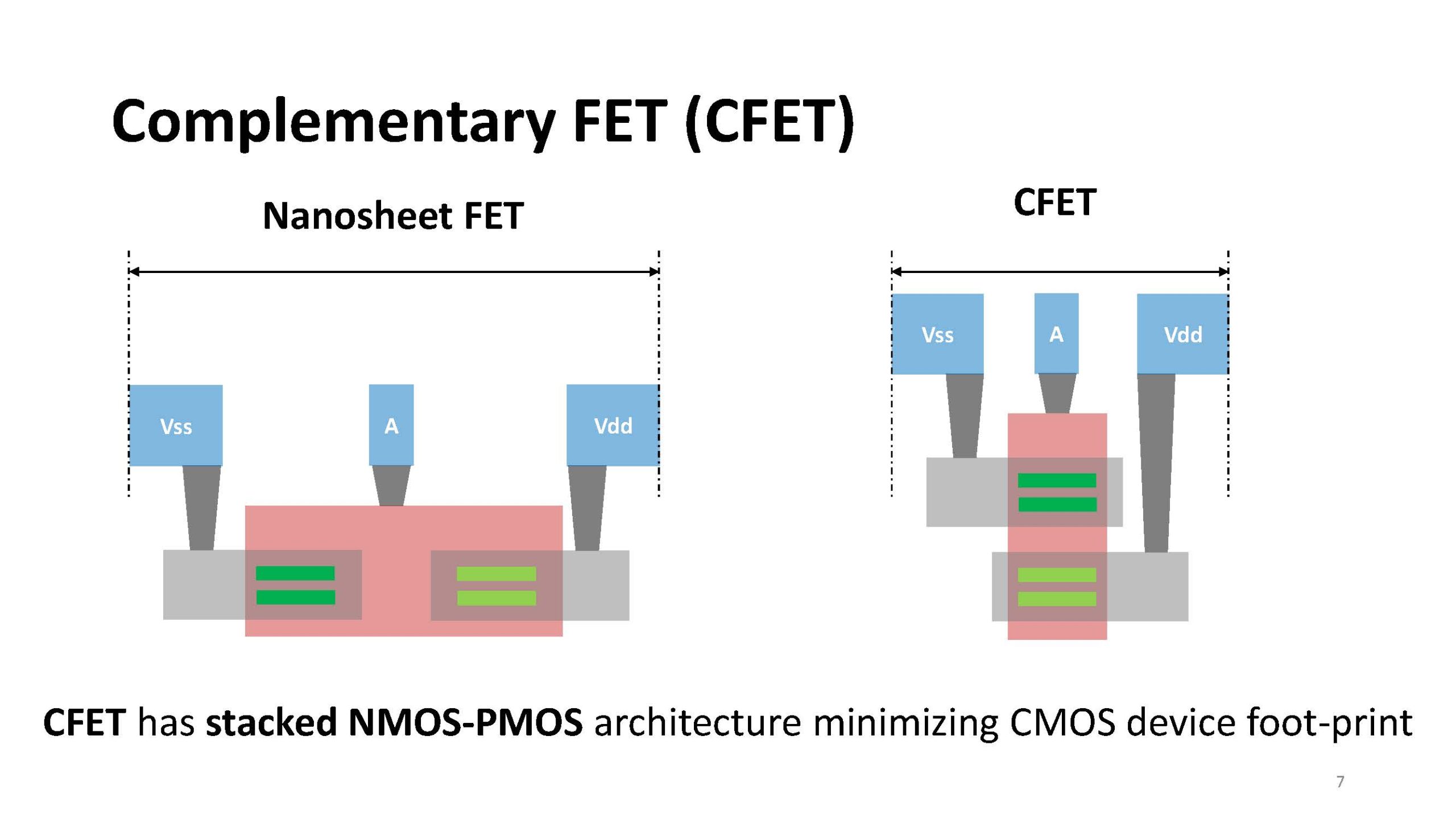

CFET (komplementarne FET) łączą nFET i pFET, patrz rysunek 4.

CFET po raz kolejny resetują ograniczenia skalowania, ponieważ nFET i pFET są ułożone w stos, a odstępy np między urządzeniami stają się pionowe, a nie poziome, co umożliwia szersze arkusze, patrz rysunek 5.

Rysunek 6 przedstawia porównanie wydajności HNS i CFET z wysokością komórki, podkreślając przewagę CFET.

Monolityczny kontra sekwencyjny CFET

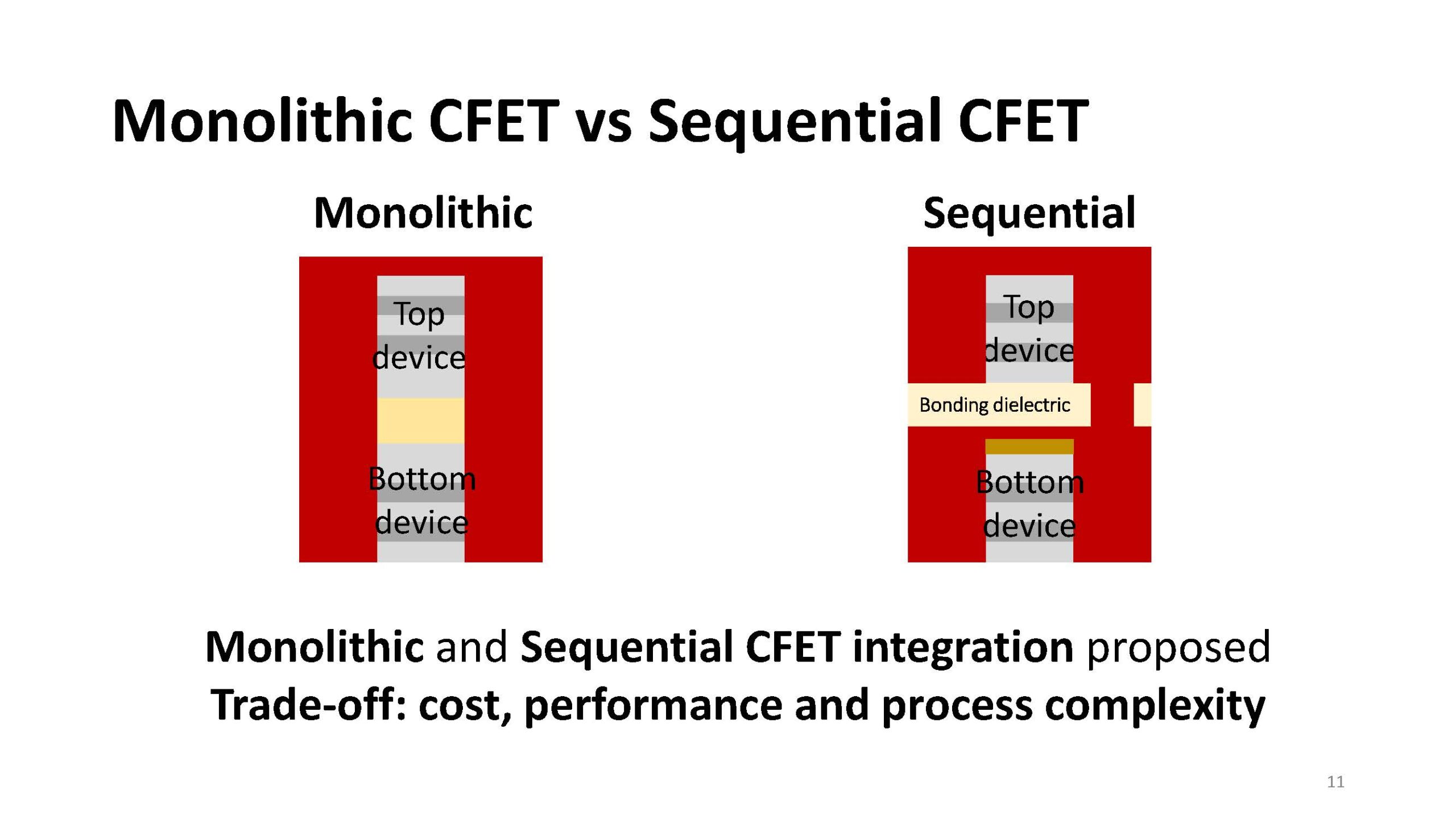

Istnieją dwa zasadniczo różne podejścia do wytwarzania CFET. W przepływie monolitycznym CFET są wytwarzane na płytce w ciągłym przebiegu procesu. W przepływie sekwencyjnym dolne urządzenie jest wytwarzane na jednej płytce, następnie druga płytka jest łączona z pierwszą płytką, a górne urządzenie jest wytwarzane na drugiej płytce.

W przepływie sekwencyjnym pomiędzy dwoma urządzeniami występuje dielektryk wiążący, patrz rysunek 7.

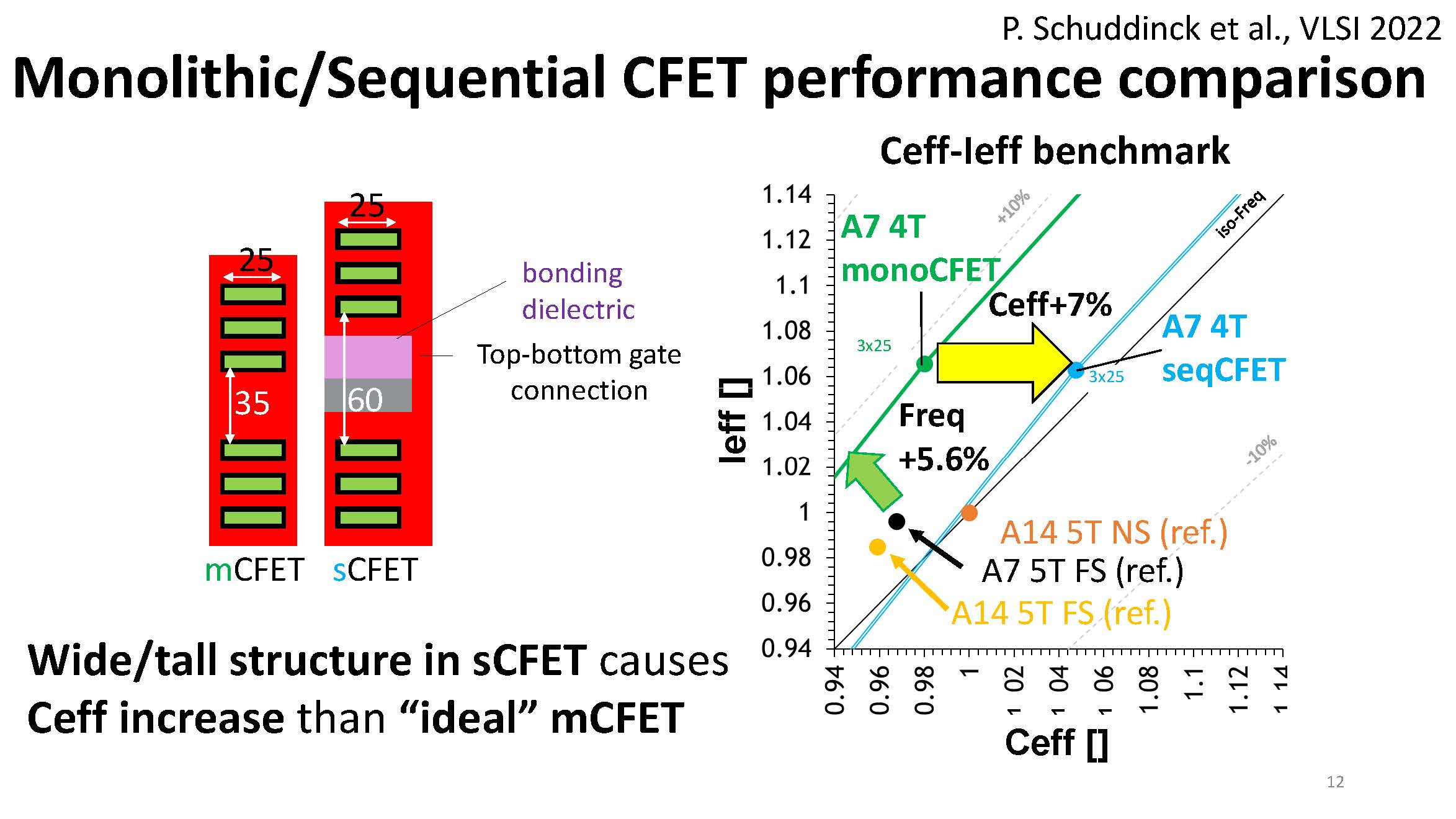

Ze względu na dielektryk wiążący konstrukcja jest wyższa i ma większy spadek pojemności, patrz rysunek 8.

Sekwencyjne CFET są droższe w produkcji niż monolityczne CFET, a poza tym i pogorszeniem wydajności wydaje się, że przemysł koncentruje się na monolitycznych CFET.

Monolityczne przetwarzanie CFET

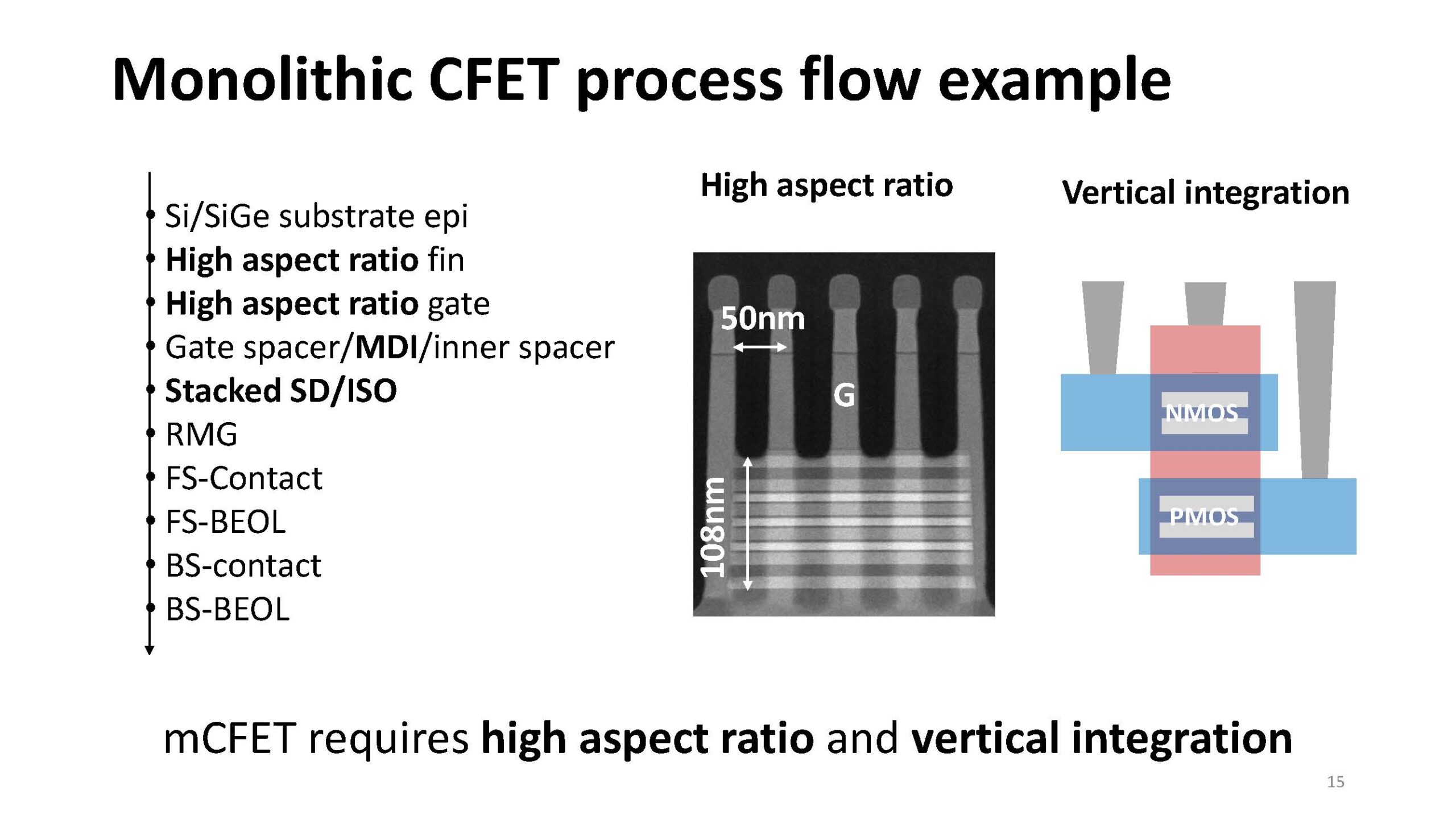

Monolityczny proces CFET przedstawiono na rysunku 9.

Kroki zaznaczone pogrubioną czcionką są szczególnie trudne:

- Poziome stosy nanoarkuszów (płetwy) mają już wysoki współczynnik kształtu, więc aby utworzyć CFET, należy ułożyć stosy nFET i pFET jeden na drugim, tworząc stosunkowo grubą warstwę pomiędzy ponad dwukrotnie większą wysokością.

- Formacja bramy ma również wysoki współczynnik kształtu, jak opisano w poprzednim punkcie.

- Źródło/dreny epitaksjalne muszą być odizolowane od siebie w pionie.

- Nie zostało to wyraźnie zaznaczone, dolne źródło/dren urządzenia jest wytwarzane, a następnie górne źródło/dren urządzenia. Obróbkę cieplną górnego urządzenia i kolejne etapy należy przeprowadzić w wystarczająco niskich temperaturach, aby nie uszkodzić dolnego urządzenia.

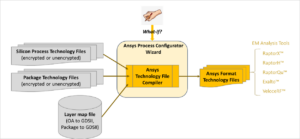

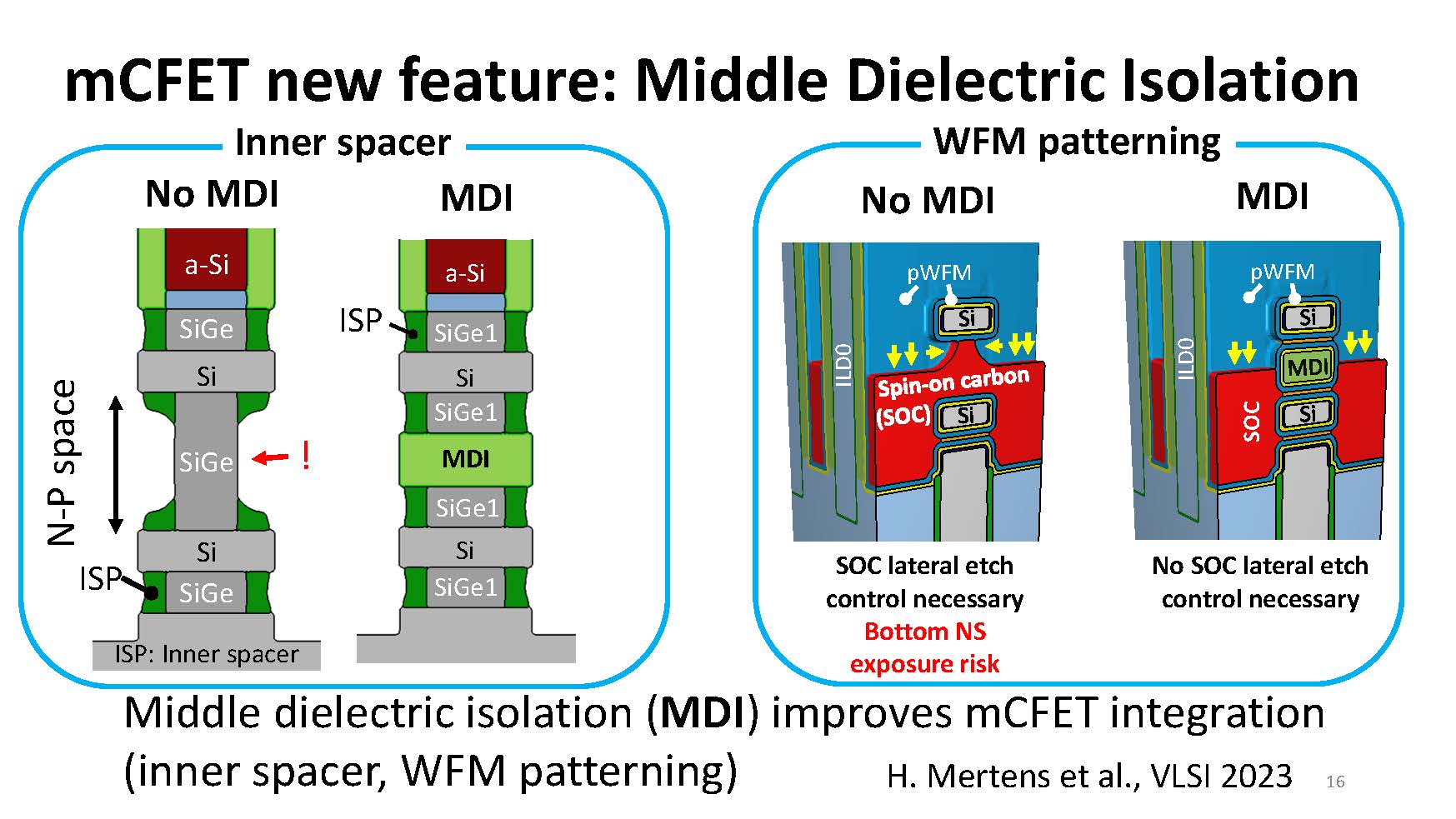

Szczególnie interesującą częścią tej prezentacji była część dotycząca izolacji środkowej dielektryka (MDI). Nie widziałem wcześniej tego problemu. MDI potwierdza wewnętrzną przekładkę i wzór materiału roboczego (WFM).

Rysunek 10 ilustruje wpływ MDI na tworzenie się wewnętrznej przekładki (lewa strona) i wzór WFM (prawa strona).

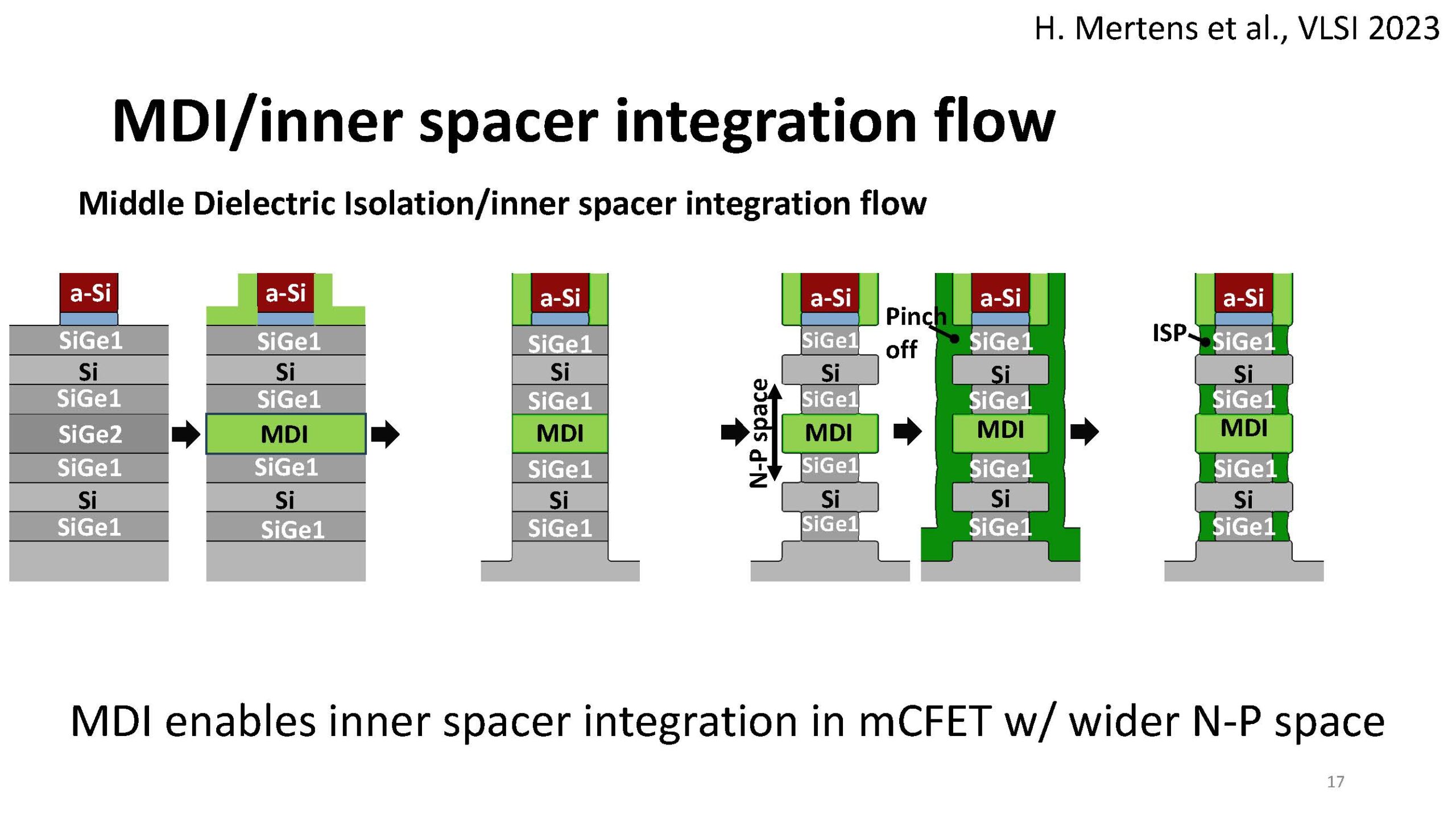

Rysunek 11 ilustruje przebieg integracji MDI.

Całkując MDI, można zwiększyć pionowe odstępy między nFET i pFET bez wpływu na tworzenie wewnętrznego elementu dystansującego.

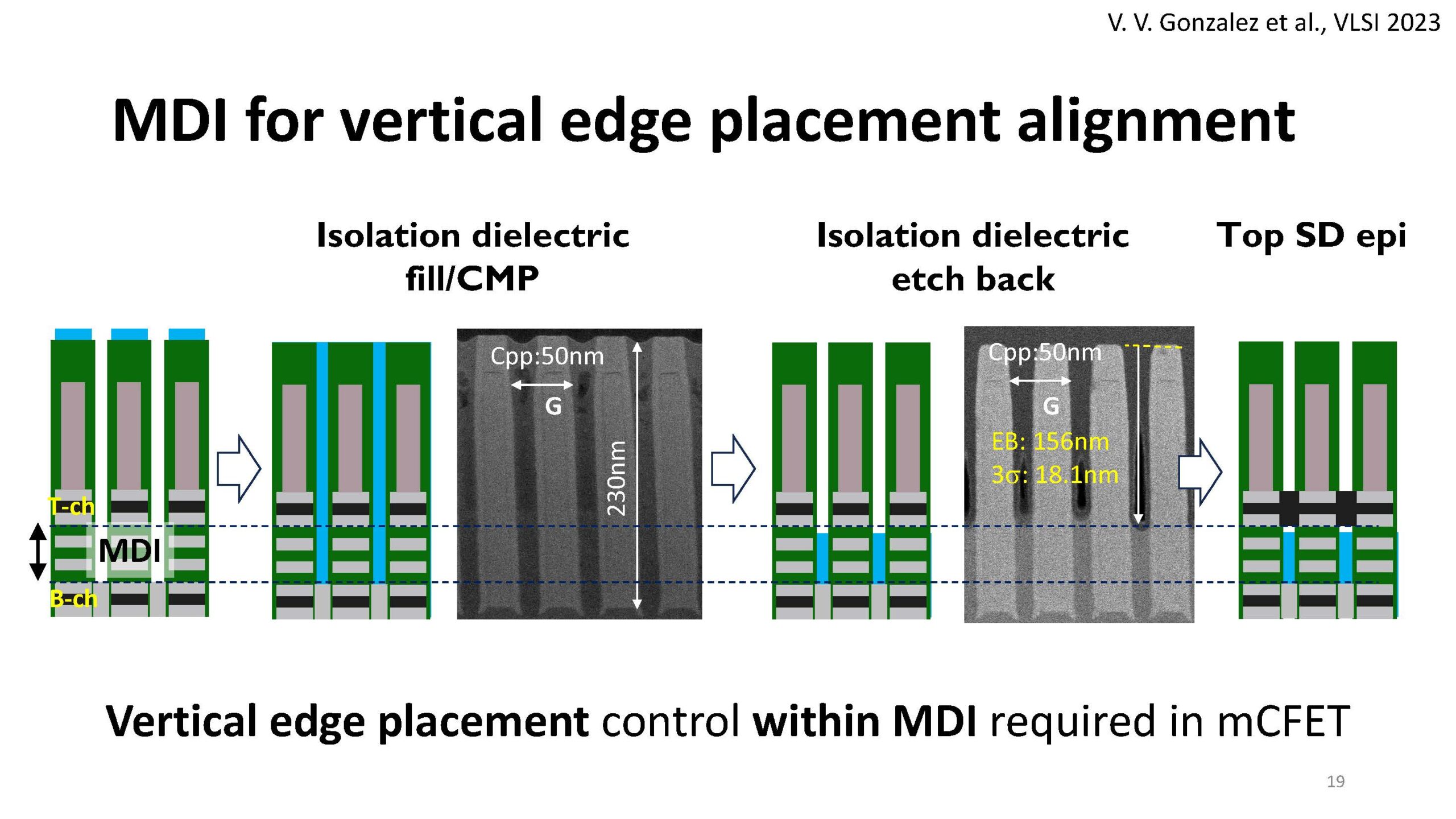

Jak wspomniano wcześniej, wytwarzane jest dolne źródło/odpływ urządzenia, a następnie wytwarzane jest górne źródło/odpływ urządzenia. Po uformowaniu dolnego źródła/drenu, osadza się dielektryk izolacyjny i ponownie go trawi, aby odsłonić górne urządzenie dla powstania epitaksjalnego źródła/drenu. Wytrawianie izolacji należy kontrolować za pomocą wysokości MDI, patrz rysunek 12.

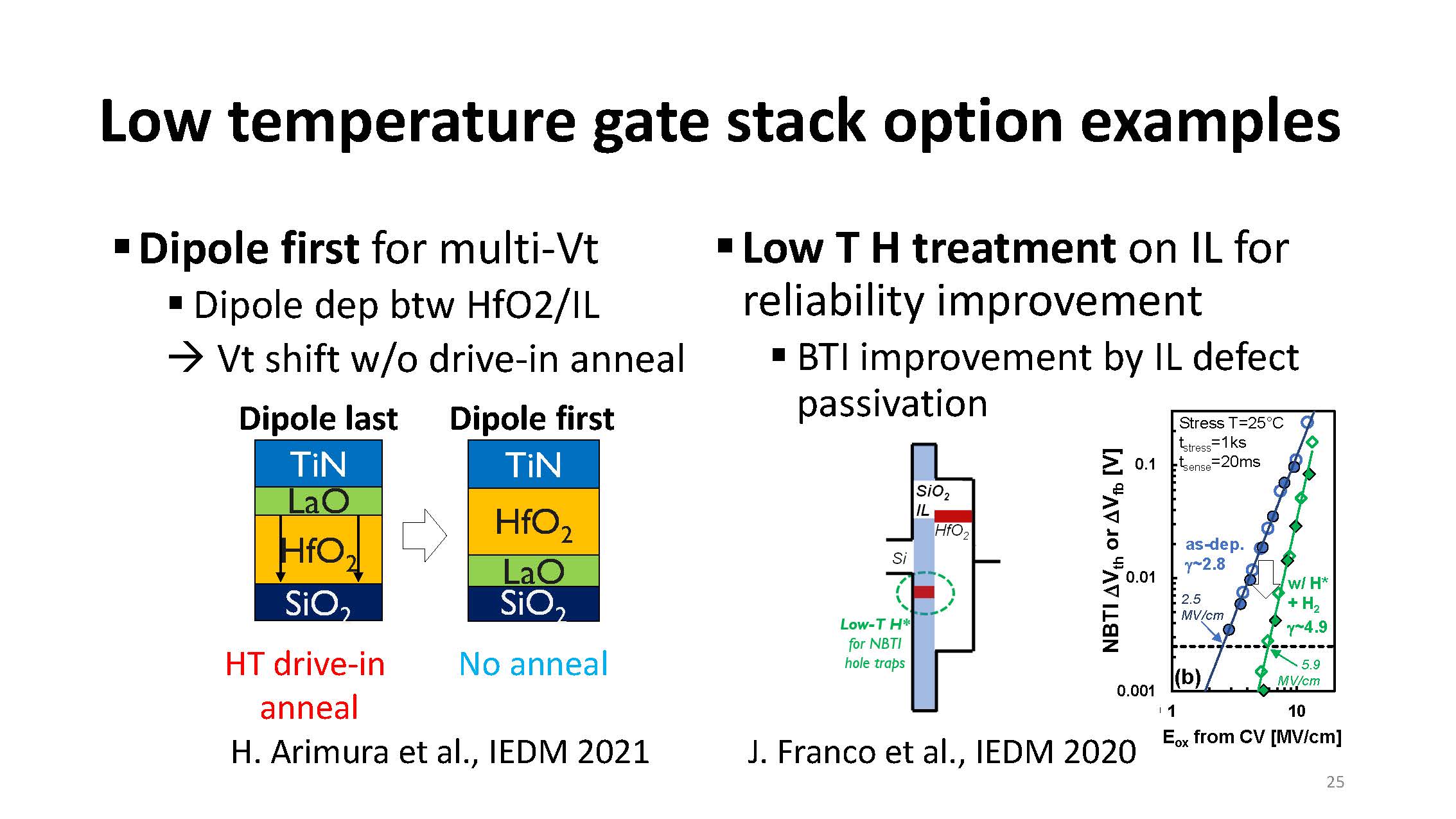

Aby zminimalizować degradację termiczną wydajności urządzenia, nowe opcje WFM z obróbką dipolową i bez procesów wyżarzania i tworzenia międzywarstw w niskiej temperaturze, patrz rysunek 13.

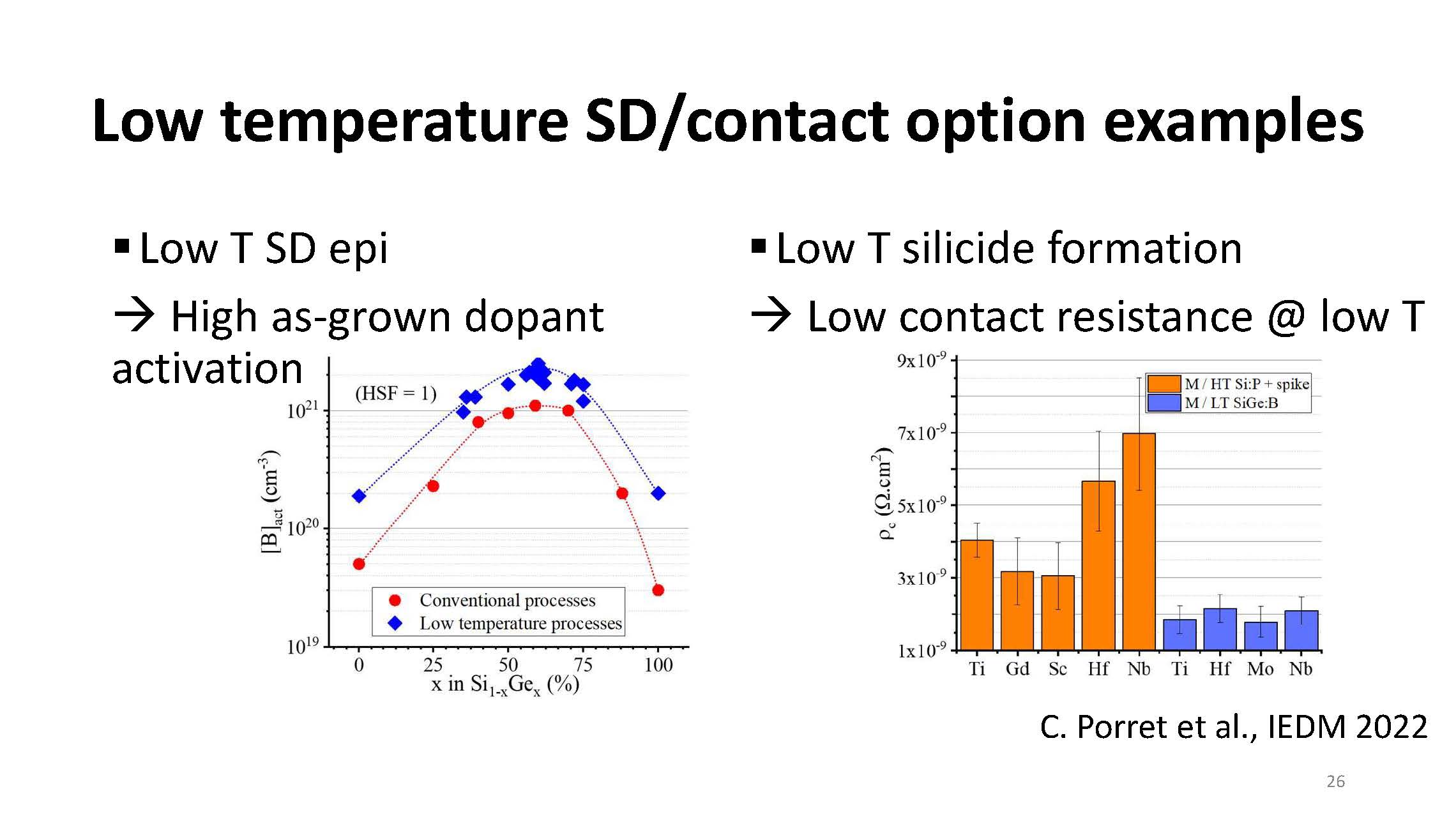

Do tworzenia kontaktu potrzebne są także niskotemperaturowe źródła/odpływy i niskotemperaturowe krzemki, patrz rysunek 14.

Krzemek niskotemperaturowy będzie szczególnie ważny w przypadku bezpośredniego kontaktu tylnej części z dolnym urządzeniem. Interkonekt CFET wymaga styków z dolnym i górnym urządzeniem, a wraz z pojawieniem się tylnego zasilania, górne urządzenie będzie połączone ze stosem wzajemnych połączeń z przodu, a dolne urządzenie będzie połączone z tyłu. Molibden (Mo) i niob (Nb) są obiecujące dla pFET, a skand (Sc) jest obiecujący dla nFET, chociaż Sc jest trudny do osadzenia w ALD.

Połączenie tylne i środkowe linii

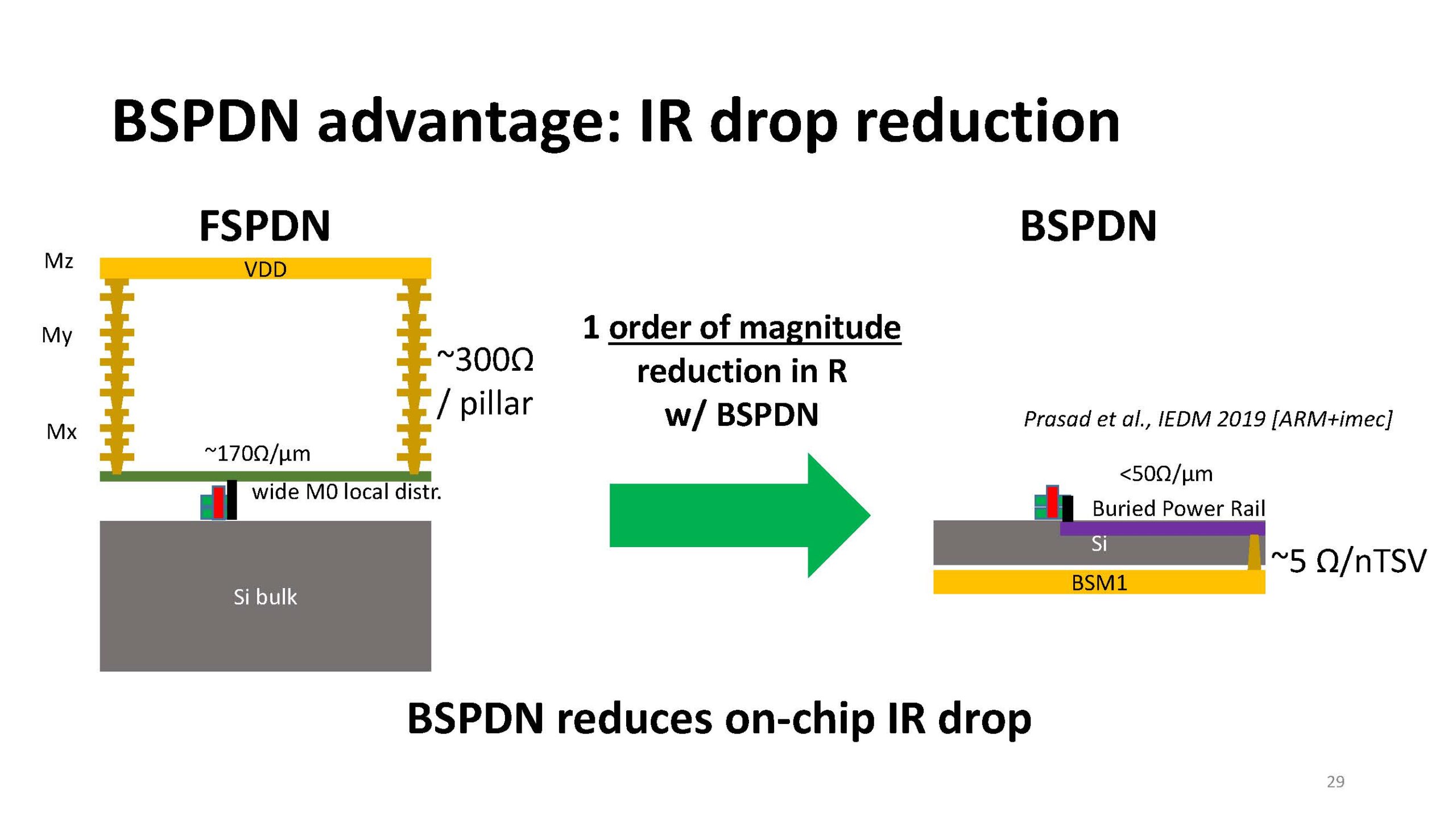

Tak jak pisałem o tym wcześniej tutaj Oczekuje się, że sieć Back Side Power Delivery Network (BSPDN) zostanie wprowadzona w tym roku przez firmę Intel, firmę Samsung i TSMC w 2026 r. Podział połączeń wzajemnych na złącza sygnałowe z przodu i złącza zasilania z tyłu zmniejsza spadek podczerwieni (utratę mocy) o rząd wielkości, patrz rysunek 15.

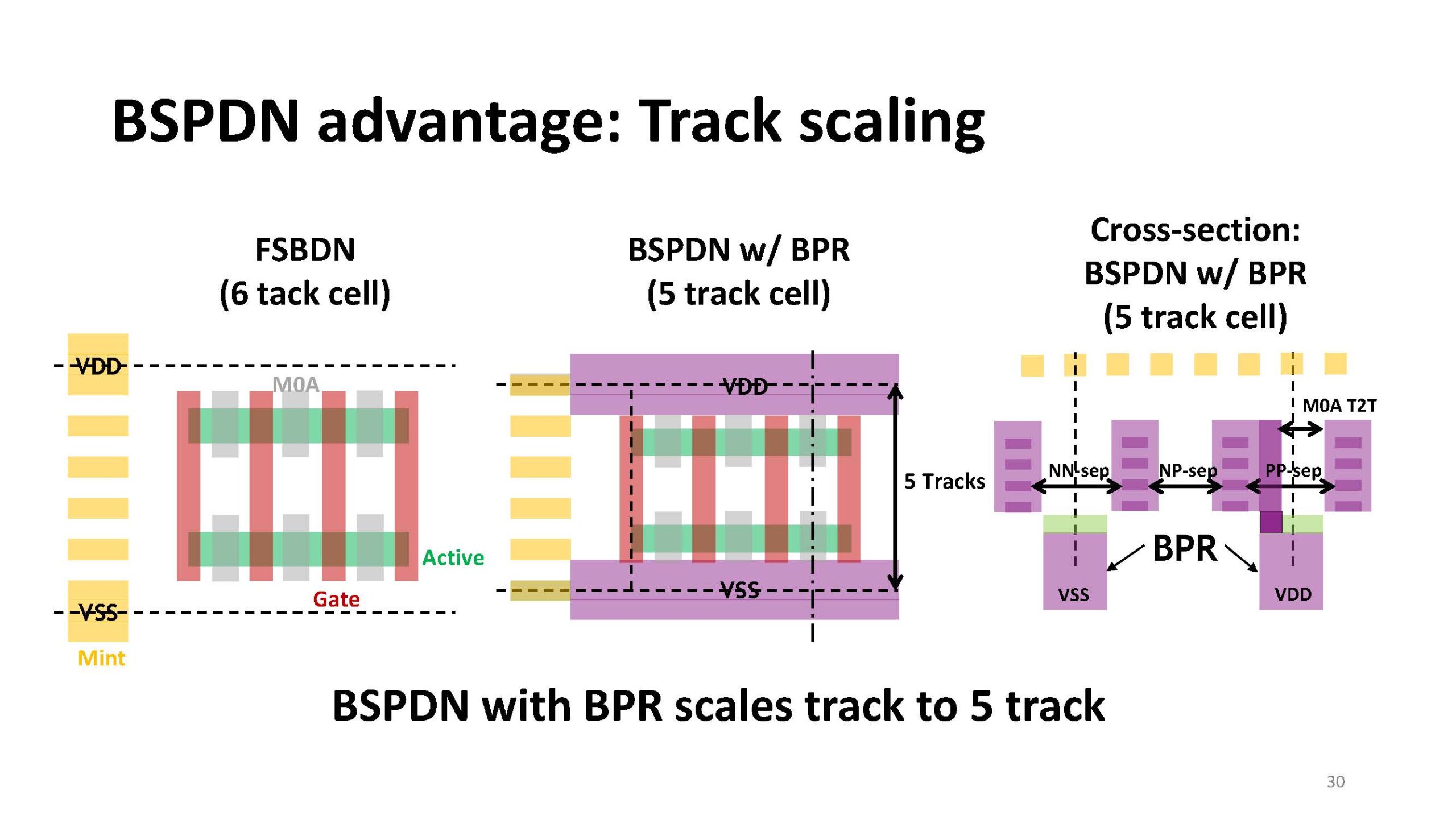

BSPDN poprawia także skalowanie ścieżek, umożliwiając redukcję komórki 6-ścieżkowej do 5-ścieżkowej, patrz rysunek 16.

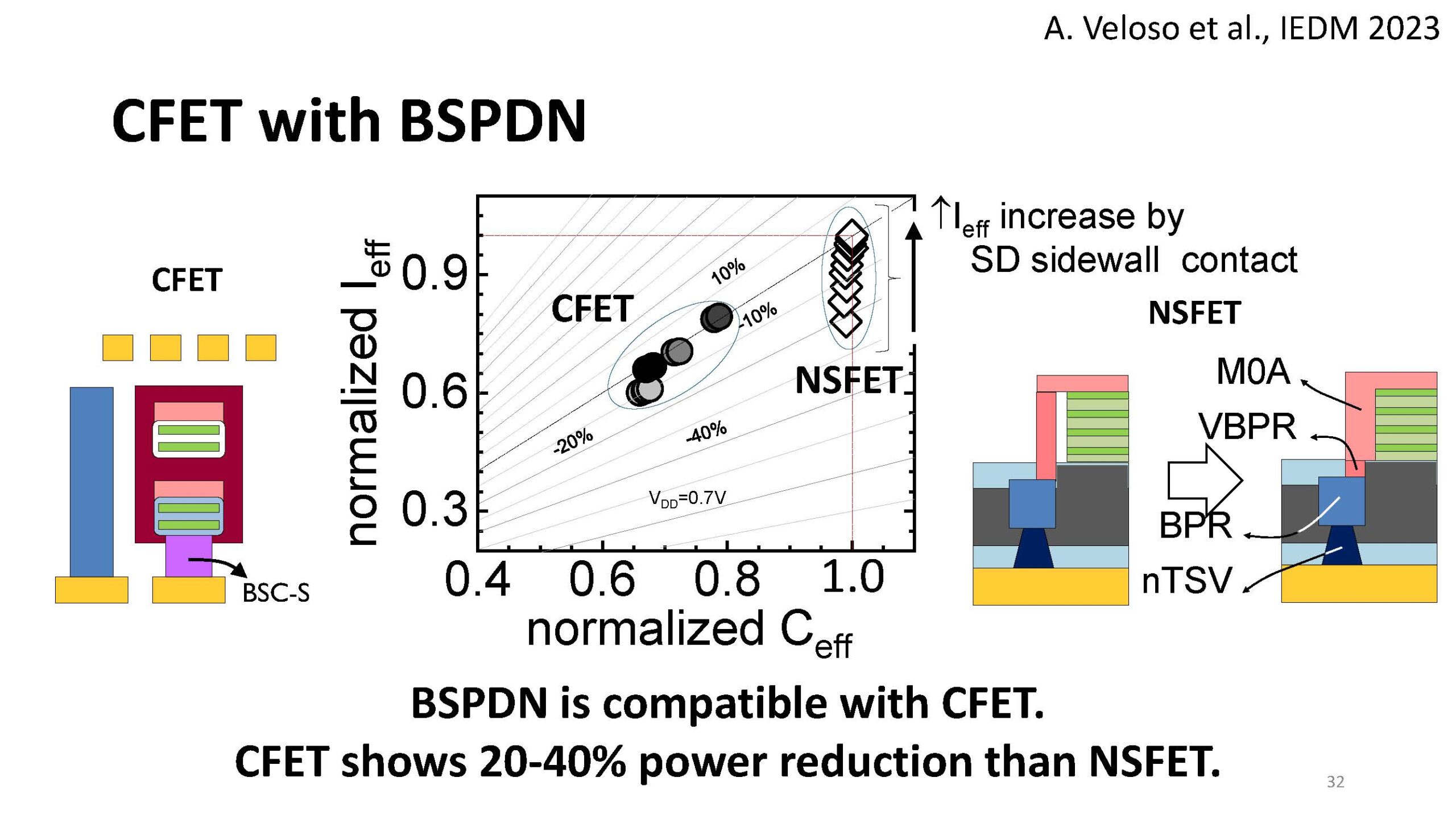

Integracja BSPDN z CFET może zapewnić redukcję mocy o 20% do 40% w porównaniu z nanoarkuszami ułożonymi poziomo (HNS), patrz rysunek 17.

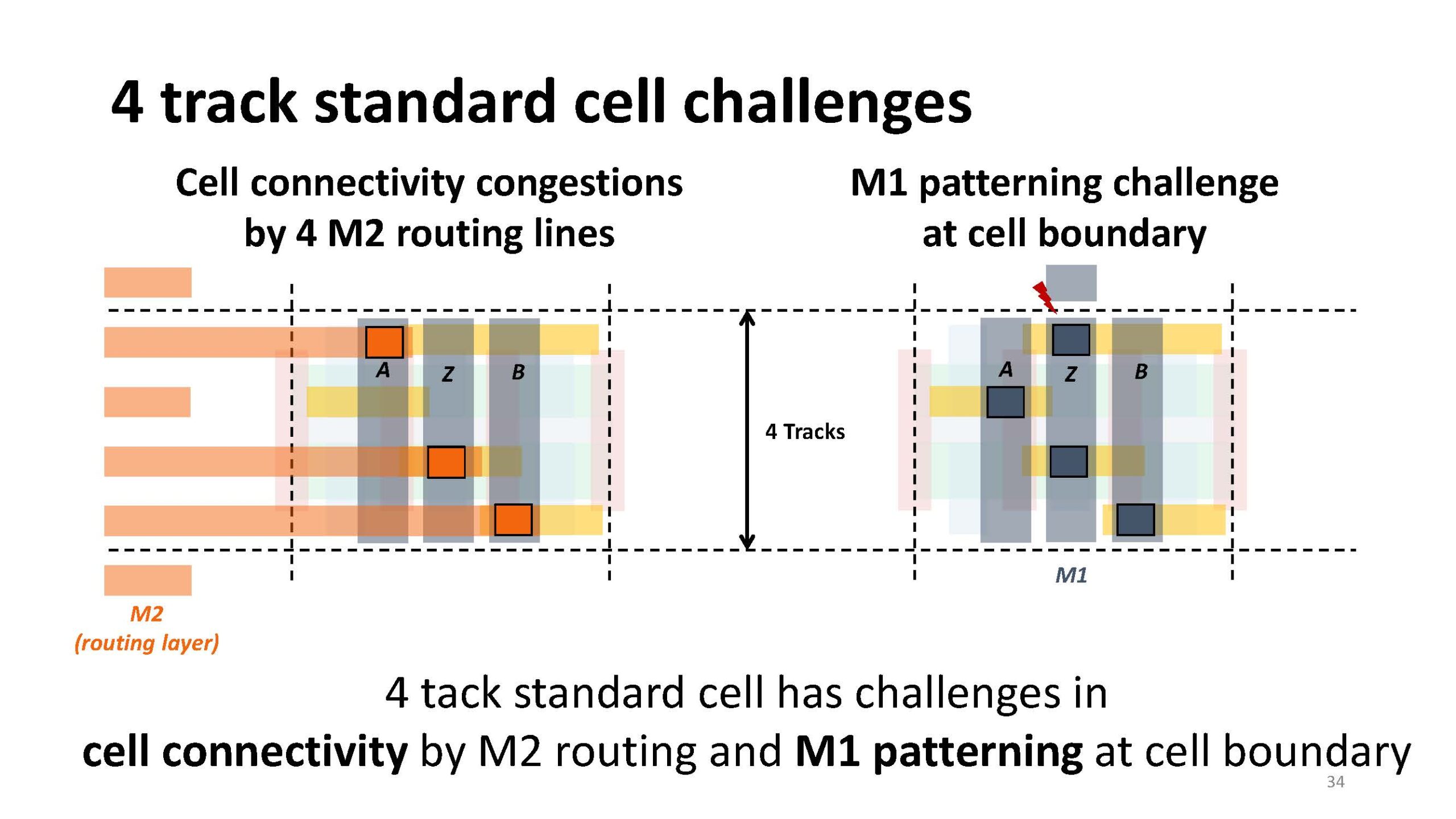

Aby wyjść poza komórkę 5-ścieżkową i przekształcić ją w komórkę 4-ścieżkową, należy pokonać wyzwania związane z wzajemnymi połączeniami, patrz rysunek 18.

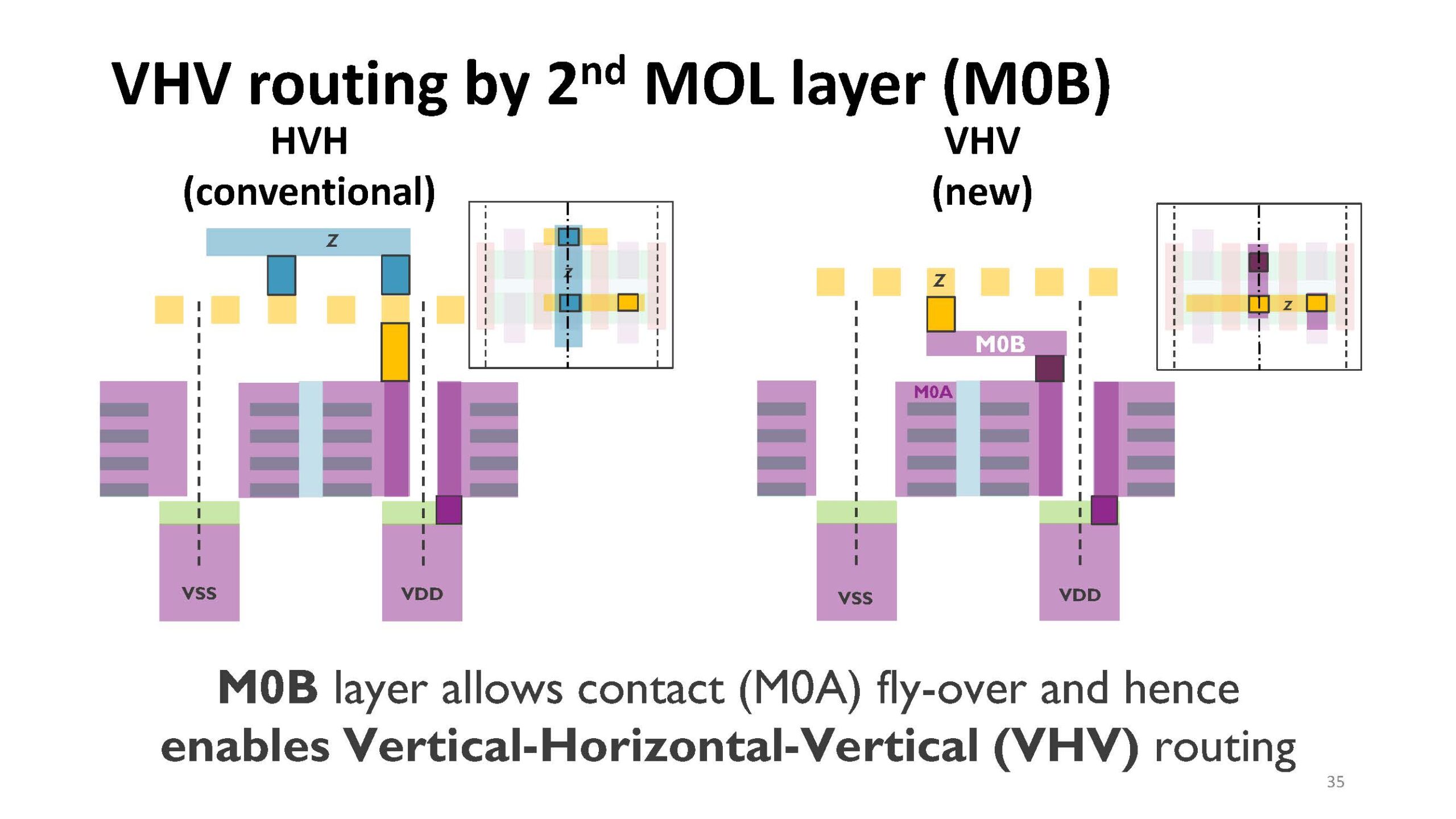

Układ pionowo-poziomo-pionowy z dodatkowymi warstwami środka linii (MOL) umożliwia tworzenie komórek 4-ścieżkowych, patrz rysunek 19.

O pracy Imeca w tym obszarze pisałem już wcześniej tutaj więc nie będę powtarzał tej informacji.

Zapytałem Naoto, czego potrzeba, aby przejść poza komórkę 4-ścieżkową do komórki 3-ścieżkowej, odpowiedział, że Imec pracuje teraz nad tą optymalizacją i że może wymagać dodatkowych warstw MOL i ewentualnie połączenia od góry do dołu obok urządzenie, które miałoby wpływ na standardowy układ komórek.

Zapytałem także Naoto, kiedy jego zdaniem możemy spodziewać się wdrożenia CFET, i odpowiedział, że prawdopodobnie będzie to generacja logiki A10 lub generacja A7.

Autorzy zauważają, że Intel, Samsung i TSMC opublikowały w tym roku prace dotyczące CFET na IEDM, a zarówno Intel, jak i TSMC posiadają mapy opcji technologicznych pokazujące, że FinFET ustępują miejsca HNS, a następnie CFET.

Wnioski

Imec w dalszym ciągu wykazuje doskonały postęp w rozwoju CFET jako opcji nowej generacji, po HNS. W pracy opisano wszystkie opcje integracji urządzeń oraz opcje BSPDN i MOL.

Przeczytaj także:

IEDM 2023 – Modelowanie emisji dwutlenku węgla w fabryce płytek 300 mm

Aktualizacja ASML SEMICON West 2023

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- PlatoData.Network Pionowe generatywne AI. Wzmocnij się. Dostęp tutaj.

- PlatoAiStream. Inteligencja Web3. Wiedza wzmocniona. Dostęp tutaj.

- PlatonESG. Węgiel Czysta technologia, Energia, Środowisko, Słoneczny, Gospodarowanie odpadami. Dostęp tutaj.

- Platon Zdrowie. Inteligencja w zakresie biotechnologii i badań klinicznych. Dostęp tutaj.

- Źródło: https://semiwiki.com/semiconductor-services/340811-iedm-2023-imec-cfet/

- :ma

- :Jest

- :nie

- $W GÓRĘ

- 06

- 07

- 08

- 09

- 1

- 10

- 11

- 12

- 13

- 14

- 15%

- 16

- 17

- 19

- 2023

- 2026

- 25

- 26

- 29

- 30

- 32

- 35%

- 7

- 8

- 9

- a

- O nas

- dodatek

- Dodatkowy

- Korzyść

- nadejście

- Po

- ponownie

- Wszystkie kategorie

- już

- również

- Chociaż

- zawsze

- an

- i

- pojawia się

- awanse

- SĄ

- POWIERZCHNIA

- AS

- aspekt

- At

- z powrotem

- na podstawie

- BE

- bo

- stają się

- staje się

- być

- zanim

- pomiędzy

- Poza

- obie

- Dolny

- by

- wezwanie

- nazywa

- CAN

- węgiel

- komórka

- Komórki

- wyzwania

- wyzwanie

- szansa

- porównanie

- uzupełniający

- połączenie

- połączenia

- Ograniczenia

- skontaktuj się

- łączność

- ciągły

- ciągły

- kontrolowanych

- dostawa

- kaucja

- zdeponowany

- opisane

- oprogramowania

- urządzenie

- urządzenia

- różne

- kierować

- dyskusja

- do

- zrobić

- podwojenie

- Spadek

- każdy

- łatwo

- krawędź

- efekt

- umożliwiać

- Umożliwia

- cieszyć się

- dość

- ostatecznie

- doskonała

- spodziewany

- drogi

- Objaśnia

- wyraźnie

- FET

- Postać

- płetwa

- finał

- FINS

- i terminów, a

- pływ

- koncentruje

- obserwuj

- W razie zamówieenia projektu

- formacja

- od

- z przodu

- funkcjonować

- zasadniczo

- brama

- generacja

- Dający

- Go

- Wzrost

- miał

- Ciężko

- Have

- he

- wysokość

- Wysoki

- wyższy

- podświetlanie

- jego

- Poziomy

- HTTPS

- Huawei

- i

- ilustruje

- Rezultat

- wpływ

- realizowane

- ważny

- ulepszony

- poprawia

- in

- wzrosła

- przemysł

- Informacja

- wewnętrzny

- zamiast

- Integracja

- integracja

- Intel

- ciekawy

- najnowszych

- przedstawiać

- odosobniony

- izolacja

- problem

- IT

- jpg

- warstwa

- nioski

- układ

- Przywódcy

- Wyprowadzenia

- lewo

- Linia

- logika

- od

- niski

- robić

- Mapy

- kolega

- materiał

- Maksymalna szerokość

- Może..

- wzmiankowany

- Środkowy

- może

- zminimalizować

- modelowanie

- MOL

- Monolityczny

- jeszcze

- przeniesienie

- wielokrotność

- musi

- niezbędny

- Potrzebować

- potrzebne

- sieć

- Nowości

- Następny

- Nie

- noty

- już dziś

- numer

- of

- on

- pewnego razu

- ONE

- optymalizacja

- Option

- Opcje

- or

- zamówienie

- Inne

- ludzkiej,

- na zewnątrz

- Przezwyciężać

- strona

- część

- szczególnie

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- Smoła

- umieszczenie

- plato

- Analiza danych Platona

- PlatoDane

- plus

- punkt

- możliwie

- Post

- power

- teraźniejszość

- presentation

- przedstawione

- prezenty

- poprzedni

- poprzednio

- Pro

- wygląda tak

- procesów

- przetwarzanie

- Postęp

- obiecujący

- dowodzi

- zapewniać

- opublikowany

- czysto

- stosunek

- Czytaj

- zmniejszyć

- Zredukowany

- zmniejsza

- redukcja

- stosunkowo

- powtarzać

- wymagać

- Wymaga

- czuły

- prawo

- Routing

- Powiedział

- Samsung

- SC

- skalowaniem

- druga

- widzieć

- widziany

- pokazać

- seans

- bok

- Signal

- So

- mówić

- stos

- ułożone w stos

- układanie w stosy

- Półki na książki

- standard

- Cel

- Struktura

- kolejny

- Wspierający

- Brać

- rozmawiać

- Technologia

- Rozwój technologii

- niż

- że

- Połączenia

- następnie

- termiczny

- to

- w tym roku

- myśl

- czas

- do

- Top

- śledzić

- przeniesiony

- TSMC

- drugiej

- Aktualizacja

- Przeciw

- pionowy

- pionowo

- przez

- vs

- była

- Droga..

- we

- DOBRZE

- Zachód

- Co

- jeśli chodzi o komunikację i motywację

- szerszy

- będzie

- w

- bez

- Praca

- pracujący

- by

- napisać

- napisany

- rok

- ty

- zefirnet