Stres termiczny jest dobrze znanym problemem w zaawansowanych opakowaniach, podobnie jak wyzwania związane z naprężeniami mechanicznymi. Oba są pogarszane przez heterogeniczną integrację, która często wymaga mieszania materiałów o niekompatybilnych współczynnikach rozszerzalności cieplnej (CTE).

Efekty już się pojawiają i prawdopodobnie będą jeszcze gorsze, gdy gęstość pakietów wzrośnie powyżej 1,000 uderzeń na chip.

„Łączysz metale, które mają stosunkowo wysoki CTE, następnie masz polimery, które mają jeszcze większą sztywność CTE, a następnie masz dielektryki, które mają wyjątkowo niski CTE. Po złożeniu wszystkiego w całość stres jest nieunikniony” — powiedział Mario Gonzalez, dyrektor naukowy i kierownik badań i rozwoju w zakresie modelowania mechanicznego i termicznego oraz charakteryzacji w imec.

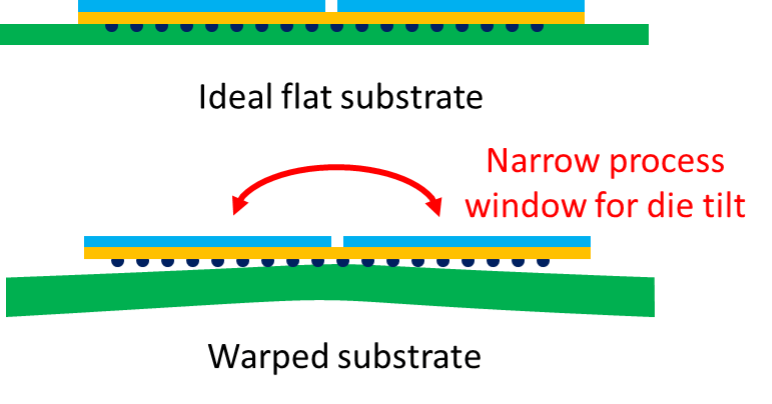

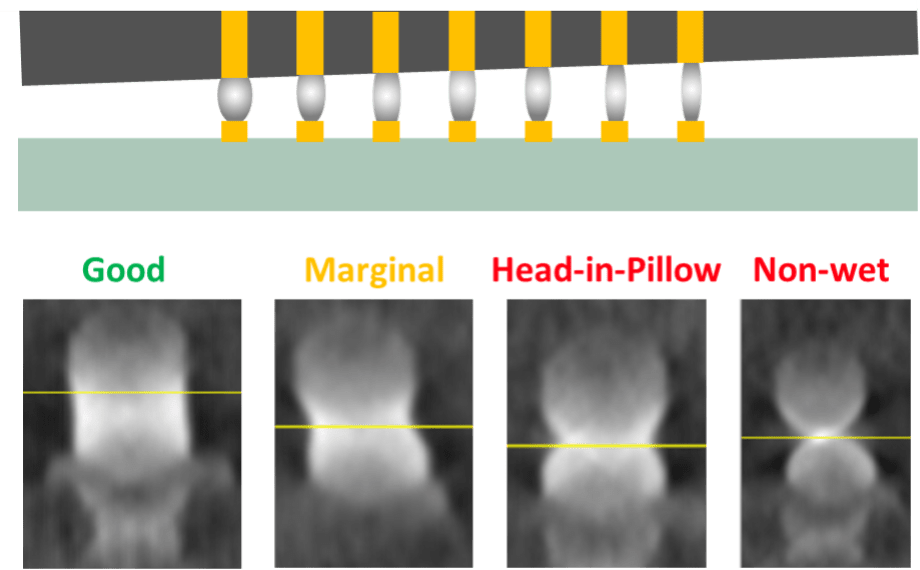

Takie naprężenia często powodują znaczne wypaczenie lub przechylenie matrycy, co z kolei prowadzi do warunków zmniejszających niezawodność. „Masz do czynienia z różnymi technologiami podłoża z wieloma warstwami” — powiedział Chip Greely, wiceprezes ds. inżynierii w firmie firmy Promex. „W szczególności różne grubości rdzeni w podłożach zaczynają powodować wiele klasycznych problemów mechanicznych, w tym wypaczanie, które stało się problemem dla niektórych większych graczy. Prosimy wielu naszych klientów, którzy mają wieloukładowy moduł system-in-pack z heterogeniczną integracją, o dostarczenie danych mory cienia ich substratów, abyśmy mogli zobaczyć, jak zmienia się wypaczenie w zależności od temperatury rozpływu i idealnie znaleźć jego punkt odbicia”.

Ten szczep ma różne negatywne skutki, doświadczane w wielu skalach wymiarowych, według Gilada Baraka, wiceprezesa ds. Nova. „Często zginanie i skręcanie funkcji na poziomie nanostruktury wynika z wbudowanego naprężenia, które zostało utworzone, jak w przypadku niektórych DRAM i nanoarkuszy logicznych front-end” – powiedział. „Inny przykład dotyczy obszarów w skali mikronowej, w których indukowane naprężenia uniemożliwiają wytwarzanie wysokiej klasy struktur półprzewodnikowych, co jest typowe w „strefach ochronnych” wokół przelotek krzemowych (TSV). Wreszcie, wpływ indukowanego naprężenia na dużą skalę może powodować wyginanie się płytki, znacznie komplikując obróbkę i wytwarzanie płytek, co grozi pęknięciem samej płytki. Wyginanie się płytek jest szczególnie widoczne podczas osadzania grubych warstw dielektrycznych, co jest powszechne podczas wytwarzania urządzeń 3D NAND”.

Dobrą wiadomością jest to, że branża jest bardzo świadoma tych i związanych z nimi problemów. Zła wiadomość jest taka, że wciąż brakuje rozwiązań, chociaż obecnie bada się wiele podejść.

„Istnieją różne metodologie ograniczania wypaczeń, ale żadna z nich nie jest w pełni skuteczna i zawsze wiąże się z kompromisami” — powiedział Frank Chen, dyrektor ds. aplikacji i zarządzania produktami w Bruker Nano Powierzchnie i metrologia. „Problemy nie ograniczają się do wąskiej grupy aplikacji. Za każdym razem, gdy przymocujesz kostkę do innego podłoża, będziesz mieć te problemy.

Wszystko to oznacza, że inspekcja i metrologia muszą nadal odgrywać kluczową rolę. Inne problemy, takie jak gorące punkty, również mogą się nasilić, gdy wiele chipów zostanie połączonych w heterogeniczne pakiety.

„Podczas testu różne chipy nagrzewają się w różnym czasie i w różnych temperaturach, tworząc potencjalne gorące punkty, które należy odpowiednio schłodzić” — powiedział Andrei Berar, starszy dyrektor ds. Amkor. „Oprócz tworzenia specyficznych kontrolerów termoaktywnych — pasujących do powierzchni różnych chipów — podejmowane są znaczne wysiłki w celu opracowania adaptacyjnych kontrolerów termicznych, które mogą„ przewidywać ”gorące punkty na podstawie wektorów dostarczonych przez program testowy”.

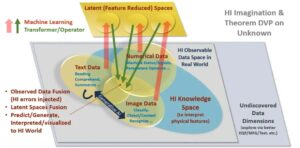

Takie kombinacje prowadzą również do coraz częstszego stosowania metrologii hybrydowej – łączenia różnych technik w celu jak najszybszego dotarcia do źródła problemów.

Projektowanie, kontrola, testowanie rozwiązań

Rzeczywiście, klasyczna zależność między projektowaniem, inspekcją i naprężeniami termomechanicznymi stała się jeszcze bardziej złożona dzięki tysiącom coraz mniejszych i bardziej delikatnych połączeń.

Jednym z rezultatów jest ponowne położenie nacisku na przesunięcie w lewo, aby, miejmy nadzieję, „zaprojektować” problemy z CTE i wynikające z tego efekty kaskadowe, które mogą prowadzić do przegrzania i naprężeń mechanicznych. Zdaniem Andrasa Vass-Varnai, kierownika ds. Siemens Digital Industries Software.

„Kosymulacja termiczna i strukturalna z wykorzystaniem obliczeniowej dynamiki przepływu (CFD), modelowania metodą elementów skończonych (FEA) itp. na wczesnym etapie projektowania opakowania pomaga zarówno zrozumieć oczekiwaną wydajność zespołu, jak i zapewnia dobrą podstawę do” Optymalizacja oparta na sztucznej inteligencji, ponieważ wiele opcji projektowych można sparametryzować” — wyjaśnił Vass-Varnai. „Po zbudowaniu pierwszego prototypu przejściowe testy termiczne mogą pomóc w mapowaniu wydajności termicznej komponentu. Jeśli istnieje rozbieżność między oczekiwanym a rzeczywistym zachowaniem termicznym, dane testowe można wykorzystać do „kalibracji” właściwości materiału cyfrowego bliźniaka opakowania i zaktualizowania bibliotek materiałów w celu uzyskania większej początkowej dokładności przyszłych projektów”.

Znalezienie najlepszego sposobu testowania macierzy wypukłości i projektowania do testów jest coraz większym wyzwaniem. „A co, jeśli jest sygnał, który idzie w górę iw dół?” zapytał Rob Aitken, A Synopsys kolega. „Stwarza to problem testowy, ponieważ teraz masz sygnał, który idzie donikąd i inny sygnał, który pochodzi znikąd, i musisz wymyślić, jak zamierzasz przetestować te rzeczy. Czy je sondujesz? Ale w takim przypadku musisz zachować wymiary fizyczne, a wtedy ryzykujesz uszkodzenie mechaniczne. A może znajdujesz jakąś strukturę podobną do JTAG? Ale to zmniejsza wydajność tych punktów łączących. Jesteśmy w fazie szeroko zakrojonych eksperymentów, w której wszyscy mówią: „Może to zadziała, może tamto zadziała”. W tej chwili niekoniecznie chciałbym obstawiać, co to jest „to”.

Według JCET istnieją zarówno pośrednie, jak i bezpośrednie opcje testowe do badania defektów. Na przykład CSAM (komputerowa skaningowa tomografia akustyczna) i rentgen 3D są pośrednie, podczas gdy mechaniczna analiza przekrojowa jest narzędziem bezpośredniego dowodu. JCET posiada zaawansowany sprzęt do charakteryzacji termicznej, aby scharakteryzować problemy materiałowe/konstrukcyjne wynikające również z wad mechanicznych.

Inspekcja optyczna jest, jak zawsze, najszybszym podejściem do inspekcji na linii, ale najlepszą praktyką jest podejście hybrydowe. „Najlepszą metodą wykrywania zwarć/otwarć i defektów brzeżnych byłoby SPI (kontrola pasty lutowniczej), AOI przed rozpływem (automatyczna kontrola optyczna), AOI po rozpływie, aż do rentgena w linii” — radzi Timothy Skunes, wiceprezes ds. badań i rozwój w firmie Nordson Test & Inspection Cyberoptyka teczka.

Ponadto przydatne mogą być inne metody, zwłaszcza w zaawansowanych węzłach. Na przykład najnowszym podejściem do charakteryzowania naprężeń w urządzeniach półprzewodnikowych jest spektroskopia ramanowska (RS). „RS doskonale nadaje się do pomiarów strukturalnych, oferując szybkie pomiary rzędu sekund i małe plamki o wielkości kilku mikronów, umożliwiające szczegółowe pomiary” — powiedział Barak z firmy Nova. „Trudność bezpośredniego pomiaru naprężeń struktur przed wprowadzeniem spektroskopii ramanowskiej jako narzędzi metrologicznych w fabryce doprowadziła do testów na znacznie późniejszych etapach procesu produkcyjnego”.

Ostatecznie, przy dokładnej inspekcji, nie ma konieczności chodzenia na skróty. Obliczenia budżetowe mogą wymagać pomiarów porównawczych, takich jak początkowy koszt nowego instrumentu w porównaniu z bieżącymi kosztami nadmiernych RMA. Jest jeszcze jedna rzecz do rozważenia — jak upewnić się, że możesz ufać swoim danym.

„Czy zamierzasz wyrzucić to, co prawdopodobnie było dobrym materiałem, aby upewnić się, że nie masz żadnych problematycznych materiałów w tym, co przekazujesz użytkownikowi końcowemu? Kto poniesie tego koszty?” ostrzegł Mike McIntyre, dyrektor ds. zarządzania oprogramowaniem w firmie Na innowacje, który zaleca statystyczną bazę danych do dokładnej oceny porównawczej podczas automatycznej klasyfikacji defektów.

Warpage

Jednym z najgorszych skutków stresu jest wypaczenie. Może być zaskakujące, że wypaczenie może być trudne do wykrycia, ale efekt nie zawsze jest tak oczywisty, jak mogłoby się wydawać. Wypaczenie powoduje niewielkie różnice w współpłaszczyznowości między chipem a podłożem, powodując, że niektóre mikrouderzenia nie łączą się w wystarczającym stopniu z podkładkami poniżej, awaria nazywana niemoczeniem.

„Weźmy na przykład zaawansowany procesor o grubości od 50 do 60 mm” — powiedział Chen. „Ze względu na duży rozmiar trudno jest go przetwarzać bez żadnych wypaczeń. Niemniej jednak, jeśli narzędzie do mocowania matrycy jest dostrojone w środku okna procesu, może przejść kontrolę i być produkowane z dużą wydajnością. Problem polega na tym, że tolerancja może być bardzo wąska. Gdy tylko trochę przechylisz matrycę na górze wypaczenia, masz problemy z wilgocią”.

Co gorsza, jeśli dzieje się to przy odstępach wypukłości w zakresie 50 µm (rozmiar wypukłości ̴35 µm), wyobraź sobie problemy, gdy wymiary wypukłości dalej się zmniejszają. Jest to już problem dla przemysłu motoryzacyjnego, ponieważ zbliża się do następnej generacji w latach 2023-2024. Krytyczne przejście nastąpi wokół węzła 28 nm, powiedział Chen.

Ryc. 1 Narzędzia do mocowania matrycy mają bardzo wąskie okno procesu przechylania matrycy w przypadku wypaczenia. źródło: Bruker

Nie nawilża

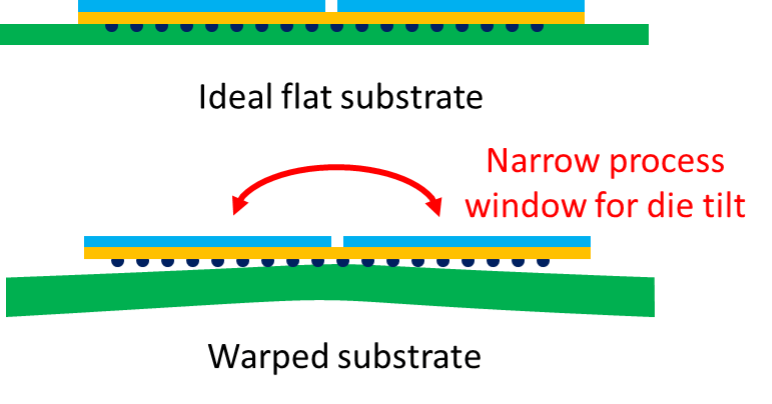

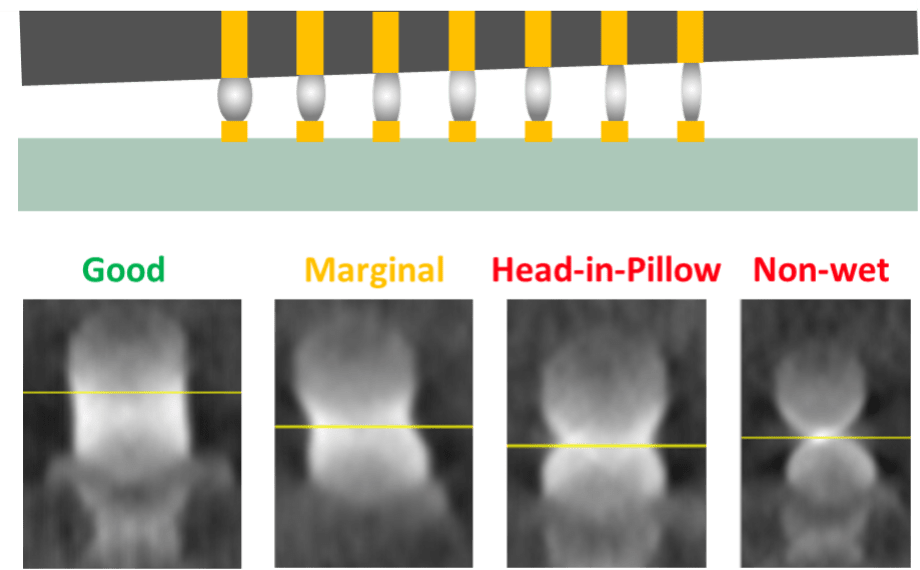

„Bez wilgoci” to szerokie pojęcie obejmujące kilka problemów, które mogą wystąpić w przypadku uderzeń lutowniczych, z których większość jest frustrująco subtelna. Ponieważ lut często występuje w stanie płynnym, proces jego nakładania został nazwany „zwilżaniem”. Słabe łącza nazywane są „niemokrymi”, które stają się coraz większym wyzwaniem w mniejszych węzłach z cieńszymi połączeniami.

Niezamoczone często wymykają się typowym procesom przesiewania, tylko po to, by pojawić się później jako zwrócone chipy (RMA). Pierwotne przyczyny mogą być termiczne, mechaniczne lub kombinowane, takie jak cykle termiczne w samochodzie, który również porusza się po nierównym terenie. Skumulowany efekt może zapewnić wystarczające obciążenie termiczno-mechaniczne, aby zerwać kontakt.

Istnieją dodatkowe pseudonimy, które opisują określone typy problemów. Zamiast gładkiego, kolumnowego kształtu dobrego połączenia, w przypadku wady „głowa w poduszce” jedna kulka wydaje się zapadać w drugą, jak głowa na poduszce.

„Nadal kontaktuje się, więc test elektryczny może być dobry, ale widać, że jest bardzo delikatny” — powiedział Chen, wskazując zdjęcie rentgenowskie głowy w poduszce. „Gdy tylko wystąpi naprężenie termiczne lub mechaniczne, może się całkowicie zepsuć. Nawet jeśli styk nie jest mokry, cienkie połączenie prowadzi do wysokiej rezystancji, nieoptymalnej wydajności i prawdopodobnie nie będzie trwać długo. Otwarty, nie mokry w ogóle nie zadziała. W typowym scenariuszu z pochyleniem matrycy widoczne jest przejście od dobrze uformowanych nierówności do niemoczonych”.

Krytycznym problemem są ukryte defekty — połączenia, które są wystarczająco funkcjonalne, aby pomyślnie przejść test elektryczny, ale zawodzą w terenie.

Ryc. 2 Stopniowe przejście od dobrych wypukłości do niezwilżonych w przypadku przechylenia matrycy. źródło: Bruker

„Jest to obecnie duży problem z wieloma typami urządzeń ze względu na skutki stresu termicznego” – powiedział Chen. „Jeden klient miał produkt, który przeszedł kontrolę e-testu i został wysłany. Niestety, mieli wiele RMA z powodu awarii niezmoczonych, które rozwinęły się później”.

Niektóre firmy rozwiązują ten problem poprzez boleśnie żmudne kontrole ręczne. Niestety, każde badanie człowieka wiąże się ze zmęczeniem operatora, zwłaszcza gdy egzaminatorzy próbują wykryć subtelne błędy podczas wielogodzinnej zmiany.

Pozytywną stroną są teraz zautomatyzowane podejścia do kontroli, takie jak narzędzia rentgenowskie, których można używać w trybie inline. „Istnieje duża siła napędowa w kierunku szybkiej, w pełni zautomatyzowanej inspekcji, aby osiągnąć <100 dppb, szczególnie w przemyśle motoryzacyjnym” — powiedział Chen.

Stamtąd staje się to bardziej skomplikowane. „Warto zauważyć, że lutowie, winowajca wielu niemokrych, również podlega elektromigracji” – powiedział Tom Marinis, główny członek personelu technicznego laboratorium w Draper. „Jeśli gęstość prądu w połączeniu między chipem a podłożem jest przez pewien czas zbyt wysoka dla określonego lutu, ponieważ temperatura topnienia lutu może być stosunkowo niska w porównaniu z temperaturą roboczą urządzenia, można uzyskać migrację atomów i faktycznie tworzą puste przestrzenie i ostatecznie otwierają połączenie”.

Marinis ostrzegł, że komercyjne narzędzia do modelowania na poziomie płytki drukowanej urządzenia nie są wystarczająco dojrzałe, aby konsekwentnie ostrzegać o potencjalnych problemach z elektromigracją, dlatego ważne jest, aby nadal przeprowadzać przyspieszony test starzenia.

Wnioski

Ostatecznie wykrywanie problemów z niezawodnością ukrytych defektów będzie wymagało wyższej metrologii próbkowania, która jest wrażliwa na przesunięcie matrycy, obrót, wysokość, nachylenie i inne parametry. Będzie to również wymagało większego polegania na modelowaniu wielofizycznym, aby spróbować przewidzieć i rozwiązać potencjalne problemy przed rozpoczęciem produkcji. A ponieważ przemysł półprzewodnikowy i motoryzacyjny nadal się przenikają, stawka jest o wiele większa niż tylko RMA.

„Koszt awarii rośnie wykładniczo, ponieważ ukryte usterki przechodzą z urządzeń na moduły i samochody, co może zagrażać życiu ludzi” — powiedział Chen. Właśnie dlatego producenci chipów tworzą całościowe rozwiązania, które łączą projektowanie, kontrolę i testowanie, aby lepiej wykrywać ukryte usterki.

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- Platoblockchain. Web3 Inteligencja Metaverse. Wzmocniona wiedza. Dostęp tutaj.

- Źródło: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- przyśpieszony

- Stosownie

- precyzja

- dokładny

- Osiągać

- aktywny

- faktycznie

- dodatek

- Dodatkowy

- adresowanie

- zaawansowany

- Starzenie się

- Alarm

- Wszystkie kategorie

- pozwala

- już

- Chociaż

- zawsze

- analiza

- i

- Inne

- przewidywać

- odpowiedni

- aplikacje

- Stosowanie

- podejście

- awanse

- POWIERZCHNIA

- obszary

- na około

- Montaż

- oszacowanie

- powiązany

- dołączać

- zautomatyzowane

- motoryzacyjny

- Przemysł motoryzacyjny

- Łazienka

- piłka

- na podstawie

- podstawa

- Niedźwiedź

- bo

- stają się

- staje

- zanim

- za

- jest

- poniżej

- BEST

- Zakład

- Ulepsz Swój

- pomiędzy

- Poza

- Duży

- większe

- Bit

- przerwa

- szeroki

- budżet

- wybudowany

- wbudowany

- biznes

- rozwój biznesu

- nazywa

- Może uzyskać

- wózek

- samochody

- walizka

- zapasy

- Spowodować

- Przyczyny

- spowodowanie

- Centrum

- CFD

- wyzwanie

- zakwestionowany

- wyzwania

- wyzwanie

- duża szansa,

- Zmiany

- charakteryzować

- chen

- żeton

- Frytki

- wybory

- klasyczny

- klasyfikacja

- połączenie

- kombinacje

- połączyć

- połączony

- łączenie

- jak

- handlowy

- wspólny

- Firmy

- w porównaniu

- całkowicie

- kompleks

- skomplikowane

- składnik

- Troska

- Warunki

- Skontaktuj się

- połączenie

- połączenia

- Rozważać

- skontaktuj się

- kontynuować

- rdzeń

- rogi

- Koszty:

- mógłby

- pokrycie

- Stwórz

- stworzony

- tworzy

- Tworzenie

- krytyczny

- Aktualny

- Obecnie

- klient

- Klientów

- tnący

- dane

- Baza danych

- czynienia

- gęstość

- opisać

- Wnętrze

- projekty

- szczegółowe

- rozwijać

- rozwinięty

- oprogramowania

- urządzenie

- urządzenia

- Umierać

- Różnice

- różne

- Trudność

- cyfrowy

- cyfrowy bliźniak

- Wymiary

- kierować

- bezpośrednio

- Dyrektor

- robi

- nie

- na dół

- sukiennik

- kierowca

- dubbingowane

- podczas

- dynamika

- Wcześnie

- efekt

- ruchomości

- efektywność

- starania

- Elektronika

- nacisk

- Inżynieria

- dość

- zapewnić

- sprzęt

- Błędy

- szczególnie

- itp

- Eter (ETH)

- Parzyste

- ostatecznie

- wszystko

- przykład

- wykonawczy

- ekspansja

- spodziewany

- doświadczony

- wyjaśnione

- zbadane

- wykładniczo

- niezwykle

- FAIL

- Brak

- najszybszy

- zmęczenie

- Korzyści

- facet

- kilka

- pole

- Figa

- Postać

- W końcu

- Znajdź

- znalezieniu

- i terminów, a

- pływ

- Nasz formularz

- znaleziono

- od

- frustrująco

- funkcjonalny

- dalej

- generacja

- otrzymać

- Goes

- będzie

- dobry

- stopniowy

- Rozwój

- Rośnie

- Prowadzenie

- Ciężko

- głowa

- wysokość

- pomoc

- pomaga

- Wysoki

- wyższy

- wysoko

- holistyczne

- Ufnie

- HOT

- W jaki sposób

- How To

- HTTPS

- człowiek

- Hybrydowy

- Oddziaływania

- ważny

- in

- Włącznie z

- Zwiększać

- wzrastający

- przemysłowa

- przemysł

- początkowy

- zamiast

- instrument

- integracja

- Wprowadzenie

- śledztwo

- odosobniony

- problem

- problemy

- IT

- samo

- Uprzejmy

- laboratorium

- duży

- na dużą skalę

- większe

- Nazwisko

- warstwa

- nioski

- prowadzić

- prowadzący

- Wyprowadzenia

- Doprowadziło

- poziom

- biblioteki

- Prawdopodobnie

- linki

- Ciecz

- Zyje

- długo

- Partia

- niski

- utrzymać

- robić

- Dokonywanie

- i konserwacjami

- kierownik

- podręcznik

- zrobiony fabrycznie

- wiele

- mapa

- Mario

- dopasowywanie

- materiał

- materiały

- dojrzały

- Maksymalna szerokość

- znaczy

- Pomiary

- zmierzenie

- mechaniczny

- członek

- Przemysł metalowy

- metoda

- metodologie

- Metryka

- Metrologia

- może

- migracja

- mieszać

- modelowanie

- moduł

- Moduły

- jeszcze

- większość

- porusza się

- wielokrotność

- nano

- koniecznie

- potrzebne

- ujemny

- Niemniej jednak

- Nowości

- Nowe technologie

- aktualności

- Następny

- węzeł

- węzły

- oczywista

- oferuje

- ONE

- trwający

- koncepcja

- operacyjny

- operator

- optymalizacja

- Opcje

- zamówienie

- Inne

- pakiet

- Pakiety

- opakowania

- Ból

- parametry

- szczególny

- szczególnie

- minęło

- Ludzie na

- wykonać

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- okres

- faza

- fizyczny

- Stanowiska

- plato

- Analiza danych Platona

- PlatoDane

- Grać

- gracze

- punkt

- zwrotnica

- polimery

- teczka

- pozytywny

- możliwy

- potencjał

- praktyka

- obecność

- prezydent

- zapobieganie

- Główny

- Wcześniejszy

- prawdopodobnie

- sonda

- Problem

- problemy

- wygląda tak

- procesów

- Procesor

- Produkt

- zarządzanie produktem

- Produkcja

- Program

- dowód

- prawidłowo

- niska zabudowa

- prototyp

- zapewniać

- pod warunkiem,

- położyć

- R & D

- zasięg

- szybki

- real

- niedawny

- zaleca

- zmniejszyć

- zmniejsza

- refleksja

- stosunkowo

- niezawodność

- poleganie

- odnowiony

- wymagać

- Wymaga

- Badania naukowe

- badania i rozwój

- dalsze

- wynikły

- Efekt

- Ryzyko

- ryzyko

- role

- korzeń

- run

- Powiedział

- mówią

- waga

- skanowanie

- scenariusz

- pokaz

- sekund

- wydaje

- segment

- wybór

- Semiconductor

- senior

- wrażliwy

- kilka

- Shadow

- Shape

- przesunięcie

- PRZESUNIĘCIE

- wysłane

- Short

- pokazać

- Signal

- znaczący

- znacznie

- symulacja

- Rozmiar

- rozmiary

- mały

- mniejszy

- So

- Tworzenie

- Rozwiązania

- kilka

- Wkrótce

- Źródło

- specyficzny

- Spektroskopia

- Spot

- Personel

- STAGE

- etapy

- stawka

- początek

- Stan

- statystyczny

- Nadal

- stres

- strukturalny

- Struktura

- przedmiot

- udany

- taki

- zaskakujący

- Techniczny

- Techniki

- Technologies

- test

- Testowanie

- Połączenia

- Strefa

- ich

- Tam.

- termiczny

- rzecz

- rzeczy

- tysiące

- Przez

- Rzucanie

- czas

- czasy

- do

- razem

- tolerancja

- także

- narzędzie

- narzędzia

- Top

- w kierunku

- przejście

- Zaufaj

- SKRĘCAĆ

- typy

- typowy

- zrozumieć

- zbliżających

- Aktualizacja

- posługiwać się

- Użytkownik

- różnorodny

- Naprawiono

- Wiceprezes

- widoczny

- znane

- Co

- który

- Podczas

- KIM

- będzie

- bez

- Praca

- najgorszy

- by

- rentgenowski

- plony

- Twój

- zefirnet