W terminologii układów scalonych spadek to spadek napięcia występujący w obwodzie. Jest to zjawisko dobrze znane i może wystąpić z następujących powodów. Zasilanie spada poniżej zakresu roboczego, dla którego chip został zaprojektowany, co powoduje spadek. Elementy przewodzące pobierają więcej prądu, niż zostały zaprojektowane, co powoduje opadanie. Czasami zakłócenia sygnału lub szumy w zasilaczu mogą również powodować wahania napięcia, powodując spadek.

Zapadnięcia mogą mieć wpływ na działanie obwodu. Jednym z takich skutków jest zmniejszona wydajność chipa, prowadząca do wydłużenia czasu przetwarzania. Poniżej przedstawiono niektóre z poważniejszych i/lub katastrofalnych skutków. Układ może pobierać więcej prądu, aby utrzymać poziom wydajności, co prowadzi do zwiększonego zużycia energii i rozpraszania ciepła. Może to prowadzić do skrócenia żywotności chipa, a w poważnych przypadkach do całkowitej awarii chipa z powodu zmian w konfiguracji i trzymaniu. Zawieszenia mogą również powodować uszkodzenie danych lub błędy w wynikach. Jest to bardzo poważny problem w zastosowaniach, w których zależy od dokładności i niezawodności chipa.

Oczywiście zjawisko opadania jest brane pod uwagę przy projektowaniu chipów i systemów. Najbardziej powszechnymi metodami łagodzenia spadków są oddzielenie zasilania, regulacja napięcia, optymalizacja obwodów i zarządzanie energią na poziomie systemu. Warunki i środowisko operacyjne, w którym chip będzie działał, są dokładnie brane pod uwagę przy projektowaniu rozwiązań łagodzących opadanie.

Problemy współczesne

W miarę jak SoC stają się coraz bardziej złożone, problemy z opadaniem również mogą stać się dość złożone. Projekt SoC musi zostać zoptymalizowany pod kątem wydajności, mocy, kosztów, kształtu itp., a także zoptymalizowany pod kątem łagodzenia oparzeń. Czasami te cele optymalizacyjne mogą ze sobą konkurować i działać przeciwstawnie, w związku z czym konieczne jest dokonanie kompromisu. Na przykład architekci SoC mogą podnieść napięcie robocze, dodając margines, aby ominąć lokalne i globalne spadki, ale wzrost ten kwadratowo zwiększa moc. Alternatywnie projektanci mogą dostosować generację zegara do opadania, co sprawia, że wydajność jest funkcją czasu przełączania generacji zegara.

W rezultacie duże układy SoC w centrum obliczeniowym i przestrzeni AI są szczególnie podatne na spadki wydajności. Obciążenia klientów są bardzo zróżnicowane i dynamiczne, co prowadzi do znacznych wahań w zakresie przełączania i poboru prądu. Oczywiście systemy nie mogą pozwolić sobie na pozostawienie problemów z zawieszaniem się bez rozwiązania. Potencjalne ryzyko wynikające z niedokładnego sygnału wyjściowego lub katastrofalnej awarii chipa jest zbyt wysokie w przypadku dzisiejszych systemów i aplikacji.

Lokalne problemy z opadaniem

Akceleratory specyficzne dla aplikacji są szeroko stosowane w połączeniu z procesorami ogólnego przeznaczenia, aby zapewnić wydajność i energooszczędność wymaganą w dzisiejszych wymagających środowiskach komputerowych. Jednak te akceleratory, a także rosnąca liczba rdzeni i asymetryczny charakter obciążeń, zwiększają ryzyko lokalnych spadków napięcia. Te zlokalizowane spadki napięcia są wynikiem nagłego wzrostu aktywności przełączania i mogą powodować przejściowe zakłócenia i potencjalne awarie w trybie misji.

W przypadku wystąpienia lokalnego zaniku, wpływ można złagodzić poprzez dynamiczne skalowanie częstotliwości. Osiąga się to poprzez regulację taktowania obwodu za pomocą programowalnego zegara. Programowalny zegar umożliwia dynamiczną regulację częstotliwości zegara i taktowania w oparciu o bieżące warunki pracy obwodu.

Movellus ułatwia radzenie sobie z lokalnymi opadami

Movellus, wiodący dostawca systemów cyfrowych IP, opracował rodzinę produktów Aeonic Generate, aby eliminować lokalne spadki. Portfolio Movellus Aeonic oferuje adaptacyjne rozwiązania taktowania, które zapewniają szybką reakcję na spadek. W portfolio znajduje się adaptacyjny układ taktowania. Elementy konstrukcyjne zbudowane są z syntezowalnego Verilogu, co czyni je wewnętrznie elastycznymi. Rozwiązania są konfigurowalne, skanowalne i przenośne dla szerokiej gamy zaawansowanych aplikacji SoC.

Rodzina produktów Aeonic Generate jest także znacznie mniejsza od tradycyjnych rozwiązań analogowych. W rezultacie projektanci mogą stworzyć instancję IP z wymaganą szczegółowością bez znaczącego wpływu na obszar. Dodatkowo, w miarę jak projekty przechodzą na bardziej drobną geometrię procesu, obszar Aeonic Generate stale się skaluje, co czyni go idealnym rozwiązaniem dla przyszłych projektów.

Kilka przypadków użycia

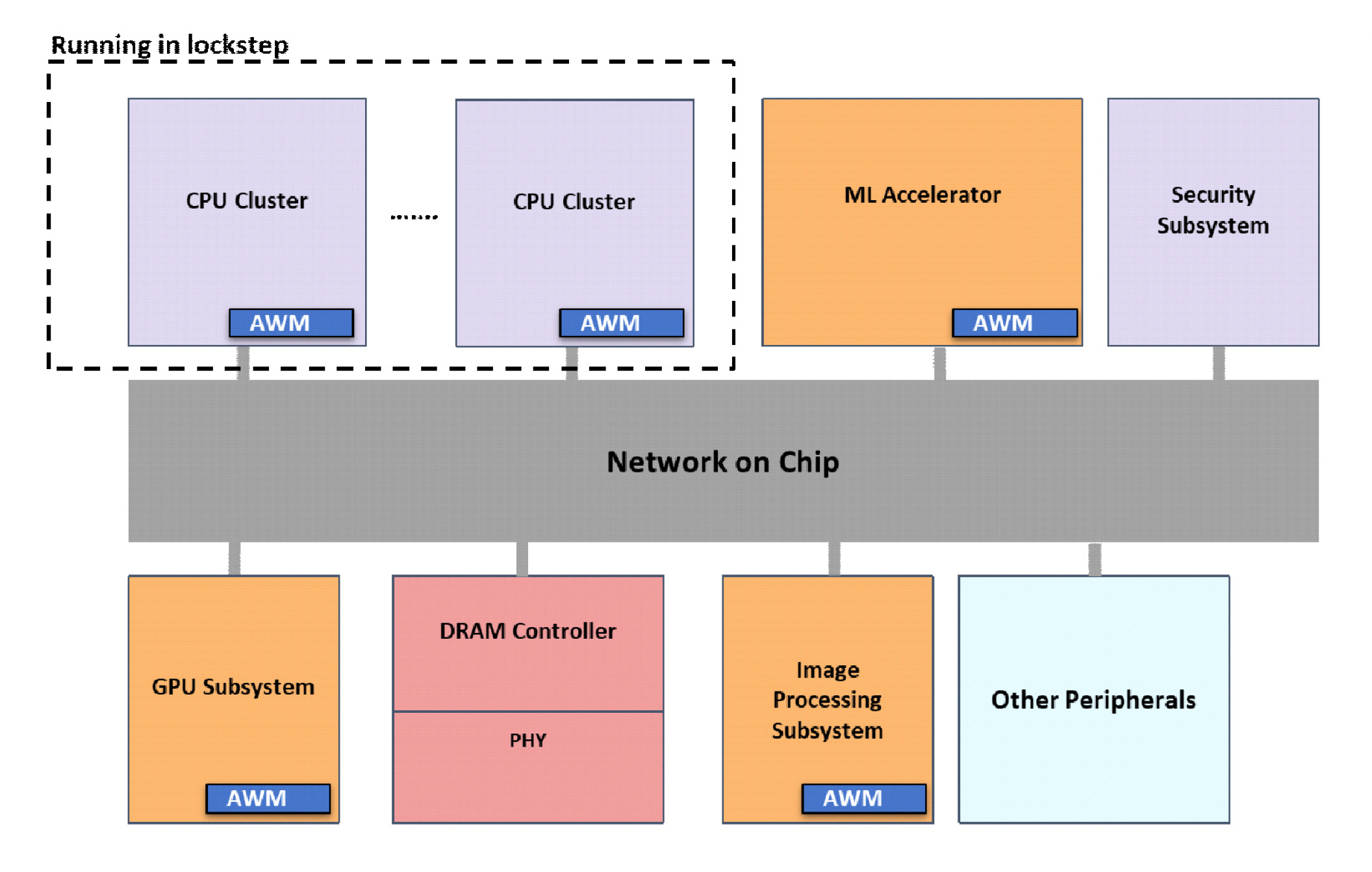

Poniższy rysunek z Movellus przedstawia przykładową architekturę procesora ADAS z platformą Aeonic Generate AWM do obsługi zlokalizowanego traconego sygnału. Architekt powinien sparować moduł AWM z podblokiem lub akceleratorem specyficznym dla aplikacji, aby reagować na zlokalizowane spadki spowodowane obciążeniem pracą w ciągu pięciu cykli zegara z pozbawionymi zakłóceń i szybkimi zmianami częstotliwości. Takie podejście zapewnia niezawodne i wydajne rozwiązanie pozwalające sprostać wyzwaniom związanym z lokalnymi przerwami w sieciach ADAS, 5G i rynkach sieci centrów danych.

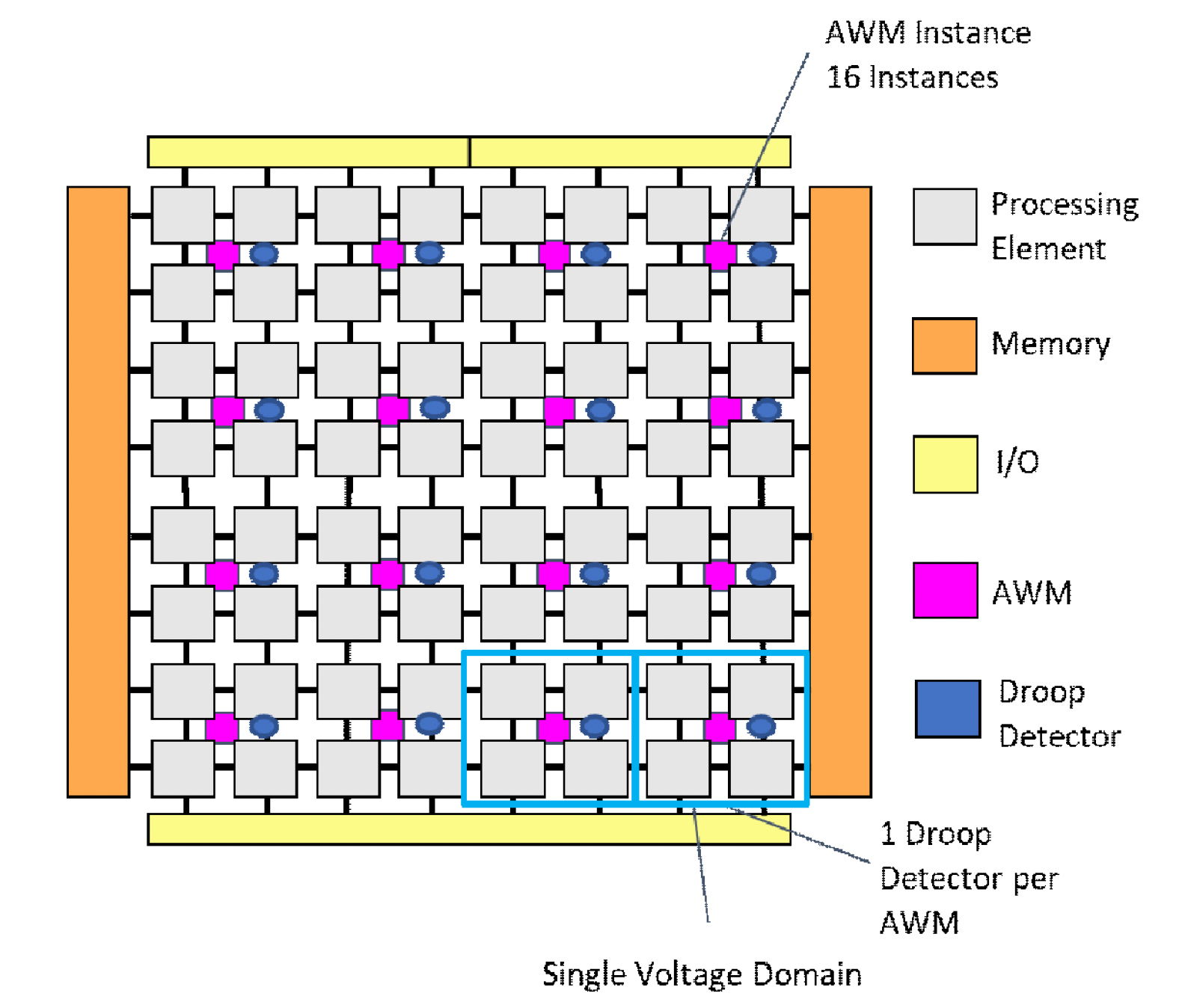

Poniższy rysunek z Movellus przedstawia przykładową architekturę morza procesorów SoC z Aeonic Generate do obsługi zlokalizowanych obniżeń. Architekt sparowałby moduł Aeonic Generate AWM z detektorem spadków dla klastra procesorów i powiązanej domeny napięcia, aby szybko reagować na zlokalizowane spadki spowodowane obciążeniem pracą. Dzięki temu projektanci mogą zapewnić zlokalizowaną i niezależną reakcję na spadek wydajności bez zmiany wydajności sąsiednich klastrów procesorów.

Podsumowanie

W heterogenicznych układach SoC zawierających akceleratory specyficzne dla danego zastosowania mogą wystąpić zlokalizowane spadki napięcia. Te spadki mogą prowadzić do usterek synchronizacji, usterek przejściowych i awarii trybu misji w ADAS, sieciach centrów danych i aplikacjach 5G. Architekci systemów mogą wdrożyć taktowanie adaptacyjne, aby reagować na te spadki i łagodzić ich skutki.

Rodzina wysokowydajnych produktów IP do generowania zegara Movellus™ Aeonic Generate Adaptive Workload Module (AWM) jest częścią architektury Aeonic Intelligent Clock Network™. Więcej informacji można znaleźć w witrynie Movellus Strona Aeonic Generate™ AWM.

Przeczytaj także:

Zalety wielkoskalowych domen synchronicznego taktowania w projektach układów AI

Nadszedł czas na sieci inteligentnego zegara

Korzyści w zakresie wydajności, mocy i obszaru (PPA) dzięki inteligentnym sieciom zegarowym

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- Platoblockchain. Web3 Inteligencja Metaverse. Wzmocniona wiedza. Dostęp tutaj.

- Źródło: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :Jest

- 5G

- a

- akcelerator

- akceleratory

- precyzja

- osiągnięty

- działalność

- przystosować

- ADA

- dodatek

- do tego

- adres

- adresowanie

- Skorygowana

- zaawansowany

- AI

- pozwala

- i

- aplikacje

- podejście

- architektura

- SĄ

- POWIERZCHNIA

- AS

- powiązany

- At

- na podstawie

- BE

- stają się

- poniżej

- Korzyści

- Blokować

- Bloki

- Budowanie

- wybudowany

- by

- CAN

- Może uzyskać

- nie może

- ostrożnie

- Etui

- katastrofalny

- Spowodować

- Centrum

- wyzwania

- żeton

- Frytki

- zegar

- Grupa

- wspólny

- rywalizować

- kompletny

- kompleks

- obliczać

- computing

- Warunki

- wynagrodzenie

- za

- konsumpcja

- ciągły

- Korupcja

- Koszty:

- mógłby

- Przeciwdziałać

- Para

- kurs

- Aktualny

- klient

- Cykle

- dane

- Centrum danych

- Datacenter

- dzień

- dostarczyć

- wymagający

- Wnętrze

- zaprojektowany

- projektanci

- projektowanie

- projekty

- rozwinięty

- cyfrowy

- dystrybuowane

- inny

- domena

- domeny

- sporządzony

- Spadek

- Krople

- dynamiczny

- dynamicznie

- każdy

- efektywność

- wydajny

- Elementy

- Środowisko

- środowiska

- Błędy

- itp

- przykład

- Brak

- Spada

- członków Twojej rodziny

- Postać

- elastyczne

- Wahania

- następujący

- W razie zamówieenia projektu

- Nasz formularz

- Częstotliwość

- od

- funkcjonować

- przyszłość

- ogólny cel

- Generować

- generacja

- otrzymać

- Globalne

- Go

- Gole

- zdarzyć

- dzieje

- Have

- Wysoki

- wysoka wydajność

- przytrzymaj

- HTTPS

- idealny

- Rezultat

- Oddziaływania

- wdrożenia

- in

- niedokładny

- obejmuje

- Zwiększać

- wzrosła

- Zwiększenia

- wzrastający

- niezależny

- Informacja

- zintegrowany

- integracja

- Inteligentny

- wewnętrznie

- IP

- problem

- problemy

- IT

- duży

- na dużą skalę

- prowadzić

- prowadzący

- poziom

- odpowiedzialność

- życie

- miejscowy

- dłużej

- zrobiony

- utrzymać

- WYKONUJE

- Dokonywanie

- i konserwacjami

- Margines

- rynki

- Maksymalna szerokość

- metody

- Złagodzić

- łagodzenie

- łagodzenie

- moduł

- Moduły

- jeszcze

- większość

- ruch

- Natura

- wymagania

- sieć

- sieci

- Hałas

- szczególnie

- numer

- of

- Oferty

- on

- ONE

- operacyjny

- operacje

- optymalizacja

- zoptymalizowane

- optymalizacji

- Inne

- wydajność

- część

- jest gwarancją najlepszej jakości, które mogą dostarczyć Ci Twoje monitory,

- wykonywania

- zjawisko

- Platforma

- plato

- Analiza danych Platona

- PlatoDane

- teczka

- Post

- potencjał

- power

- Zasilacz laboratoryjny

- wygląda tak

- przetwarzanie

- Procesor

- Procesory

- Produkty

- dostawca

- zapewnia

- podnieść

- zasięg

- szybki

- szybko

- Czytaj

- w czasie rzeczywistym

- Przyczyny

- Zredukowany

- Regulacja

- niezawodność

- rzetelny

- wymagany

- Odpowiadać

- odpowiedź

- dalsze

- wynikły

- Rosnąć

- Ryzyko

- run

- Skala

- skalowaniem

- SEA

- poważny

- ustawienie

- ciężki

- Przesunięcia

- Targi

- Signal

- znaczący

- znacznie

- mniejszy

- mądry

- rozwiązanie

- Rozwiązania

- kilka

- Typ przestrzeni

- taki

- nagły

- Dostawa

- wsparcie

- wrażliwy

- system

- systemy

- Tandem

- Technologia

- terminologia

- że

- Połączenia

- Strefa

- ich

- Im

- Te

- Przez

- czas

- czasy

- wyczucie czasu

- do

- dzisiaj

- także

- tradycyjny

- posługiwać się

- bardzo zróżnicowany

- przez

- Napięcie

- DOBRZE

- znane

- który

- szeroki

- Szeroki zasięg

- szeroko

- będzie

- w

- w ciągu

- bez

- by

- zefirnet