To było z powrotem w 1991 że Cadence jako pierwsza ogłosiła nazwę produktu Virtuoso, a my, 32 lata później, produkt żyje i ma się całkiem nieźle. Steven Lewis z Cadence przekazał mi aktualne informacje na temat czegoś nowego, co nazywają Studio Wirtuozi chodzi o niestandardowy projekt układu scalonego dla prawdziwego świata. W ciągu tych 32 lat widzieliśmy, jak proces półprzewodnikowy przebiega zgodnie z prawem Moore’a od 600 nm przy użyciu planarnej matrycy CMOS, aż do ery FinFET poniżej 22 nm, osiągając GAA w węźle 3 nm. Najwyraźniej wymagania dotyczące narzędzi EDA uległy zmianie, ponieważ mniejsze węzły wprowadziły nowe efekty fizyczne, które należało modelować i symulować, aby zapewnić pierwszy sukces krzemowy.

Celem Cadence Virtuoso Studio jest pomaganie projektantom układów scalonych w podejmowaniu współczesnych wyzwań w sześciu obszarach:

- Zwiększona złożoność procesu

- Obsługa 10,000 XNUMX symulacji obwodów

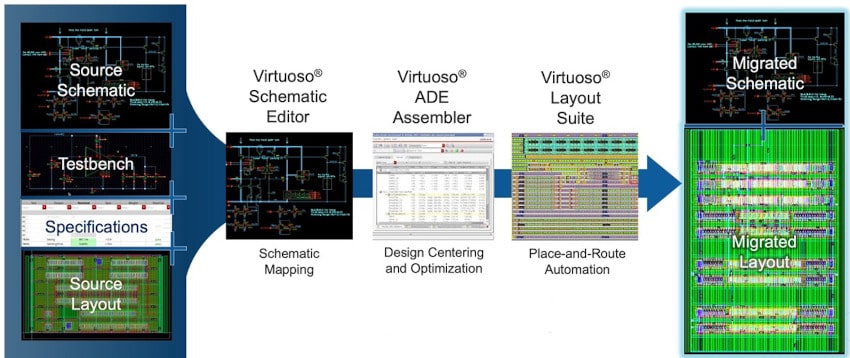

- Automatyzacja projektowania i migracja obwodów

- Integracja heterogeniczna

- AI

- Podpisanie, weryfikacja i analiza w projekcie

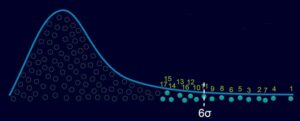

Połączenia Wirtuoz ADE (Analog Design Environment) umożliwia inżynierom obwodów eksplorację projektów analogowych, mieszanych i RFIC poprzez przechwytywanie schematów i symulację obwodów. Architektura Virtuoso ADE została ulepszona w celu lepszej kontroli zadań, zmniejszenia zużycia pamięci RAM i przyspieszenia symulacji dzięki wykorzystaniu chmury. Na przykład pamięć RAM wymagana do uruchomienia Spectre w 10,000 420 symulacjach została zmniejszona z 18 MB do zaledwie 420 MB na potrzeby monitorowania symulacji, podczas gdy ocena wyrażeń została zmniejszona z 280 MB pamięci RAM do zaledwie XNUMX MB.

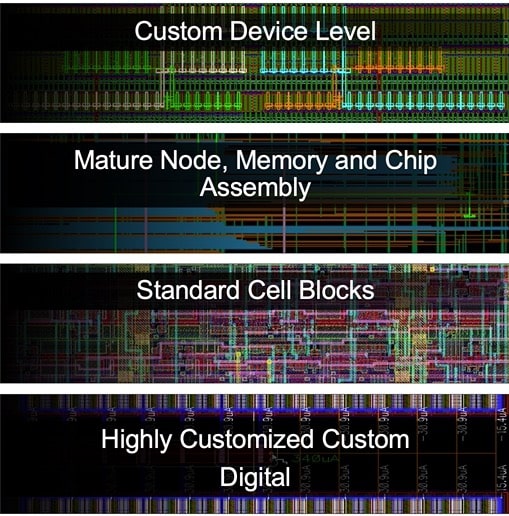

Aktualizacje do Wirtuozowski apartament z układem obejmują cztery opcje technologii lokalizacji i tras, każda dostosowana do unikalnego zadania wykonywanego w środowisku Virtuoso:

Cztery technologie P&R

Przebiegi DRC i LVS stanowią część weryfikacji fizycznej, a uruchamianie ich w trybie wsadowym, naprawianie i powtarzanie, prowadzi do długich harmonogramów rozwoju. Weryfikacja w projekcie umożliwia interaktywne wykorzystanie DRC i LVS podczas pracy nad układem układu scalonego, dzięki czemu informacje zwrotne na temat tego, co należy zmienić, są szybko podkreślane, co przyspiesza produktywność. Projektant układu korzystający z pakietu Virtuoso Layout Suite korzysta z weryfikacji w projekcie za pomocą narzędzia Pegasus Technologia DRK i LVS.

Chiplety, opakowania 2.5D i 3D obejmują tradycyjnie odrębne dziedziny projektowania PCB, obudów i układów scalonych. Virtuoso Studio umożliwia współprojektowanie i weryfikację pakietów, modułów i układów scalonych poprzez:

Patrząc w niedaleką przyszłość, można spodziewać się szczegółów na temat stosowania sztucznej inteligencji w celu automatycznego przejścia ze schematu analogowego do układu opartego na uczeniu maszynowym i specyfikacjach. Te automatycznie generowane układy próbne jeszcze bardziej przyspieszą bardzo pracochłonny proces. Drugim obszarem rozwoju AI do zastosowania jest problem migracji niestandardowego analogowego IP do nowego węzła procesowego. Czekać na dalsze informacje.

Pierwsi klienci Virtuoso Studio to m.in. firma Analog Devices zajmująca się wspólnym projektowaniem układów scalonych i obudów, najnowocześniejsze projekty konsumenckie układów scalonych w firmie MediaTek oraz migracja procesów oparta na sztucznej inteligencji w firmie Renesas.

Podsumowanie

Virtuoso Studio wprowadziło do wersji 23.1 kilka imponujących nowych funkcji, z których zespoły projektowe układów scalonych mogą zacząć korzystać, aby zwiększyć produktywność. Infrastruktura Virtuoso została zmieniona, aby sprostać wyzwaniom prawa Moore’a, symulacje obejmujące symulacje obwodów 10,000 2.5 są praktyczne, obsługiwane jest wspólne projektowanie RFIC i modułu 3D/XNUMXD, weryfikacja DRC/LVS w projekcie zajmuje znacznie mniej czasu, a sztuczna inteligencja jest stosowane do automatyzacji zadań analogowych.

Powiązane blogi

Udostępnij ten post przez:

- Dystrybucja treści i PR oparta na SEO. Uzyskaj wzmocnienie już dziś.

- Platoblockchain. Web3 Inteligencja Metaverse. Wzmocniona wiedza. Dostęp tutaj.

- Wybijanie przyszłości w Adryenn Ashley. Dostęp tutaj.

- Źródło: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :ma

- :Jest

- $W GÓRĘ

- 1

- 10

- 3d

- a

- O nas

- przyspieszenie

- AI

- Wszystkie kategorie

- pozwala

- wzdłuż

- i

- ogłosił

- stosowany

- architektura

- SĄ

- POWIERZCHNIA

- obszary

- AS

- At

- zautomatyzować

- automatycznie

- Automatyzacja

- z powrotem

- na podstawie

- BE

- być

- jest

- poniżej

- Korzyści

- Ulepsz Swój

- przyniósł

- by

- Kadencja

- wezwanie

- CAN

- zdobyć

- wyzwania

- zmiana

- wybory

- wyraźnie

- Chmura

- konsument

- kontrola

- zwyczaj

- Klientów

- dzień

- wymagania

- Wnętrze

- projektant

- projektanci

- projekty

- detale

- oprogramowania

- urządzenia

- robi

- domeny

- na dół

- każdy

- ruchomości

- Umożliwia

- Inżynierowie

- zapewnić

- Środowisko

- Era

- oceny

- przykład

- oczekiwać

- odkryj

- Korzyści

- informacja zwrotna

- i terminów, a

- Skupiać

- W razie zamówieenia projektu

- cztery

- od

- dalej

- przyszłość

- Go

- ręka

- Have

- pomoc

- tutaj

- Podświetlony

- W jaki sposób

- HTML

- HTTPS

- ICS

- imponujący

- in

- zawierać

- Infrastruktura

- interaktywne

- IP

- Praca

- jpg

- praca

- Prawo

- układ

- Wyprowadzenia

- nauka

- Chwytak

- długo

- maszyna

- uczenie maszynowe

- March

- Maksymalna szerokość

- Poznaj nasz

- migracja

- Moda

- moduł

- Moduły

- monitorowanie

- jeszcze

- Nazwa

- Blisko

- potrzebne

- Nowości

- Nowe funkcje

- węzeł

- węzły

- of

- on

- ONE

- pakiet

- Pakiety

- opakowania

- część

- fizyczny

- Miejsce

- plato

- Analiza danych Platona

- PlatoDane

- Post

- Praktyczny

- teraźniejszość

- Problem

- wygląda tak

- Produkt

- produktywny

- wydajność

- położyć

- szybko

- RAM

- osiągnięcie

- real

- Prawdziwy świat

- Zredukowany

- redukcja

- zwolnić

- wymagany

- Trasa

- run

- bieganie

- skalowaniem

- druga

- patrz szczegóły

- Semiconductor

- oddzielny

- Krzem

- symulacja

- SIX

- mniejszy

- So

- kilka

- coś

- rozpiętość

- Specyfikacje

- Widmo

- prędkość

- początek

- pobyt

- studio

- sukces

- apartament

- Utrzymany

- Brać

- trwa

- Zadanie

- zadania

- Zespoły

- Technologia

- że

- Połączenia

- ich

- Te

- Przez

- czas

- do

- narzędzie

- tradycyjnie

- próba

- wyjątkowy

- Aktualizacja

- Stosowanie

- posługiwać się

- Weryfikacja

- przez

- DOBRZE

- Co

- Podczas

- będzie

- w

- pracujący

- świat

- lat

- zefirnet