Nu een toenemend aantal bedrijven geïnteresseerd is in apparaten gebaseerd op de RISC-V ISA, en een groeiend aantal cores, accelerators en infrastructuurcomponenten beschikbaar wordt gesteld, hetzij commercieel, hetzij in open source-vorm, worden eindgebruikers geconfronteerd met een steeds moeilijkere uitdaging om ervoor te zorgen dat ze de beste keuzes maken.

Elke gebruiker zal waarschijnlijk een reeks behoeften en zorgen hebben die bijna gelijk zijn aan de flexibiliteit van het RISC-V-aanbod, en die veel verder gaan dan de traditionele PPA-metrieken op het gebied van veiligheid en beveiliging, of kwaliteitsoverwegingen. Te denken valt aan de aanpasbaarheid van het verificatieonderpand, waardoor de architectonische uitbreiding en de daarmee gepaard gaande noodzakelijke verificatie mogelijk wordt.

Traditioneel worden er drie niveaus van prototyping ingezet: virtuele prototypes, emulatie en FPGA-prototypes, inclusief hybriden daartussen. Elk platform wordt vervolgens voor verschillende doeleinden gebruikt, waaronder softwareverificatie, architecturale validatie, functionele verificatie van de hardware, prestatieanalyse en meer.

Terwijl de ontwerp- en software-ecosystemen voor RISC-V vaste voet aan de grond krijgen, lopen de configuratie- en verificatie-ecosystemen achter en vereisen ze dat er nieuwe technologie wordt gebouwd. Het is juist de flexibiliteit van RISC-V die enorme uitdagingen voor de verificatie met zich meebrengt, die verder gaan dan wat vereist is voor de verificatie van vaste processors. Het maakt ook de gezamenlijke ontwikkeling van hardware en software niet alleen mogelijk, maar ook noodzakelijk.

Co-ontwikkeling

In het verleden werd hardware geselecteerd en vervolgens software ontwikkeld om daarop te draaien. Bij RISC-V wordt de hardware vaak aangestuurd door software. “Het eerste dat u moet kiezen, is welke standaard RISC-V-opties u wilt”, zegt Simon Davidmann, oprichter en CEO van Imperas-software. “De RISC-V-functieset heeft momenteel 200 of 300 opties. Hoe weet u of uw algoritme baat zou hebben bij een drijvende-komma-eenheid, of SIMD, hardwarevermenigvuldigers of zelfs een vectorengine? Je moet uitzoeken welke hardwaremogelijkheden je nodig hebt en kunt betalen voor het type toepassing of de taak die je wilt dat de processor doet. Dat wordt op zichzelf al een hele uitdaging.”

Om dit soort afwegingen te kunnen maken, zijn prototypes nodig. “Als het doel van de ontwerper is om de prestaties en geschiktheid voor het doel te evalueren, dan is virtuele prototyping de enige haalbare keuze”, zegt Steve Roddy, CMO bij kwadraat. “Het bouwen van hardwareprototypes kost meer dan 10 tot 50 keer meer tijd dan het maken van een SystemC-model van een subsysteem of een volledige SoC. Het virtuele prototype van SystemC werkt over het algemeen snel genoeg om prestatievragen te beantwoorden, zoals hoeveel frames per seconde aan doorvoer ik kan halen met deze processorkern, of wat de piek- en gemiddelde bandbreedtevereiste is van functie X, binnen een acceptabele nauwkeurigheidsgrenzen.”

Het verkrijgen van de juiste nauwkeurigheid kan lastig zijn. “Het draait allemaal om nauwkeurigheid en jouw vermogen om een model heel snel te laten draaien”, zegt Frank Schirrmeister, vice-president voor oplossingen en bedrijfsontwikkeling bij Arteris-IP. “De juiste nauwkeurigheid wordt bepaald door wat je vraag ook vereist, en het genereren ervan is niet triviaal. Als u een ASIP-provider bent, kunt u deze genereren op basis van welke sjabloon u ook heeft. Afhankelijk van de vraag heb je misschien pijplijnnauwkeurigheid nodig, misschien heb je geheugennauwkeurigheid nodig, het hoeft niet volledig nauwkeurig te zijn, maar als je een CAD-afdeling erbij hebt betrokken, zijn ze te bang om de verkeerde vraag te beantwoorden.”

Maar nauwkeurigheid is een afweging ten opzichte van snelheid. “Hoewel sommige virtuele prototypes cyclusnauwkeurig zijn, draaien deze vaak te langzaam om de benodigde softwaredoorvoer te kunnen realiseren”, zegt Davidmann van Imperas. “De krachtigste virtuele prototypes zijn geen prestatiemotoren, omdat ze geen processorpijplijnen modelleren. Ze bekijken het vanuit softwareoogpunt, waarbij je het kunt compileren en op hardware kunt uitvoeren, en je de prestaties bij benadering kunt zien door te kijken naar het aantal instructies of geschatte timingschattingen. Dit zou voldoende moeten zijn om dit soort architectonische beslissingen te nemen.”

Vaak zijn er meerdere prototypes nodig. “Over het algemeen maken we prototypes om twee redenen”, zegt Venki Narayanan, senior directeur voor software en systeemtechniek binnen de FPGA-businessunit van Microchip Technology. “De ene is voor architecturale validatie om ervoor te zorgen dat we aan alle prestatiestatistieken en -vereisten en functionele validatie voldoen. De andere reden is de ontwikkeling van embedded software en firmware. We gebruiken verschillende niveaus van prototypingtechnieken, waarbij de meest voorkomende is dat we onze eigen FPGA's gebruiken om een emulatieplatform te ontwikkelen voor zowel architecturale als functionele validatie. We gebruiken ook architecturale modellen zoals QEMU om virtuele platforms te bouwen voor zowel prestatievalidatie als embedded software-ontwikkeling.”

Het aantal mogelijkheden groeit. “Er zijn veel manieren waarop bedrijven tegenwoordig prototypes maken met RISC-V”, zegt Mark Himelstein, CTO van RISC-V International. “Deze variëren van single board computers op makerniveau tot enterprise LINUX-compatibele boards. Emulatieomgevingen (zoals QEMU) stellen ontwikkelaars in staat vooruitgang te boeken met software voordat hun hardware compleet is, en er zijn overal kant-en-klare onderdelen, van embedded SoC's (van bedrijven als Espressif en Telink) tot FPGA's (van bedrijven als Microsemi) tot het komende Horse Creek-bord van Intel en SiFive.”

Het komt terug op de afweging tussen prestatie en nauwkeurigheid. “Fysieke prototypes vergen veel meer ontwerpinspanning, omdat je echte RTL verbindt en synthetiseert, maar ze leveren een veel grotere nauwkeurigheid en doorvoersnelheid”, zegt Roddy van Quadric. “Het kost moeite om een fysiek prototype in een FPGA-systeem op te zetten, of het nu van eigen bodem is of van de grote EDA-bedrijven. Maar het kan een orde van grootte sneller draaien dan een SystemC-model, en verschillende ordes van grootte sneller dan volledige simulatie op poortniveau. Ontwerpteams zullen doorgaans tijdens het IP-selectieproces overschakelen van C-gebaseerde modellen naar fysieke modellen voor zowel verificatie van het daadwerkelijke ontwerp na IP-selectie, als als een systeem-software-ontwikkelplatform.”

Als u eenmaal weet welke functies u in de hardware wilt hebben, kunt u kijken of iemand al een oplossing heeft gemaakt die aan de meeste van uw behoeften voldoet. "De kans is groot dat er, ondanks alle leveranciers die er zijn, een commerciële oplossing zal zijn die precies aansluit bij wat jij zoekt", zegt Davidmann. “Maar met RISC-V hoef je die oplossing niet zomaar te accepteren. Een aanzienlijk deel van de waarde van RISC-V is de vrijheid om het te veranderen, aan te passen en verschillende dingen toe te voegen die je wilt.”

Een implementatie selecteren

Er zijn veel manieren om een reeks functies te implementeren, zoals het aantal pijplijnfasen of speculatieve uitvoeringsfuncties. Ze hebben allemaal een andere afweging tussen kracht, prestaties en oppervlakte. "De ISA-variant, of het nu RISC-V, Arm, Xtensa van Cadence of ARC van Synopsys is, heeft niet echt invloed op de doelstellingen en afwegingen bij het modelleren en prototypen", zegt Roddy. “Een systeemarchitect moet vragen over SoC-ontwerpdoelen beantwoorden, ongeacht het merk processor. Op technisch niveau bevindt de RISC-V-bandwagon zich echt in een stabiele positie op de markt als het gaat om ondersteuning voor modellering en prestatieanalysetools. Er zijn talloze concurrerende kernleveranciers, elk met verschillende implementaties en processorfuncties. Als hoofdsysteem-CPU heeft deze niet de levensduur van een arm, en daarom hebben minder ecosysteemspelers in de EDA-wereld breed gevalideerde, kant-en-klare modelleringsondersteuning voor kant-en-klare RISC-V-kernen uit de variëteit van RISC-V-leveranciers. Als configureerbare, aanpasbare kern blijft de RISC-V-wereld achter op het niveau van instructiesetautomatisering dat Tensilica 25 jaar lang heeft opgebouwd. RISC-V heeft dus minder modelleringsondersteuning als kant-en-klare bouwsteen en minder automatisering om te gebruiken als platform voor experimenten met instructiesets.”

Maar dat is slechts één aspect van een implementatie dat beoordeeld moet worden. Wat is de kwaliteit ervan? Als u het wilt wijzigen, hoe valideert u het dan opnieuw?

Prestaties zijn het gemakkelijkst te beoordelen. “Dit is niet anders dan naar een traditionele processorleverancier gaan”, zegt Davidmann. “Ze zullen je vertellen dat deze kern je zoveel Dhrystones per watt geeft, ze zullen je de typische analytische gegevens van een processor geven, die zeggen hoe snel deze microarchitectuur werkt. Ze hebben al die gegevens, en iedereen die een licentie voor een processorkern in licentie neemt, zal bekend zijn met die gegevens en met hen gaan praten om die informatie op te halen. Ze zullen waarschijnlijk veel selecteerbare opties in hun gegevensblad hebben, en ze zullen zeggen: 'Als je deze optie inschakelt, krijg je dit of dat.' Je kunt het bekijken op het gegevensblad, op de websites van de leveranciers.”

Op dit niveau heeft u waarschijnlijk cyclusnauwkeurigheid nodig. "Ik zie dat de meeste mensen het in een emulator pompen en er voldoende gegevens doorheen halen om een redelijke beslissing te nemen", zegt Schirrmeister. “Ik zie dat niet snel overgaan op virtuele prototypes. Sommige bedrijven hebben het over FPGA-prototypes, waarbij je je eigen single board-oplossing hebt. Afhankelijk van de vraag die u moet beantwoorden, kunt u besluiten deze te configureren, te genereren en vervolgens in een FPGA te pompen om er meer gegevens doorheen te laten lopen, met de juiste softwareroutines erbovenop. De industrie beschikt over voldoende snelle toegang tot emulators en prototyping om dit mogelijk te maken. Het fundamentele probleem is dat je deze beslissing wilt nemen op basis van zo nauwkeurig mogelijke gegevens, maar dat je op het moment dat je die beslissing wilt nemen misschien niet over die nauwkeurige gegevens beschikt.”

Veel van deze prototypes moeten meer omvatten dan alleen de processor. “Virtuele platforms bieden de mogelijkheid om te integreren met andere externe fysieke hardwarefuncties, zoals geheugen en sensoren die in een echte omgeving werken”, zegt Narayanan van Microchip. “Hybride systemen kunnen virtuele platforms samenbrengen met fysieke prototypes voor andere externe functies. FPGA-emulatie en prototyping helpen bij het vinden van timinggerelateerde bugs, zoals raceomstandigheden, omdat dit cyclusnauwkeuriger is en externe functies sneller werken.”

Verificatie

Omdat het processorontwerp al lange tijd in eigen beheer is, bestaat er geen openbaar verificatie-ecosysteem voor het bouwen van een processor en vereisen de functies van RISC-V een veel flexibelere verificatieoplossing dan ooit in het verleden heeft bestaan. De creatie hiervan begint nog maar net te gebeuren.

“Er zijn sectorstatistieken zoals Dhrystones of CoreMark, zodat mensen de prestaties kunnen vergelijken”, zegt Davidmann. “Maar hoe kun je de verificatiekwaliteit vergelijken? Er moet een gelijk speelveld zijn, zodat elke leverancier kan zeggen: 'Dit is hoe wij het doen.' We hebben een aantal kwaliteitsstatistieken nodig die te maken hebben met verificatie.”

Dit is waar de open-sourcebeweging kan helpen. “Als je naar het RISC-V-ecosysteem kijkt, zie je een groot aantal zeer ervaren processorontwikkelaars”, zegt Schirrmeister. “Er zijn twee uitersten. Een daarvan is dat ik een kern van een leverancier krijg en als deze niet werkt, heb je een probleem met hen. Aan de andere kant heb ik totale vrijheid en doe ik alles zelf. Ergens tussen deze twee uitersten ontwikkelt zich een evenwicht. Je krijgt iets waarbij een bepaalde mate van verificatie wordt geleverd door je leverancier, en dan zijn de uitbreidingen je eigen verantwoordelijkheid.”

En dit is waar statistieken in beeld komen. “ISA-compatibiliteit is slechts de eerste trede op een ladder vol complexiteit die slechts een paar bedrijven hebben beklommen”, zegt Dave Kelf, CEO van Breker Verification Systems. “Prototyping is misschien wel de enige manier om een betrouwbare werking van de processor volledig te garanderen, maar het benutten van echte werklasten om deze prototypes aan te sturen, is nog maar een stap in de goede richting van echte processordekking. Dit staat op gespannen voet met de concurrentie-inspanningen van een open ISA die een versnelde ontwikkeling en time-to-market-problemen stimuleert.”

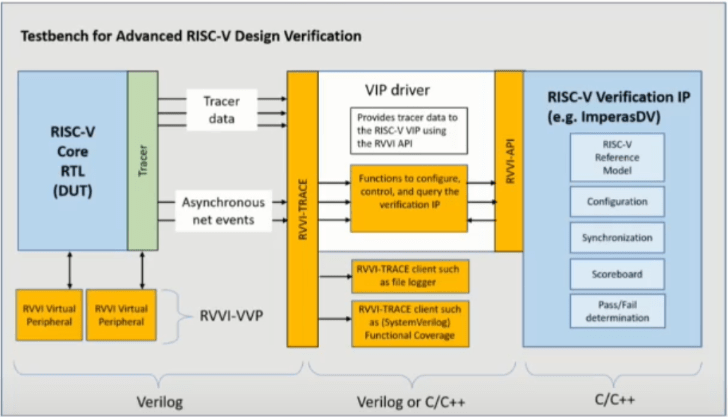

Maar wat zijn die statistieken? “In de OpenHW-kwaliteitsgroep proberen we uit te zoeken wat deze statistieken zouden moeten zijn”, zegt Davidmann. “Daar horen zaken als functionele dekking bij, want het zijn niet alleen simpele instructies. Voor een hoogwaardige processor heb je veel meer nodig dan dat. U heeft een verificatiemethode nodig, waarbij u erop kunt vertrouwen dat uw vergelijkingen met een referentie alles omvatten. Functionele dekking laat alleen zien dat u de test onder de knie heeft, maar dat moet gepaard gaan met een methodologie die vergelijkt met een of andere vorm van bekende referentie. We gaan foutinjectietechnologie toevoegen, zodat je kunt achterhalen of je testbank daadwerkelijk problemen detecteert.”

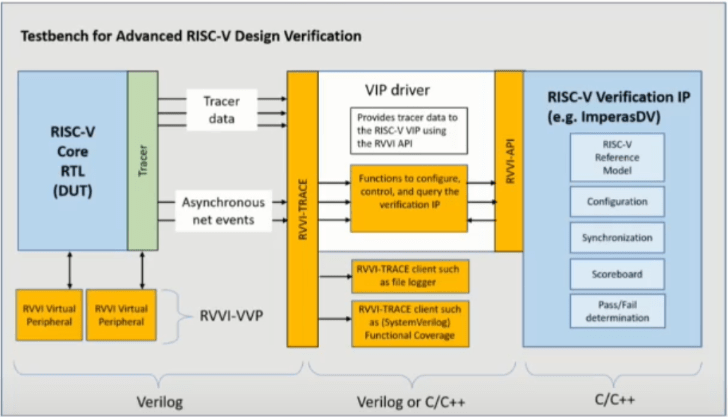

Fig. 1: De architectuur van een RISC-V-verificatieoplossing definiëren. Bron: Imperas

Er is een reeks hulpmiddelen voor nodig. “Naarmate het RISC-V-ecosysteem volwassener wordt, beginnen commerciële implementaties gedefinieerde marktsegmenten te ondersteunen”, zegt Ashish Darbari, oprichter en CEO van Axiomise. “We zien steun voor markten, zoals de automobielsector, die naleving van functionele veiligheid vereisen. We zien steun voor IoT, waarvoor beveiliging nodig is. RISC-V-leveranciers investeren in geavanceerde verificatietechnieken, waaronder virtuele prototyping voor architecturale modellering en prestaties. Er zijn nu tools beschikbaar voor vroege adoptie van formele methoden om bugs vroeg in het ontwerpproces uit te sluiten en het inbrengen van bugs te voorkomen, aangezien ontwerpers moeite hebben om bugs in de hoekjes op te vangen met simulatie op de processor-geheugeninterface.”

Een van de tools die nodig zullen zijn, is de mogelijkheid om testcases te genereren op basis van een featurelijst of een reeks mogelijkheden. “Het geautomatiseerd genereren van testinhoud om prototypes aan te sturen die tijdig rekening houden met verificatiecomplexiteit is van cruciaal belang”, zegt Breker's Kelf. “Deze generatiemechanismen beginnen nu op de markt te verschijnen.”

Conclusie

Een ecosysteem is slechts zo goed als zijn zwakste component, en voor RISC-V is dat de EDA-toolchain. De redenen hiervoor zijn tweeledig. Ten eerste bestond er tot voor kort geen commerciële markt voor processorverificatietools. Hoewel ze in het verleden bestonden, waren ze allemaal verdwenen of opgegaan in de oude verwerkers. Ten tweede creëert de flexibiliteit van de RISC-V ISA een nieuwe optimalisatiebenadering op systeemniveau die een nieuwe set tools vereist. Het kost tijd voordat deze kans wordt begrepen en voordat er commerciële instrumenten verschijnen die deze kans op de juiste manier aanpakken.

Verwant

Een minimale RISC-V

Is er ruimte voor een nog kleinere versie van een RISC-V-processor die 8-bits microcontrollers zou kunnen vervangen?

RISC-V duwt in de mainstream

Open-source processorkernen beginnen op te duiken in heterogene SoC's en pakketten.

Efficiënte tracering in RISC-V

Hoe te werken met de nieuwe RISC-V debug-standaard.

Hoe veilig zijn RISC-V-chips?

Open source op zichzelf garandeert geen veiligheid. Het komt nog steeds neer op de fundamenten van design.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- Platoblockchain. Web3 Metaverse Intelligentie. Kennis versterkt. Toegang hier.

- Bron: https://semiengineering.com/selecting-the-right-risc-v-core/

- 1

- 10

- a

- vermogen

- in staat

- Over

- boven

- versneld

- versnellers

- ACCEPTEREN

- aanvaardbaar

- Account

- nauwkeurigheid

- accuraat

- werkelijk

- adres

- Adoptie

- vergevorderd

- Na

- tegen

- algoritme

- Alles

- al

- bedragen

- analyse

- Analytisch

- en

- en infrastructuur

- beantwoorden

- verschijnen

- Aanvraag

- nadering

- passend

- Boog

- bouwkundig

- architectuur

- GEBIED

- ARM

- verschijning

- geëvalueerd

- geautomatiseerde

- Automatisering

- automotive

- Beschikbaar

- gemiddelde

- terug

- bandbreedte

- gebaseerde

- basis-

- omdat

- wordt

- worden

- vaardigheden

- Begin

- wezen

- voordeel

- BEST

- tussen

- Verder

- Groot

- Beetje

- Blok

- boord

- merk

- brengen

- breed

- Bug

- bugs

- bouw

- Gebouw

- bebouwd

- bedrijfsdeskundigen

- zakelijke ontwikkeling

- CADXPERT / LANDXPERT

- mogelijkheden

- in staat

- het worstelen

- ceo

- zeker

- uitdagen

- uitdagingen

- kansen

- verandering

- chips

- keuze

- keuzes

- Kies

- Beklommen

- CMO

- Collateral

- hoe

- commercieel

- commercieel

- Gemeen

- Bedrijven

- vergelijken

- verenigbaarheid

- concurrerende

- concurrerend

- compleet

- complexiteit

- nakoming

- bestanddeel

- componenten

- computers

- Zorgen

- voorwaarden

- vertrouwen

- Configuratie

- Wij verbinden

- overwegingen

- content

- Kern

- kon

- gepaard

- dekking

- aan het bedekken

- CPU

- aangemaakt

- creëert

- Wij creëren

- het aanmaken

- Kreek

- CTO

- Op dit moment

- gegevens

- Dave

- beslissing

- het definiëren van

- leveren

- eisen

- afdeling

- Afhankelijk

- ingezet

- Design

- ontwerpproces

- ontwerpers

- ontwikkelen

- ontwikkelde

- ontwikkelaars

- het ontwikkelen van

- Ontwikkeling

- systemen

- anders

- moeilijk

- Director

- Nee

- Dont

- beneden

- rit

- gedreven

- aandrijving

- gedurende

- elk

- Vroeg

- gemakkelijkste

- ecosysteem

- ecosystemen

- inspanning

- inspanningen

- beide

- ingebed

- maakt

- Motor

- Engineering

- Motoren

- genoeg

- verzekeren

- zorgen

- Enterprise

- Geheel

- toegang

- Milieu

- omgevingen

- Is gelijk aan

- Evenwicht

- gevestigd

- schattingen

- schatten

- Zelfs

- OOIT

- alles

- uitvoering

- ervaren

- verlenging

- uitbreiding

- extensies

- extern

- uitersten

- Gezicht

- vertrouwd

- Mode

- SNELLE

- sneller

- Kenmerk

- Voordelen

- weinig

- veld-

- Vijg

- VIND DE PLEK DIE PERFECT VOOR JOU IS

- het vinden van

- Voornaam*

- geschikt

- vast

- Flexibiliteit

- flexibel

- formulier

- formeel

- oprichter

- Oprichter en CEO

- FPGA

- Vrijheid

- oppompen van

- vol

- geheel

- functie

- functioneel

- functies

- Fundamentals

- algemeen

- voortbrengen

- het genereren van

- generatie

- krijgen

- het krijgen van

- Geven

- geeft

- Go

- Doelen

- gaan

- goed

- meer

- Groep

- Groeiend

- garantie

- gebeuren

- Hardware

- hulp

- helpt

- hoogwaardige

- homegrown

- Paard

- Hoe

- HTTPS

- reusachtig

- Impact

- uitvoeren

- uitvoering

- in

- omvatten

- omvat

- Inclusief

- meer

- in toenemende mate

- -industrie

- informatie

- Infrastructuur

- instructies

- integreren

- Intel

- geïnteresseerd

- Interface

- Internationale

- investeren

- betrokken zijn

- iot

- IP

- problemen

- IT

- zelf

- Jobomschrijving:

- sleutel

- Soort

- blijven

- bekend

- ladder

- Groot

- Nalatenschap

- Niveau

- niveaus

- leveraging

- Licenties

- Waarschijnlijk

- linux

- Lijst

- lang

- lange tijd

- lang leven

- Kijk

- op zoek

- gemaakt

- Hoofd

- maken

- maker

- MERKEN

- veel

- Mark

- Markt

- Markten

- rijpt

- max-width

- Maak kennis met

- Geheugen

- Methodologie

- methoden

- Metriek

- minimaal

- model

- modellering

- modellen

- wijzigen

- meer

- meest

- beweging

- bewegend

- noodzakelijk

- Noodzaak

- behoeften

- New

- aantal

- vele

- doel van de persoon

- Kansen

- aanbod

- EEN

- open

- open source

- werkzaam

- operatie

- kansen

- optimalisatie

- Keuze

- Opties

- bestellen

- orders

- Overige

- het te bezitten.

- Paketten

- deel

- onderdelen

- verleden

- Hoogtepunt

- Mensen

- prestatie

- Fysiek

- pijpleiding

- Spil

- platform

- platforms

- Plato

- Plato gegevensintelligentie

- PlatoData

- spelers

- spelen

- punt

- Oogpunt

- positie

- mogelijkheden

- mogelijk

- energie

- president

- waarschijnlijk

- probleem

- problemen

- Gegevensverwerker

- processors

- Voortgang

- naar behoren

- prototype

- prototypes

- prototyping

- zorgen voor

- mits

- leverancier

- publiek

- pomp

- pompen

- doel

- doeleinden

- kwaliteit

- vraag

- Contact

- Race

- reeks

- pasklaar

- vast

- echte wereld

- reden

- redelijk

- redenen

- onlangs

- achteloos

- betrouwbaar

- vervangen

- vereisen

- nodig

- vereiste

- Voorwaarden

- vereist

- verantwoordelijkheid

- Kamer

- lopen

- lopend

- Veiligheid

- Veiligheid en beveiliging

- Tweede

- beveiligen

- veiligheid

- segmenten

- gekozen

- selecteren

- selectie

- senior

- sensor

- reeks

- verscheidene

- moet

- tonen

- Shows

- aanzienlijke

- Simon

- Eenvoudig

- simulatie

- single

- Langzaam

- kleinere

- So

- Software

- software development

- oplossing

- Oplossingen

- sommige

- Iemand

- iets

- ergens

- Spoedig

- bron

- snelheid

- besteed

- spinnen

- stabiel

- stadia

- standaard

- Start

- Steve

- Still

- dergelijk

- suite

- ondersteuning

- Oppervlak

- system

- Systems

- Nemen

- neemt

- Talk

- praat

- teams

- Technisch

- technieken

- Technologie

- sjabloon

- proef

- De

- hun

- daarom

- ding

- spullen

- drie

- Door

- doorvoer

- niet de tijd of

- tijdrovend

- keer

- timing

- naar

- vandaag

- samen

- ook

- tools

- top

- Totaal

- opsporen

- traditioneel

- BEURT

- typisch

- typisch

- begrijpelijk

- eenheid

- komende

- .

- Gebruiker

- gebruikers

- gevalideerd

- bevestiging

- waarde

- variëteit

- verkoper

- vendors

- Verificatie

- versie

- rendabel

- Vice President

- Bekijk

- Virtueel

- virtuele platforms

- willen

- manieren

- websites

- Wat

- Wat is

- of

- welke

- en

- wil

- binnen

- Mijn werk

- uitwerken

- wereld

- zou

- Verkeerd

- X

- jaar

- Your

- zephyrnet