Door de jaren heen hebben DRC-tools op bewonderenswaardige wijze gelijke tred gehouden met de enorme groei van de IC-ontwerpomvang. Toch duren de DRC-runs voor het aftekenen van het volledige ontwerp met behulp van gieterijregelkaarten vele uren. Deze lange doorlooptijden zijn acceptabel voor de definitieve aftekening, maar er zijn veel situaties waarin DRC-resultaten snel nodig zijn wanneer kleine wijzigingen in het ontwerp worden aangebracht om problemen in een laat stadium op te lossen. Siemens EDA heeft in samenwerking met MaxLinear een witboek geschreven dat laat zien hoe Caliber RealTime Digital in-design DRC snel DRC-resultaten kan opleveren als er kleine wijzigingen in het ontwerp zijn aangebracht. Een snellere DRC-doorlooptijd voor gelokaliseerde wijzigingen kan de iteratieve foutoplossing versnellen die vaak nodig is om tapeout te bereiken.

In het witboek met de titel “MaxLinear en Calibre RealTime Digital: Faster signoff DRC convergentie plus ontwerpoptimalisatie voor maakbaarheid” praten MaxLinear en Siemens over de omstandigheden waarin de mogelijkheid om DRC uit te voeren op een klein deel van een ontwerp met het volledige gieterijregeldek kan bespaar vele uren en pijnlijke langzame iteraties.

Moderne P&R-tools leveren uitstekend werk bij het produceren van een DRC-correcte lay-out. Er zijn echter altijd gevallen waarin de bronnen van overtredingen complexer zijn en tijdens P&R over het hoofd worden gezien. Deze vereisen meestal een handmatige oplossing, waarbij rekening wordt gehouden met complexe ontwerpregels. Tijdens deze handmatige reparaties bestaat ook de kans dat er nieuwe fouten worden geïntroduceerd. Siemens presenteert informatie van MaxLinear in het witboek waarin wordt benadrukt hoe Calibre RealTime Digital, gekoppeld aan hun P&R-tool, hen in staat stelt om snel handmatige oplossingen te implementeren en te valideren. Het alternatief is om een volledige DRC-run uit te voeren, alleen maar om te zien of de veranderingen in een klein gebied correct zijn.

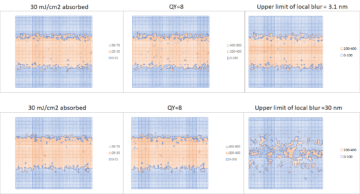

MaxLinear maakt chips met analoge en digitale blokken. De analoge blokken hebben minder metaallagen nodig, dus om de productiekosten te verlagen, proberen ze de routeringslagen in het volledige ontwerp te verminderen. Dit zorgt voor problemen met de routeringsdichtheid, die vaak in strijd zijn met het handhaven van een hoge DFM-ranglijst. Single-cut via's gebruiken de minste ruimte, maar dragen bij aan een lage DFM-ranglijst. Als het erop aan komt, kunnen MaxLinear-ontwerpers handmatig tussen typen schakelen om om te gaan met de afwegingen tussen routeerbaarheid en DFM. Maar deze moeten worden gevolgd door een alomvattende DRC om te controleren op zaken als schendingen van multi-patterning. Met Caliber RealTime Digital kunnen ontwerpers via typen wisselen en vervolgens snel zien of er DRC-fouten zijn.

Via's zijn niet het enige probleem dat kan leiden tot DRC-problemen die tijd en moeite vergen om op te lossen. Het witboek beschrijft verschillende situaties waarin handmatig werk vereist is en de enige manier om deze problemen uiteindelijk op te lossen is door een schone DRC-run te krijgen. Een van deze situaties die zich laat in het proces voordoen, is wanneer re-tapeout-controles (RTO) nodig zijn om ervoor te zorgen dat ECO’s compatibel zijn met bestaande maskers. De RTO-regels zijn van nature restrictiever dan de oorspronkelijke DRC-regels.

Het witboek gaat ook in op elektromigratieproblemen die kunnen worden veroorzaakt door het gebruik van oneigenlijke via's. Ook hier speelde Caliber ReatTime Digital een belangrijke rol voor MaxLinear bij het correct implementeren van DRC via vervanging. Alles bij elkaar genomen zijn er veel omstandigheden die DRC-controles vereisen nadat kleine wijzigingen zijn aangebracht om functionele of maakbaarheidsproblemen in een ontwerp te corrigeren. Als u de mogelijkheid heeft om onmiddellijk resultaat te boeken, in plaats van te wachten op een dag of langer bij een volledige DRC-run, kunt u dagen of weken van een project besparen. Het is niet goed om voor verrassingen te komen na een grote run in de DRC. Siemens Caliber RealTime Digitale interface naar P&R-tools lijkt hiervoor ideaal te passen. Deze whitepaper van Siemens is te vinden op de Siemens EDA-website.

Deel dit bericht via:

Bron: https://semiwiki.com/eda/299770-realtime-digital-drc-can-save-time-close-to-tapeout/

- Alles

- GEBIED

- artikelen

- veroorzaakt

- Controles

- chips

- conflict

- content

- dag

- transactie

- Design

- digitaal

- Tot slot

- geschikt

- Bepalen

- Gieterij

- vol

- goed

- hier

- Hoge

- Hoe

- HTTPS

- reusachtig

- informatie

- problemen

- Jobomschrijving:

- houden

- leiden

- lang

- productie

- Maskers

- metaal

- Papier

- project

- verminderen

- Resultaten

- reglement

- lopen

- Siemens

- Maat

- Klein

- So

- Tussenruimte

- snelheid

- Stadium

- Stap over voor slechts

- thumbnail

- niet de tijd of

- Tegen

- Website

- wit papier

- Mijn werk

- jaar