Sinds het debuut in de jaren tachtig met gedeelde LAN's van 1980 Mbps via coaxkabels heeft Ethernet consistente vooruitgang geboekt, nu met het potentieel om snelheden tot 10 Tbps te ondersteunen. Deze vooruitgang heeft het mogelijk gemaakt dat Ethernet een breder scala aan toepassingen kan bedienen, zoals livestreaming, radiotoegangsnetwerken en industriële controle, waarbij het belang van betrouwbare pakketoverdracht en servicekwaliteit wordt benadrukt. Nu de huidige internetbandbreedte zo'n 1.6 Tbps bedraagt, is er een groeiende vraag naar verbeterde back-end intra-datacenterverkeersafhandeling. Hoewel individuele servers nog niet op Terabit-per-seconde-niveaus werken, nadert het totale datacenterverkeer deze schaal, wat de IEEE's 500dj-groep ertoe aanzet om standaardisatie-inspanningen te ondernemen en robuuste Ethernet-controllers en SerDes nodig heeft om de groeiende gegevensstroom te beheren. Tegen deze achtergrond van escalerende eisen bereikt de communicatie tussen processors al deze snelheden.

Communicatie tussen processors loopt voorop in de behoefte aan 1.6T-snelheden met minimale latentie. Hoewel individuele apparaten worden beperkt door hun inherente verwerkingscapaciteiten en chipgrootte, kan het combineren van chips deze capaciteiten aanzienlijk vergroten. De eerste generatie applicaties zal naar verwachting worden gevolgd door intra-datacenter switch-to-switch-verbindingen, waardoor het bundelen van krachtige processors en geheugen mogelijk wordt, waardoor de schaalbaarheid en efficiëntie binnen cloud computing worden vergroot.

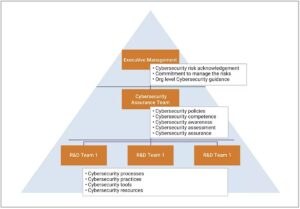

IEEE's 802.3dj-initiatief: Verbetering van Ethernet-standaarden voor 1.6 Tbps-interoperabiliteit

Naleving van de evoluerende standaardisatie-inspanningen is van cruciaal belang voor een naadloze interoperabiliteit van ecosystemen. De 802.3dj-groep van IEEE is bezig met het formuleren van de komende Ethernet-standaard, die fysieke lagen en beheerparameters omvat voor snelheden van 200G tot 1.6 terabit per seconde. Het doel van de groep is een Ethernet MAC-datasnelheid van 1.6 Tbps, waarbij wordt gestreefd naar een maximale bitfoutenkans van niet meer dan 10-13 op de MAC-laag. Verdere voorzieningen zijn onder meer optionele 16- en 8-baans Attachment Unit Interfaces (AUI) die geschikt zijn voor verschillende chiptoepassingen, waarbij gebruik wordt gemaakt van 112G- en 224G-SerDes. Fysiek omvat de specificatie van 1.6 Tbps transmissie via 8 paar koperen Twinax-kabels voor maximaal één meter en 8 paar glasvezel voor afstanden tussen 500 meter en 2 km. Hoewel de volledige ratificatie van de standaard in het voorjaar van 2026 wordt verwacht, wordt verwacht dat de kernfuncties in 2024 voltooid zullen zijn.

Bandbreedte-overhead en foutcorrectie in een 1.6T Ethernet-subsysteem

Fig. 1: Diagram dat de componenten van een 1.6T Ethernet-subsysteem weergeeft.

In eerdere Ethernet-iteraties richtte het PCS zich vooral op gegevenscodering voor betrouwbare pakketdetectie. Met de escalatie naar 1.6T Ethernet-snelheden wordt echter de behoefte aan Forward Error Correction (FEC) duidelijk, vooral om signaalverslechtering over zelfs korte verbindingen tegen te gaan. Voor dit doel blijft 1.6T Ethernet gebruik maken van Reed-Solomon FEC. Deze aanpak bouwt een codewoord op dat bestaat uit 514 symbolen van 10 bits, gecodeerd in een blok van 544 symbolen, wat resulteert in een bandbreedteoverhead van 6%. Deze FEC-codewoorden worden verdeeld over de fysieke AUI-verbindingen, zodat elke fysieke verbinding (8 voor 1.6T Ethernet) niet een volledig codewoord bevat. Deze methode biedt niet alleen extra bescherming tegen foutuitbarstingen, maar maakt ook parallellisatie aan de andere kant van de decoder mogelijk, waardoor de latentie wordt verminderd.

De Physical Medium Attachment (PMA), voorzien van een versnellingsbak en SerDes, brengt het Ethernet-signaal naar de verzonden kanalen. Voor 1.6T Ethernet gaat het om 8 kanalen die elk draaien op 212 Gbps, goed voor een FEC-overhead van 6%. De gebruikte modulatietechniek is 4-Level Pulse Amplitude Modulation (PAM-4), die twee databits codeert voor elk transmissiesymbool, waardoor de bandbreedte effectief wordt verdubbeld wanneer deze wordt gecombineerd met de traditionele Non-Return Zero (NRZ)-benadering. Het transmissiemechanisme is gebaseerd op digitaal-naar-analoog-conversie, terwijl aan de ontvangende kant een analoog-naar-digitaal-conversie in combinatie met DSP's zorgt voor nauwkeurige signaalextractie.

Bovendien is het belangrijk op te merken dat het Ethernet-PCS een “buitenste FEC” introduceert die zich van begin tot eind uitstrekt over een Ethernet-verbinding. Om kanalen met een groter bereik te versterken, zit er een extra foutcorrectielaag voor individuele fysieke lijnen in de pijplijn, waarschijnlijk met behulp van een hamming-code FEC. Verwacht wordt dat deze correctie zijn primaire toepassing zal vinden in optische zendontvangermodules waar een dergelijke correctie absoluut noodzakelijk is.

Fig. 2: Diagram met extra overhead die wordt toegevoegd bij gebruik van een aaneengeschakelde FEC voor groter bereik.

In het voorbeeldsysteem afgebeeld in figuur 2 zijn de MAC en PCS verbonden via een optische module en een vezelrek. Het PCS heeft een bitfoutpercentage van 10-5 bij de optische moduleverbinding, plus fouten van de optische verbinding zelf. Het gebruik van een enkele RS-FEC end-to-end zou niet voldoende zijn om de 10 te behalen-13 Ethernet-standaard, waardoor de verbinding onbetrouwbaar wordt. Een optie zou een drievoudige implementatie van afzonderlijke RS FEC bij elke hop zijn, waardoor de kosten en de latentie aanzienlijk toenemen. Een effectievere oplossing is de integratie van een aaneengeschakelde Hamming Code FEC specifiek voor de optische link, die tegemoetkomt aan de typische willekeurige fouten van optische verbindingen. Deze binnenste FEC-laag zorgt voor een extra uitbreiding van de lijnsnelheid van 212 Gbps naar 226 Gbps, dus het is essentieel dat de SerDes deze lijnsnelheid kan ondersteunen.

Latency-uitdagingen in 1.6T Ethernet-systemen

Fig. 3: Latentiepad voor 1.6T Ethernet-subsysteem.

Verschillende componenten dragen bij aan de Ethernet-latentie: de verzendwachtrij, de transmissieduur, de gemiddelde doorlooptijd en verschillende verwerkings- en ontvangsttijden. Om dit te visualiseren, kunt u figuur 3 bekijken, waarin een uitgebreid 1.6T Ethernet-subsysteem wordt weergegeven. Hoewel latentie kan worden beïnvloed door de reactietijd van de far-end-toepassing, is deze factor extern aan Ethernet en daarom vaak uitgesloten tijdens latentieanalyse. Het minimaliseren van de latentie bij de Ethernet-interface vereist inzicht in de specifieke omstandigheden. Latentie is bijvoorbeeld misschien niet het voornaamste probleem voor trunkverbindingen tussen switches vanwege inherente vertragingen bij langzamere clientverbindingen. Afstand speelt ook een rol; grotere lengtes introduceren meer latentie. Dit betekent uiteraard niet dat we de latentie in andere scenario's over het hoofd moeten zien; het verminderen van de latentie is altijd een doel.

De transmissielatentie is inherent gebonden aan de Ethernet-snelheid en de framegrootte. Concreet vereist het verzenden van een pakket van minimale grootte voor een 1.6T Ethernet-systeem 0.4 ns – in wezen één Ethernet-frame per tick van een 2.5 GHz-klok. Aan de andere kant duurt het verzenden van een standaard frame met maximale grootte 8 ns, wat zich uitbreidt tot 48 ns voor Jumbo Frames. Het gekozen medium dicteert verder de latentie. Optische vezels hebben bijvoorbeeld doorgaans een latentie van 5 ns per meter, terwijl koperen kabels met 4 ns per meter iets sneller zijn.

Een substantieel deel van de totale latentie is geworteld in de ontvangercontroller. De RS FEC-decoder introduceert inherent latentie. Om de foutcorrectie te initiëren moet het systeem 4 codewoorden ontvangen, wat bij 1.6 Tbps neerkomt op 12.8 ns. Daaropvolgende activiteiten, waaronder foutcorrectie en buffering, versterken deze latentie. Hoewel de opslagduur van het FEC-codewoord consistent blijft, is de latentie tijdens berichtontvangst afhankelijk van de specifieke implementatie. Niettemin kan de latentie worden geoptimaliseerd door zorgvuldige digitale ontwerpstrategieën toe te passen.

In wezen is er een inherente, onvermijdelijke latentie als gevolg van het FEC-mechanisme en de fysieke afstand of kabellengte. Naast deze factoren speelt ontwerpexpertise een cruciale rol bij het minimaliseren van de latentie van Ethernet-controllers. Door gebruik te maken van een complete oplossing die de MAC, PCS en PHY integreert en optimaliseert, wordt de weg vrijgemaakt voor de meest efficiënte implementatie met lage latentie.

Samengevat

Fig. 4: First-pass siliciumsucces voor Synopsys 224G Ethernet PHY IP in 3nm-proces met zeer lineaire PAM-4-ogen.

1.6 Tbps Ethernet is op maat gemaakt voor de meest bandbreedte-eisende en latentiegevoelige toepassingen. Met de opkomst van de 224G SerDes-technologie, in combinatie met de vooruitgang op het gebied van MAC en PCS IP, zijn nu uitgebreide oplossingen beschikbaar die voortdurend voldoen aan de evoluerende 1.6T Ethernet-standaarden. Bovendien moet het digitale en analoge IP-ontwerp, vanwege de latentie die inherent is aan het protocol en de foutcorrectiemethoden, zorgvuldig worden vervaardigd door deskundige ontwerpers om te voorkomen dat er onnodige latentie in het datapad wordt geïntroduceerd.

Het bereiken van topprestaties voor 1.6T SoC-ontwerpen vereist een efficiënt geoptimaliseerde architectuur en nauwgezette ontwerppraktijken voor elk chiponderdeel. Dit legt de nadruk op energiebesparing en minimaliseert de siliciumvoetafdruk, waardoor datasnelheden van 1.6T werkelijkheid worden. Op silicium bewezen Synopsys 224G Ethernet PHY IP heeft de weg geëffend voor de 1.6T MAC- en PCS-controller. Met behulp van geavanceerde ontwerp-, analyse-, simulatie- en meettechnieken blijft Synopsys uitzonderlijke signaalintegriteit en jitterprestaties leveren, met een complete Ethernet-oplossing inclusief MAC+PCS+PHY.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- : heeft

- :is

- :niet

- :waar

- $UP

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- toegang

- beschikbaar

- Accounting

- accuraat

- Bereiken

- over

- activiteiten

- toegevoegd

- Extra

- Daarnaast

- De goedkeuring van

- vooruitgang

- oprukkende

- tegen

- het richten

- toegestaan

- al

- ook

- Hoewel

- altijd

- midden

- hoeveelheden

- versterken

- an

- analyse

- en

- verwachte

- Aanvraag

- toepassingen

- nadering

- architectuur

- ZIJN

- AS

- At

- vermijd

- Back-end

- achtergrond

- bandbreedte

- BE

- wordt

- tussen

- Verder

- Beetje

- Blok

- ondersteunen

- het stimuleren

- Brengt

- bouwt

- maar

- by

- kabel

- kabels

- CAN

- capaciteiten

- dragen

- uitdagingen

- kanalen

- spaander

- chips

- uitgekozen

- situatie

- klant

- Klok

- Cloud

- cloud computing

- code

- gecombineerde

- combineren

- Communicatie

- compleet

- voltooiing

- bestanddeel

- componenten

- uitgebreid

- omvattende

- computergebruik

- Bezorgdheid

- samenwerking

- gekoppeld blijven

- aansluitingen

- GESPREK

- Overwegen

- overwegingen

- consequent

- blijft

- doorlopend

- bijdragen

- onder controle te houden

- controleur

- Camper ombouw

- Koper

- Kern

- Kosten

- tegenwerken

- cursus

- bewerkte

- creëert

- Actueel

- gegevens

- Datacenter

- debuut

- vertragingen

- leveren

- Vraag

- veeleisende

- eisen

- beeltenis

- Design

- ontwerpers

- ontwerpen

- Opsporing

- systemen

- dicteert

- anders

- digitaal

- ijverig

- displays

- afstand

- verdeeld

- Nee

- verdubbeling

- twee

- duur

- gedurende

- elk

- Vroeger

- ecosysteem

- effectief

- effectief

- doeltreffendheid

- doeltreffend

- efficiënt

- inspanningen

- opkomst

- benadrukt

- nadruk te leggen op

- loondienst

- gebruik

- maakt

- waardoor

- omvat

- einde

- eind tot eind

- waarborgt

- Geheel

- fout

- fouten

- escalatie

- essentie

- essentieel

- in wezen

- Ether (ETH)

- Zelfs

- Alle

- duidelijk

- evoluerende

- voorbeeld

- uitzonderlijk

- uitgesloten

- uit te breiden

- uitbreiding

- verwacht

- expert

- expertise

- verlengen

- verlenging

- extern

- extractie

- Ogen

- factor

- factoren

- ver

- sneller

- Voordelen

- Met

- Figuur

- VIND DE PLEK DIE PERFECT VOOR JOU IS

- Voornaam*

- Eerste generatie

- stroom

- gericht

- gevolgd

- Footprint

- Voor

- formuleren

- Naar voren

- FRAME

- oppompen van

- verder

- generatie

- geeft

- meer

- Groep

- Groep

- Groeiend

- hand

- Behandeling

- Hoge

- hoge performantie

- zeer

- Echter

- HTML

- HTTPS

- gebiedende wijs

- uitvoering

- belang

- belangrijk

- verbeterd

- in

- Anders

- omvatten

- Inclusief

- meer

- individueel

- industrieel

- beïnvloed

- inherent

- inherent

- beginnen

- initiatief

- instantie

- integreert

- integratie

- integriteit

- Interface

- interfaces

- Internet

- Interoperabiliteit

- in

- intrinsiek

- voorstellen

- Introduceert

- de invoering

- gaat

- IP

- IT

- iteraties

- HAAR

- zelf

- jpg

- Rijstrook

- Wachttijd

- lagen

- Legkippen

- Lengte

- niveaus

- leveraging

- Waarschijnlijk

- Lijn

- lijnen

- LINK

- links

- leven

- langer

- Laag

- Mac

- maken

- beheer

- management

- max-width

- maximaal

- Mei..

- gemiddelde

- maat

- mechanisme

- Medium

- Geheugen

- Bericht

- methode

- methoden

- nauwkeurig

- minimaal

- verkleinen

- minimaliseert

- minimaliseren

- module

- Modules

- meer

- meest

- Dan moet je

- naderen

- Noodzaak

- netwerken

- niettemin

- geen

- nota

- nu

- doel van de persoon

- of

- vaak

- on

- EEN

- Slechts

- werkzaam

- geoptimaliseerde

- Optimaliseert

- Keuze

- or

- Overige

- over

- totaal

- paren

- parameters

- vooral

- pad

- PCs

- voor

- prestatie

- optredens

- Fysiek

- fysiek

- pijpleiding

- centraal

- Plato

- Plato gegevensintelligentie

- PlatoData

- speelt

- plus

- potentieel

- energie

- praktijken

- in de eerste plaats

- primair

- verwerking

- processors

- progressie

- geprojecteerde

- bescherming

- protocol

- pols

- doel

- voortvarend

- kwaliteit

- Radio

- willekeurige

- reeks

- tarief

- Tarieven

- bereiken

- het bereiken van

- reactie

- Realiteit

- ontvangen

- ontvangende

- receptie

- vermindering

- betrouwbaar

- stoffelijk overschot

- weergave

- vereist

- begrensd

- verkregen

- robuust

- Rol

- ingeworteld

- lopend

- Schaalbaarheid

- Scale

- scenario's

- naadloos

- Tweede

- gezien

- segment

- gevoelig

- apart

- dienen

- service

- reeks

- verscheidene

- gedeeld

- Bermuda's

- moet

- presentatie

- Signaal

- aanzienlijk

- Silicium

- simulatie

- Maat

- So

- oplossing

- Oplossingen

- overspanningen

- een toonaangevende rol

- specifiek

- specifiek

- specificatie

- snelheden

- voorjaar

- Stadium

- standaard

- normalisering

- normen

- mediaopslag

- strategieën

- streaming

- volgend

- wezenlijk

- succes

- dergelijk

- geschikt

- ondersteuning

- symbool

- system

- op maat gemaakt

- neemt

- techniek

- technieken

- Technologie

- neem contact

- dat

- De

- hun

- Er.

- daarbij

- daarom

- Deze

- dit

- Door

- Dus

- teek

- Gebonden

- niet de tijd of

- keer

- naar

- top

- traditioneel

- verkeer

- overdracht

- overdragen

- Triple

- twee

- typisch

- typisch

- onvermijdelijk

- begrip

- ondernemen

- eenheid

- komende

- op

- gebruik

- gebruik maken van

- via

- visualiseren

- Manier..

- we

- wanneer

- welke

- en

- bredere

- Met

- binnen

- zou

- nog

- zephyrnet

- nul