Een technisch artikel met de titel “WWW: What, When, Where to Compute-in-Memory” werd gepubliceerd door onderzoekers van Purdue University.

Abstract:

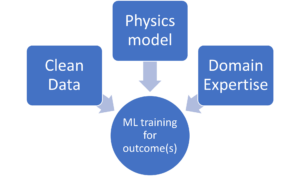

“Compute-in-memory (CiM) is een overtuigende oplossing gebleken om de hoge kosten voor gegevensverplaatsing in von Neumann-machines te verminderen. CiM kan massaal parallelle GEMM-bewerkingen (General Matrix Multiplication) in het geheugen uitvoeren, de dominante berekening in Machine Learning (ML)-gevolgtrekking. Het herbestemmen van geheugen voor computers roept echter belangrijke vragen op over 1) Welk type CiM te gebruiken: Gegeven een veelheid aan analoge en digitale CiM's, is het nodig om hun geschiktheid vanuit systeemperspectief te bepalen. 2) Wanneer moet u CiM gebruiken: ML-inferentie omvat workloads met een verscheidenheid aan geheugen- en computervereisten, waardoor het moeilijk is om te identificeren wanneer CiM voordeliger is dan standaard verwerkingskernen. 3) Waar CiM te integreren: Elk geheugenniveau heeft een andere bandbreedte en capaciteit, wat van invloed is op de gegevensverplaatsing en de locatievoordelen van CiM-integratie.

In dit artikel onderzoeken we antwoorden op deze vragen met betrekking tot CiM-integratie voor versnelling van ML-inferentie. We gebruiken Timeloop-Accelergy voor vroege evaluatie op systeemniveau van CiM-prototypes, inclusief zowel analoge als digitale primitieven. We integreren CiM in verschillende cachegeheugenniveaus in een Nvidia A100-achtige basisarchitectuur en stemmen de datastroom af op verschillende ML-workloads. Onze experimenten laten zien dat CiM-architecturen de energie-efficiëntie verbeteren, tot 0.12x lagere energie bereiken dan de vastgestelde basislijn met INT-8-precisie, en tot 4x prestatieverbeteringen met gewichtsinterleaving en duplicatie. Het voorgestelde werk biedt inzicht in welk type CiM moet worden gebruikt, en wanneer en waar dit optimaal kan worden geïntegreerd in de cachehiërarchie voor GEMM-versnelling.”

Vind de technisch document hier. Gepubliceerd december 2023 (voordruk).

Sharma, Tanvi, Mustafa Ali, Indranil Chakraborty en Kaushik Roy. "WWW: wat, wanneer, waar in het geheugen berekenen." arXiv voordruk arXiv:2312.15896 (2023).

Gerelateerd lezen

Het verhogen van de AI-energie-efficiëntie met rekenkracht in het geheugen

Hoe u zettascale-workloads kunt verwerken en binnen een vast energiebudget kunt blijven.

Modellering van rekenkracht in het geheugen met biologische efficiëntie

Generatieve AI dwingt chipmakers om computerbronnen intelligenter te gebruiken.

SRAM in AI: de toekomst van het geheugen

Waarom SRAM wordt gezien als een cruciaal element in nieuwe en traditionele computerarchitecturen.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- PlatoData.Network Verticale generatieve AI. Versterk jezelf. Toegang hier.

- PlatoAiStream. Web3-intelligentie. Kennis versterkt. Toegang hier.

- PlatoESG. carbon, CleanTech, Energie, Milieu, Zonne, Afvalbeheer. Toegang hier.

- Plato Gezondheid. Intelligentie op het gebied van biotech en klinische proeven. Toegang hier.

- Bron: https://semiengineering.com/cim-integration-for-ml-inference-acceleration/

- : heeft

- :is

- :waar

- $UP

- 1

- 2023

- a

- versnelling

- het bereiken van

- AI

- verlichten

- an

- en

- antwoorden

- architectuur

- AS

- At

- bandbreedte

- Baseline

- heilzaam

- betekent

- zowel

- begroting

- by

- cache

- CAN

- Inhoud

- dwingende

- berekening

- Berekenen

- Kosten

- kritisch

- gegevens

- December

- bepalen

- anders

- moeilijk

- digitaal

- dominant

- elk

- Vroeg

- doeltreffendheid

- element

- voortgekomen

- energie-niveau

- energie-efficiëntie

- gevestigd

- evaluatie

- experimenten

- Verken

- vast

- Voor

- Krachten

- oppompen van

- toekomst

- verdiensten

- Algemeen

- gegeven

- hier

- hiërarchie

- Hoge

- Echter

- HTTPS

- identificeren

- verbeteren

- in

- omvat

- Inclusief

- inzichten

- integreren

- integratie

- in

- IT

- jpg

- sleutel

- leren

- Niveau

- niveaus

- te verlagen

- machine

- machine learning

- Machines

- maken

- massief

- Matrix

- Geheugen

- ML

- meer

- beweging

- menigte

- nodig

- New

- Nvidia

- of

- on

- open

- Operations

- onze

- Papier

- Parallel

- uitvoeren

- prestatie

- perspectief

- Plato

- Plato gegevensintelligentie

- PlatoData

- vormt

- energie

- precisie

- verwerking

- voorgestelde

- prototypes

- biedt

- gepubliceerde

- Contact

- met betrekking tot

- Voorwaarden

- onderzoekers

- Resources

- roy

- tonen

- oplossing

- standaard

- blijven

- geschiktheid

- Systems

- Technisch

- neem contact

- dat

- De

- De toekomst

- hun

- Deze

- dit

- getiteld

- naar

- traditioneel

- type dan:

- universiteit-

- .

- variëteit

- divers

- bekeken

- van

- was

- we

- gewicht

- Wat

- wanneer

- Met

- binnen

- Mijn werk

- zephyrnet