Thermische stress is een bekend probleem bij geavanceerde verpakkingen, samen met de uitdagingen van mechanische stress. Beide worden verergerd door heterogene integratie, waarvoor vaak materialen moeten worden gemengd met incompatibele thermische uitzettingscoëfficiënten (CTE).

De effecten zijn al zichtbaar en zullen waarschijnlijk alleen maar erger worden naarmate de dichtheid van pakketten groter wordt dan 1,000 hobbels per chip.

“Je combineert metalen met een relatief hoge CTE, dan heb je polymeren met een nog grotere CTE-stijfheid en dan heb je diëlektrica met een extreem lage CTE. Als je alles eenmaal in elkaar hebt gezet, is stress onvermijdelijk”, zegt Mario Gonzalez, wetenschappelijk directeur en R&D-manager voor mechanische en thermische modellering en karakterisering bij imec.

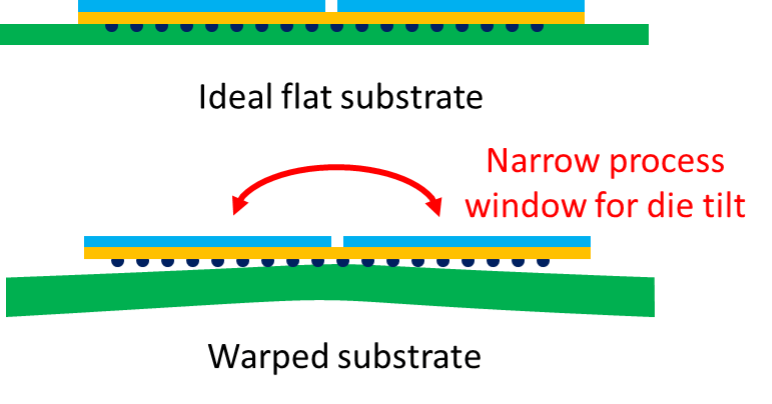

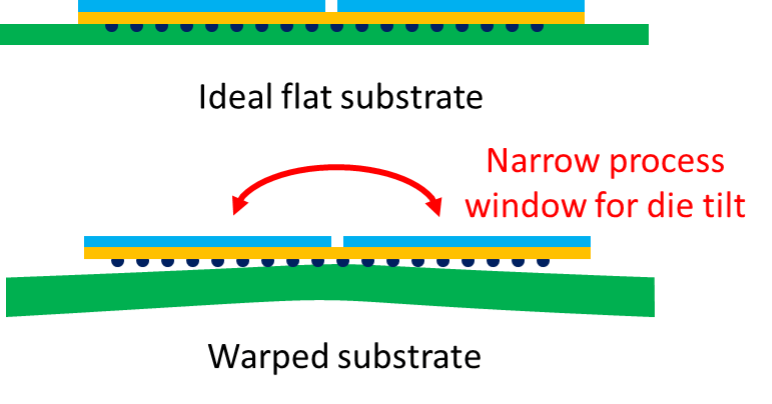

Dergelijke stress resulteert vaak in aanzienlijke kromtrekken of kantelen van de matrijs, wat op zijn beurt leidt tot omstandigheden die de betrouwbaarheid verminderen. "Je hebt te maken met verschillende substraattechnologieën met meerdere lagen", zegt Chip Greely, vice-president engineering bij Promex Industries. “Vooral verschillende kerndiktes in substraten beginnen veel klassieke mechanische problemen te veroorzaken, waaronder kromtrekken, wat een pijnpunt is geworden voor sommige van de grotere spelers. We vragen veel van onze klanten die een system-in-package, heterogene integratie multi-chipmodule hebben, om de schaduwmoiré-gegevens van hun substraten te verstrekken, zodat we kunnen zien hoe de vervorming ervan verandert door de reflow-temperatuur en idealiter de reflectiepunt.”

Deze soort heeft verschillende negatieve effecten, ervaren op vele dimensionale schalen, volgens Gilad Barak, vice-president van geavanceerde nieuwe technologieën bij Nova. "Vaak is het buigen en draaien van kenmerken op nanostructuurniveau het gevolg van de ingebouwde spanning die is gecreëerd, zoals gevonden in sommige DRAM en front-end logische nanosheets," zei hij. “Een ander voorbeeld heeft betrekking op gebieden op micronschaal waar geïnduceerde spanning de fabricage van hoogwaardige halfgeleiderstructuren verhindert, zoals typisch is in 'keep-out zones' rond through-silicium vias (TSV's). Ten slotte kunnen de grootschalige effecten van geïnduceerde spanning leiden tot het buigen van de wafel, wat de hantering en fabricage van de wafel aanzienlijk bemoeilijkt, wat het risico inhoudt dat de wafel zelf breekt. Buigen van wafers wordt met name gezien tijdens het afzetten van dikke diëlektrische lagen, zoals gebruikelijk is tijdens de fabricage van 3D NAND-apparaten.”

Het goede nieuws is dat de industrie zich terdege bewust is van deze en aanverwante problemen. Het slechte nieuws is dat er nog steeds een tekort aan oplossingen is, hoewel er momenteel veel benaderingen worden onderzocht.

"Er zijn verschillende methodologieën om kromtrekken te verminderen, maar geen van hen is volledig succesvol, en ze komen altijd met compromissen", zegt Frank Chen, directeur toepassingen en productbeheer bij Bruker Nano Oppervlakken & Metrologie. “De problemen staan niet op zichzelf bij een beperkte selectie van toepassingen. Elke keer dat je een matrijs op een ander substraat bevestigt, krijg je deze problemen.

Dit alles betekent dat inspectie en metrologie een cruciale rol moeten blijven spelen. Andere problemen, zoals hotspots, kunnen ook verergeren wanneer meerdere chips in heterogene pakketten worden gecombineerd.

"Tijdens de test zullen verschillende chips op verschillende tijdstippen en verschillende temperaturen opwarmen, waardoor mogelijke hotspots ontstaan die goed moeten worden gekoeld", zegt Andrei Berar, senior director voor Test Business Development bij Amkor. "Naast het creëren van specifieke thermische actieve controllers - passend bij het gebied van verschillende chips - zijn er aanzienlijke inspanningen om adaptieve thermische controllers te ontwikkelen die kunnen 'anticiperen' op de hotspots op basis van de vectoren die door het testprogramma worden geleverd."

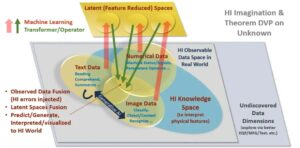

Dergelijke combinaties leiden ook tot een toenemend gebruik van hybride metrologie – het combineren van verschillende technieken om zo snel mogelijk tot de kern van problemen te komen.

Ontwerp, inspectie, testoplossingen

Inderdaad, het klassieke samenspel tussen ontwerp, inspectie en thermomechanische belasting is alleen maar ingewikkelder geworden met duizenden steeds kleinere en fragielere verbindingen.

Een resultaat is een hernieuwde nadruk op het verschuiven naar links, om hopelijk de CTE-problemen en de daaruit voortvloeiende trapsgewijze effecten die kunnen leiden tot oververhitting en mechanische stress te "ontwerpen". En om de kans op het voorkomen en vinden van kritieke defecten te vergroten, zijn zowel simulatie als inspectie nodig, aldus Andras Vass-Varnai, portfolio development executive bij het Electronics and Semiconductor Industry-segment van Siemens Digital Industries-software.

"Thermische en structurele co-simulatie met behulp van computationele stromingsdynamiek (CFD), eindige-elementenmodellering (FEA), enz., in de vroege ontwerpfase van het pakket, helpt zowel de verwachte prestaties van de assemblage te begrijpen als een goede basis voor ' AI-gestuurde optimalisatie omdat veel van de ontwerpkeuzes kunnen worden geparametriseerd', legt Vass-Varnai uit. “Zodra het eerste prototype is gebouwd, kunnen thermische transiënte testen helpen om de thermische prestaties van het onderdeel in kaart te brengen. Als er een discrepantie is tussen het verwachte en het werkelijke thermische gedrag, kunnen de testgegevens worden gebruikt om de materiaaleigenschappen van de digitale tweeling van het pakket te 'kalibreren' en de materiaalbibliotheken bij te werken voor een hogere initiële nauwkeurigheid van toekomstige ontwerpen.”

Het is een groeiende uitdaging om de beste manier te vinden om bump-arrays te testen en te ontwerpen voor testen. "Wat als er een signaal is dat op en neer gaat?" vroeg Rob Aitken, een Synopsys vakgenoot. “Dat zorgt voor een testprobleem, want nu heb je een signaal dat nergens heen gaat en een ander signaal dat nergens vandaan komt, en je moet uitzoeken hoe je die dingen gaat testen. Test je ze? Maar dan zijn er fysieke afmetingen die je moet behouden, en dan loop je het risico op mechanische schade. Of vind je een soort JTAG-achtige structuur? Maar dat vermindert dan de efficiëntie van deze verbindingspunten. We bevinden ons in de enorme experimenteerfase waarin iedereen zegt: 'Misschien werkt dit, misschien werkt dat.' Op dit moment zou ik niet noodzakelijkerwijs willen wedden op wat 'dat' is.

Volgens JCET zijn er zowel indirecte als directe testmogelijkheden voor defectonderzoek. CSAM (Computed Scanning Acoustic Tomography) en 3D X-ray zijn bijvoorbeeld indirect, terwijl mechanische dwarsdoorsnede-analyse een hulpmiddel is voor direct bewijs. JCET beschikt over geavanceerde thermische karakteriseringsapparatuur om ook de materiaal-/structuurproblemen als gevolg van mechanische defecten te karakteriseren.

Optische inspectie is, zoals altijd, de snelste aanpak voor inline inspectie, maar best practice is een hybride aanpak. "De beste methode voor het detecteren van kortsluitingen/openingen en marginale defecten is SPI (soldeerpasta-inspectie) naar pre-reflow AOI (geautomatiseerde optische inspectie) naar post-reflow AOI naar inline X-ray," adviseerde Timothy Skunes, vice-president onderzoek en ontwikkeling in Nordson Test & Inspection's CyberOptica portefeuille.

Daarnaast kunnen andere modaliteiten nuttig zijn, vooral bij geavanceerde knooppunten. Een recente benadering om spanning in halfgeleiderapparaten te karakteriseren, is bijvoorbeeld Raman Spectroscopie (RS). "RS is zeer geschikt voor on-structure metingen, biedt snelle metingen in de orde van seconden en kleine spotgroottes van enkele microns om gedetailleerde metingen mogelijk te maken", aldus Nova's Barak. "De moeilijkheid om spanning op structuren direct te meten voorafgaand aan de introductie van Raman-spectroscopie als in-line metrologietools in de fab, leidde tot testen in veel latere stadia van het fabricageproces."

Uiteindelijk zijn er voor een grondige inspectie geen bezuinigingen. Budgetberekeningen kunnen vergelijkende statistieken vereisen, zoals de initiële kosten van een nieuw instrument versus de lopende kosten van buitensporige RMA's. En er is nog een ding om over na te denken: hoe u ervoor kunt zorgen dat u uw gegevens kunt vertrouwen.

“Gaat u waarschijnlijk goed materiaal weggooien om er zeker van te zijn dat u geen probleemmateriaal overhoudt in wat u doorgeeft aan de eindgebruiker? Wie gaat de kosten daarvan dragen?” waarschuwde Mike McIntyre, directeur softwareproductbeheer bij Op naar innovatie, die een statistische database aanbeveelt voor nauwkeurige vergelijkende beoordeling bij het uitvoeren van geautomatiseerde defectclassificatie.

kromtrekken

Een van de ergste gevolgen van stress is kromtrekken. Het is misschien verrassend dat warpage moeilijk te detecteren is, maar het effect is niet altijd zo duidelijk als het lijkt. Warpage veroorzaakt kleine verschillen in coplanariteit tussen chip en substraat, waardoor sommige microbumps onvoldoende verbinding maken met de pads eronder, een storing die niet-nat wordt genoemd.

"Denk bijvoorbeeld aan een geavanceerde processor van 50 tot 60 mm", zegt Chen. “Vanwege zijn grote omvang is het een uitdaging om het zonder kromtrekken te verwerken. Desalniettemin, als het stansgereedschap is afgestemd op het midden van het procesvenster, kan het de inspectie doorstaan en met hoge opbrengsten worden vervaardigd. Het probleem is dat de tolerantie erg smal kan zijn. Zodra je een beetje kanteling bovenop de warpage hebt, heb je niet-natte problemen.

Erger nog, als dit gebeurt bij hobbels in het bereik van 50 µm (̴35 µm hobbelgrootte), stelt u zich de problemen voor als de afmetingen van de hobbels verder verkleinen. Het is al een punt van zorg voor de auto-industrie, aangezien deze op weg is naar de volgende generatie in 2023 tot 2024. De kritieke overgang zal rond het 28nm-knooppunt plaatsvinden, zei Chen.

Afb. 1 Die-attach-gereedschappen hebben een zeer smal procesvenster voor het kantelen van de matrijs wanneer er kromtrekken is. Bron: Bruker

Niet nat

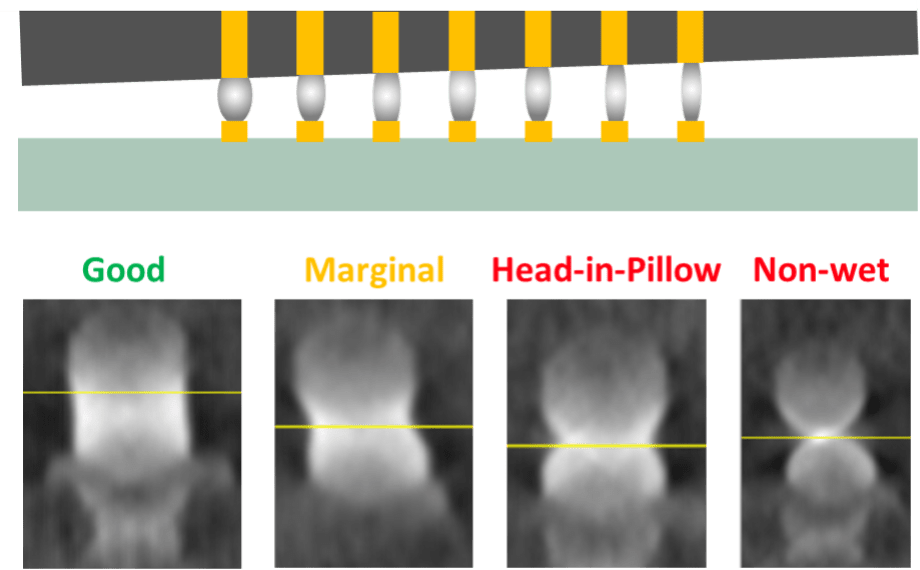

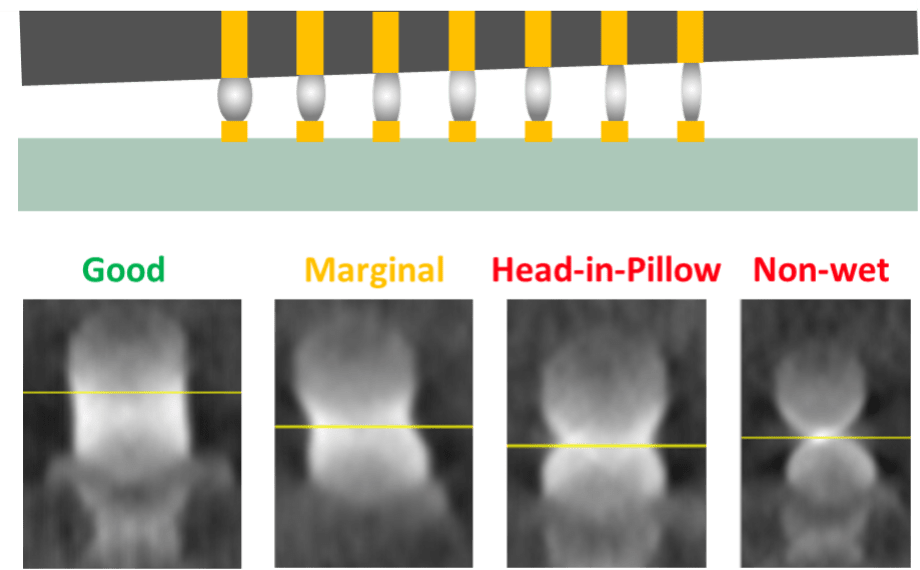

"Non-wets" is een brede term die verschillende problemen dekt die kunnen optreden met soldeerbultjes, waarvan de meeste frustrerend subtiel zijn. Omdat soldeer vaak in vloeibare toestand is, wordt het aanbrengen ervan "bevochtigen" genoemd. Zwakke links worden "non-wets" genoemd, wat een grotere uitdaging wordt bij kleinere knooppunten met dunnere verbindingen.

Non-wets ontsnappen vaak aan typische screeningprocessen, maar verschijnen later als geretourneerde chips (RMA's). De grondoorzaken kunnen thermisch, mechanisch of een combinatie zijn, zoals thermisch fietsen in een auto die ook over ruw terrein rijdt. Het cumulatieve effect kan voldoende thermisch-mechanische spanning opleveren om het contact te verbreken.

Er zijn extra bijnamen die specifieke soorten problemen beschrijven. In plaats van de gladde, zuilvormige vorm van een goede verbinding, lijkt bij een "head-in-pillow"-defect de ene bal in de andere weg te zinken, als een hoofd op een kussen.

"Het maakt nog steeds contact, dus de elektrische test kan goed zijn, maar je kunt zien dat het erg kwetsbaar is," zei Chen, wijzend naar de röntgenfoto van een hoofd-in-kussen. “Zodra je thermische belasting of mechanische belasting krijgt, kan het volledig breken. Zelfs als het een contact is dat niet nat is, leidt de dunne verbinding tot hoge weerstand, suboptimale prestaties en zal waarschijnlijk niet lang meegaan. Een open niet-nat werkt helemaal niet. In een typisch scenario met die tilt is er een zichtbare overgang van goed gevormde hobbels naar niet-nat.

Het kritieke probleem zijn latente defecten - verbindingen die functioneel genoeg zijn om de elektrische test te doorstaan, maar falen in het veld.

Fig. 2 Geleidelijke overgang van goede hobbels naar niet-natte stukken in de aanwezigheid van kanteling van de matrijs. Bron: Bruker

"Het is op dit moment een groot probleem met veel soorten apparaten vanwege de effecten van thermische stress", zegt Chen. “Eén klant had een product dat door de e-testscreening kwam en werd verzonden. Helaas hadden ze veel RMA's vanwege non-wets-storingen die zich daarna ontwikkelden.

Sommige bedrijven pakken dit aan door middel van tergend vervelende handmatige inspecties. Helaas is elk menselijk onderzoek onderhevig aan vermoeidheid van de operator, vooral wanneer examinatoren tijdens een dienst van meerdere uren subtiele fouten proberen op te sporen.

Aan de positieve kant zijn er nu geautomatiseerde benaderingen van inspectie, zoals röntgenapparatuur die inline kan worden gebruikt. "Er is een grote drijfveer voor snelle, volledig geautomatiseerde inspectie om <100 dppb te bereiken, vooral voor de auto-industrie", aldus Chen.

Vanaf daar wordt het ingewikkelder. "Met name soldeer, de boosdoener achter veel non-wets, is ook onderhevig aan elektromigratie", zegt Tom Marinis, een hoofdlid van de technische laboratoriumstaf bij Draper. “Als de stroomdichtheid in een verbinding tussen een chip en substraat gedurende een bepaalde periode te hoog is voor een bepaald soldeersel, omdat de smelttemperatuur van het soldeer relatief laag kan zijn in vergelijking met de bedrijfstemperatuur van het apparaat, kun je migratie krijgen van de atomen en eigenlijk leegtes vormen en uiteindelijk een verbinding openen.”

Marinis waarschuwde dat commerciële modelleringstools op apparaat-PCB-niveau niet helemaal volwassen genoeg zijn om consistent te waarschuwen voor mogelijke elektromigratieproblemen, dus het is belangrijk om nog steeds een versnelde verouderingstest uit te voeren.

Conclusie

Uiteindelijk vereist het detecteren van betrouwbaarheidsproblemen door latente defecten een hogere bemonsteringsmetrologie die gevoelig is voor matrijsverschuiving, rotatie, hoogte, kanteling en andere parameters. Het vereist ook meer afhankelijkheid van multi-fysica-modellering om te proberen mogelijke problemen vóór productie te anticiperen en op te lossen. En terwijl de halfgeleider- en auto-industrie zich blijven vermengen, staat er veel meer op het spel dan alleen RMA's.

"De kosten van falen nemen exponentieel toe naarmate verborgen defecten overgaan van apparaten naar modules naar auto's die het leven van mensen in gevaar kunnen brengen", aldus Chen. Daarom creëren chipmakers holistische oplossingen die ontwerp, inspectie en testen combineren om latente fouten beter op te vangen.

- Door SEO aangedreven content en PR-distributie. Word vandaag nog versterkt.

- Platoblockchain. Web3 Metaverse Intelligentie. Kennis versterkt. Toegang hier.

- Bron: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- versneld

- Volgens

- nauwkeurigheid

- accuraat

- Bereiken

- actieve

- werkelijk

- toevoeging

- Extra

- aanpakken

- vergevorderd

- Veroudering

- Alarm

- Alles

- toestaat

- al

- Hoewel

- altijd

- analyse

- en

- Nog een

- anticiperen

- toepasselijk

- toepassingen

- Het toepassen van

- nadering

- benaderingen

- GEBIED

- gebieden

- rond

- bijeenkomst

- beoordeling

- geassocieerd

- hechten

- geautomatiseerde

- automotive

- auto-industrie

- slecht

- bal

- gebaseerde

- basis

- Beer

- omdat

- worden

- worden

- vaardigheden

- achter

- wezen

- onder

- BEST

- Wedden

- Betere

- tussen

- Verder

- Groot

- groter

- Beetje

- Breken

- breed

- begroting

- bebouwd

- ingebouwd

- bedrijfsdeskundigen

- zakelijke ontwikkeling

- Dit betekent dat we onszelf en onze geliefden praktisch vergiftigen.

- Kan krijgen

- auto

- auto's

- geval

- het worstelen

- Veroorzaken

- oorzaken

- veroorzakend

- Centreren

- CFD

- uitdagen

- uitgedaagd

- uitdagingen

- uitdagend

- kansen

- Wijzigingen

- karakteriseren

- chen

- spaander

- chips

- keuzes

- klassiek

- classificatie

- combinatie van

- combinaties

- combineren

- gecombineerde

- combineren

- hoe

- commercieel

- Gemeen

- Bedrijven

- vergeleken

- compleet

- complex

- ingewikkeld

- bestanddeel

- Bezorgdheid

- voorwaarden

- Verbinden

- versterken

- aansluitingen

- Overwegen

- contact

- voortzetten

- Kern

- hoeken

- Kosten

- kon

- aan het bedekken

- en je merk te creëren

- aangemaakt

- creëert

- Wij creëren

- kritisch

- Actueel

- Op dit moment

- klant

- Klanten

- snijdend

- gegevens

- Database

- omgang

- dichtheid

- beschrijven

- Design

- ontwerpen

- gedetailleerd

- ontwikkelen

- ontwikkelde

- Ontwikkeling

- apparaat

- systemen

- De

- verschillen

- anders

- Moeilijkheid

- digitaal

- digitale tweeling

- Afmeting

- directe

- direct

- Director

- doen

- Dont

- beneden

- manufacturier

- bestuurder

- nagesynchroniseerde

- gedurende

- dynamica

- Vroeg

- effect

- duurt

- doeltreffendheid

- inspanningen

- Elektronica

- nadruk

- Engineering

- genoeg

- verzekeren

- uitrusting

- fouten

- vooral

- etc

- Ether (ETH)

- Zelfs

- uiteindelijk

- alles

- voorbeeld

- uitvoerend

- uitbreiding

- verwacht

- ervaren

- uitgelegd

- Nagegaan

- exponentieel

- uiterst

- FAIL

- Storing

- snelste

- 피로

- Voordelen

- kameraad

- weinig

- veld-

- Vijg

- Figuur

- Tot slot

- VIND DE PLEK DIE PERFECT VOOR JOU IS

- het vinden van

- Voornaam*

- stroom

- formulier

- gevonden

- oppompen van

- frustrerend

- functioneel

- verder

- generatie

- krijgen

- Goes

- gaan

- goed

- geleidelijk

- Groeiend

- Groeit

- Behandeling

- Hard

- hoofd

- Hoogte

- hulp

- helpt

- Hoge

- hoger

- zeer

- holistische

- Hopelijk

- Populair

- Hoe

- How To

- HTTPS

- menselijk

- Hybride

- Effecten

- belangrijk

- in

- Inclusief

- Laat uw omzet

- meer

- industrieën

- -industrie

- eerste

- verkrijgen in plaats daarvan

- instrument

- integratie

- Introductie

- onderzoek

- geïsoleerd

- kwestie

- problemen

- IT

- zelf

- Soort

- laboratorium

- Groot

- grootschalig

- groter

- Achternaam*

- lagen

- Legkippen

- leiden

- leidend

- Leads

- LED

- Niveau

- bibliotheken

- Waarschijnlijk

- links

- Vloeistof

- Lives

- lang

- lot

- Laag

- onderhouden

- maken

- maken

- management

- manager

- handboek

- geproduceerd

- veel

- kaart

- Mario

- matching

- materiaal

- materieel

- volwassen

- max-width

- middel

- maten

- het meten van

- mechanisch

- lid

- Metalen

- methode

- methodologieën

- Metriek

- Metrologie

- macht

- migratie

- vermenging

- modellering

- module

- Modules

- meer

- meest

- beweegt

- meervoudig

- nano

- nodig

- nodig

- negatief

- niettemin

- New

- Nieuwe technologieën

- nieuws

- volgende

- knooppunt

- knooppunten

- Voor de hand liggend

- het aanbieden van

- EEN

- lopend

- open

- werkzaam

- operator

- optimalisatie

- Opties

- bestellen

- Overige

- pakket

- Paketten

- verpakking

- Pijn

- parameters

- bijzonder

- vooral

- voorbij

- mensen

- uitvoeren

- prestatie

- periode

- fase

- Fysiek

- standplaatsen

- Plato

- Plato gegevensintelligentie

- PlatoData

- Spelen

- spelers

- punt

- punten

- polymeren

- portfolio

- positief

- mogelijk

- potentieel

- praktijk

- aanwezigheid

- president

- het voorkomen van

- Principal

- Voorafgaand

- waarschijnlijk

- sonde

- probleem

- problemen

- processen

- Gegevensverwerker

- Product

- product management

- Productie

- Programma

- bewijs

- naar behoren

- vastgoed

- prototype

- zorgen voor

- mits

- zetten

- R & D

- reeks

- snel

- vast

- recent

- beveelt

- verminderen

- vermindert

- afspiegeling

- relatief

- betrouwbaarheid

- vertrouwen

- vernieuwd

- vereisen

- vereist

- onderzoek

- onderzoek en ontwikkeling

- resultaat

- verkregen

- Resultaten

- Risico

- risico's

- rollen

- wortel

- lopen

- Zei

- zegt

- balans

- het scannen

- scenario

- doorlichting

- seconden

- lijkt

- segment

- selectie

- halfgeleider

- senior

- gevoelig

- verscheidene

- Shadow

- Vorm

- verschuiving

- VERSCHUIVEN

- verscheept

- Bermuda's

- tonen

- Signaal

- aanzienlijke

- aanzienlijk

- simulatie

- Maat

- maten

- Klein

- kleinere

- So

- Software

- Oplossingen

- sommige

- Spoedig

- bron

- specifiek

- Spectroscopie

- Spot

- Medewerkers

- Stadium

- stadia

- inzet

- begin

- Land

- statistisch

- Still

- spanning

- structureel

- structuur

- onderwerpen

- geslaagd

- dergelijk

- verrassend

- Technisch

- technieken

- Technologies

- proef

- Testen

- De

- De omgeving

- hun

- Er.

- warmte-

- ding

- spullen

- duizenden kosten

- Door

- Het werpen

- niet de tijd of

- keer

- naar

- samen

- tolerantie

- ook

- tools

- tools

- top

- in de richting van

- overgang

- Trust

- BEURT

- types

- typisch

- begrijpen

- komende

- bijwerken

- .

- Gebruiker

- divers

- groot

- Vice President

- zichtbaar

- bekend

- Wat

- welke

- en

- WIE

- wil

- zonder

- Mijn werk

- Slechtst

- zou

- röntgenstraal

- opbrengsten

- Your

- zephyrnet