わずか 1.0 年以上前、PCI Express 2002 の導入により、業界は当時ユビキタスだったパラレル インターフェイスからシリアル インターフェイスへの移行を迎えました。 XNUMX 年当時、車載コンピューティングの当時の現状と、PCIe が主にデスクトップおよびデータセンターでの使用に焦点を当てていたことを考慮すると、車載アプリケーションにおける「PCIe」の可能性は予想外でした。しかし今日では、人間に近い (敢えて言えば超人間的?) 自動運転能力を備えたコネクテッド カーの出現により、「なぜ今自動車に PCIe を組み込むのか?」という疑問は少なくなりました。 「なぜ自動車業界が PCIe を使用するのにこれほど時間がかかったのですか?」

自動車エレクトロニクスは年々複雑化しています。アダプティブ クルーズ コントロール (車両が速度を調整して、前の車両との一定の距離を維持する機能) は、少し前までは高級高級車専用のものでした。今日では、中産階級の家族が車を購入し、渋滞の中や周りを自動で操縦し、自分で駐車スペースを見つけて占有し、所有者に呼ばれるまでそこで待つことができる世界では、これは奇妙なギミックに思えます。これを達成するためのセンサー データ、カメラ画像、および純粋な計算能力の量は単に驚異的であり、一部の研究者は 200 台の車両のデータ スループットが XNUMX Gbps に近いと計算しています。

信頼性は常に自動車システムの基本的な要件です。かつての自動車広告では、目的地まで安全に連れて行ってくれるブランドの能力を宣伝しており、消費者は整備工場にいるよりも路上で多くの時間を費やした自動車に群がりました。消費者とその家族は現在、自動車が走行し続ける能力だけでなく、重要な意思決定を下し、人間の能力を超えた運転能力に依存しているため、信頼性への注目はかつてないほど高まっています。自動車環境のすでに困難で急速に変化する温度、湿度、振動に、これらすべての高度なエレクトロニクスによって生成される熱を加えるのは、自動車設計者にとって困難な作業になります。時折起こる「クラッシュ」のためにスマートフォンを再起動することを受け入れる消費者は、当然のことながら、自動車エレクトロニクスの同じ不具合を容赦しません。その結果、現実世界でのクラッシュが容易に発生し、それに応じて深刻な結果が生じる可能性があります。悲しいことに、同じ消費者は、サイバー犯罪と「ハッキング」が日常生活においてますます不快な現実であることをしぶしぶ受け入れていますが、ここでもまた、その結果は最もひどい個人情報の盗難よりもはるかに深刻です。

したがって、現代の車両には高帯域幅、極めて高い信頼性、堅牢なセキュリティを備えた相互接続が必要であることは明らかです。これらはすべて PCI Express 6.0 に共通の特性です。

PCIe帯域幅

PCI Express は当初から、最先端の帯域幅の提供に重点を置いてきました。そのため、現在の PCIe 6.0 仕様が、最も幅の広い (x256) リンクを最高 (16GT) で実行するときに最大 64GB/s を提供することは驚くべきことではありません。 /s) の速度が利用可能です。別の昔の自動車広告についてお詫びしますが、PCIe 4 で定義された新しい FLIT モードと PAM6.0 シグナリングは、「PCIe 6.0 はお父さんの PCI Express 仕様ではありません!」を意味します。以前の PCIe 世代との完全な下位互換性が維持されているため、新しい PAM4 シグナリングは 64GT/s でのみ使用され、従来の NRZ シグナリングは 32GT/s 以下で引き続き使用されます。この新しい速度で許容可能なビット エラー レートを維持するという課題により、PCIe プロトコルが大幅に変更されました。これにより、信頼性を重視する自動車設計者にとって、実際にはさらに魅力的なものになる可能性があります。

新しい固定サイズの FLIT (FLow control unIT) 構造により、前方誤り訂正 (FEC) の使用が可能になります。これにより、データが従来の PCIe エラー処理メカニズムによって処理される前に FLIT 内の複数のエラーを修正することで、実効ビット エラー レートが向上します。この新しい FLIT モードは、PCIe リンクが 64GT/s で動作する場合に必要ですが、定義された任意の PCIe リンク速度で許可されます。 PCIe FLIT の開発はエラー訂正のために必要でしたが、多くの場合、リンク効率の向上という嬉しい副次効果が得られます。パケットごとのオーバーヘッドを FLIT ごとのオーバーヘッドに統合することにより、複数の小さなパケットを単一の FLIT 内で前世代の PCIe よりもさらに効率的に転送できます。

PCIe 6.0 デバイスは、最新の 64GT/s リンク速度で動作している場合でも、PCIe 6.0 基本仕様で完全に定義されサポートされているそれより低いリンク速度のいずれかで動作している場合でも、可能な限り最高の帯域幅を利用できます。

PCIeの信頼性

最初のリリース以来、PCIe は本質的に信頼性の高い配信メカニズムを提供してきました。すべての PCIe パケットには、受信時にすぐに検証されるリンクレベルの巡回冗長検査 (LCRC) が含まれています。 ACK/NAK (確認応答/非確認応答) プロトコルは、エラーのあるパケットのシームレスなハードウェア再送信を提供し、リンクの切断が見逃されないようにするためのタイムアウトを備えています。上で述べたように、PCIe リンクが FLIT モードで動作しているときは、LCRC がチェックされる前であっても、適用される FEC の使用によって追加の保護層が提供され、エラーが修正される可能性があります。これらのチェックに失敗したパケットは受信機によって NAK され、送信機による自動再送信がトリガーされます。このデータ転送のハードウェア管理により、ソフトウェア開発者は、個々の転送の配信について心配する必要がなく、PCIe 接続のデバイスをあたかも CPU に直接接続されているかのように使用できるようになります。

PCIe 6.0 には、レーン マージニング機能 (PCIe 4.0 で導入) が含まれており、すべての PCIe コンポーネントが受信している「良好な」信号と障害点との間にあるマージンの量を報告する標準化されたメカニズムを提供します。この機能を使用すると、コンポーネントの耐用年数全体にわたって潜在的な信号品質の低下を追跡し、信号パラメータの再調整、リンク速度の低下、さらには障害を事前に予防するコンポーネントの交換など、事前の障害軽減策をトリガーすることができます。

PCI Express は、ベンダー定義メッセージ (VDM) を利用して PCIe プロトコルをさまざまな方法で拡張するオプションを提供します。自動車設計者は、これらの VDM をハートビート情報、帯域内管理、および PCIe 車載システム全体の信頼性に貢献できるその他の多くの機能に使用できます。

PCIeセキュリティ

自動車の分野では、「インターフェイス セキュリティ」という言葉から、映画の秘密諜報員が自動運転車をハッキングして崖から転落させ、派手に爆発させて悪の天才たちを暗殺するというビジョンが思い浮かぶかもしれませんが、実際には、その背後には複数の現実世界のシナリオがあります。安全な PCIe リンクに移動します。他国の兵器を破壊するためにサイバー攻撃を行った国家が見つかった世界では、「暗殺のためのハッキング車両」という映画のプロットを完全に排除すべきではありませんが、窃盗というもっと単純な利益動機は、賢明な窃盗犯にそのような動機を与えるでしょう。ハッキング。自動車メーカーが無線周波数リモートロック解除システムなどの従来の盗難防止メカニズムのセキュリティ脆弱性をどんどん解決しているため、窃盗犯は必然的に、PCIe インターコネクトが魅力的な攻撃点となる可能性がある車両内部の奥深くに注意を向ける必要があります。同様に見落とされがちなのが、デジタル著作権管理を実施するためのインターフェース セキュリティの考え方です。この場合、「攻撃者」は、自動運転などの有料機能のロックを解除しようとする「攻撃」対象の車両に時間無制限で自由にアクセスできる車両所有者である可能性があります。 。

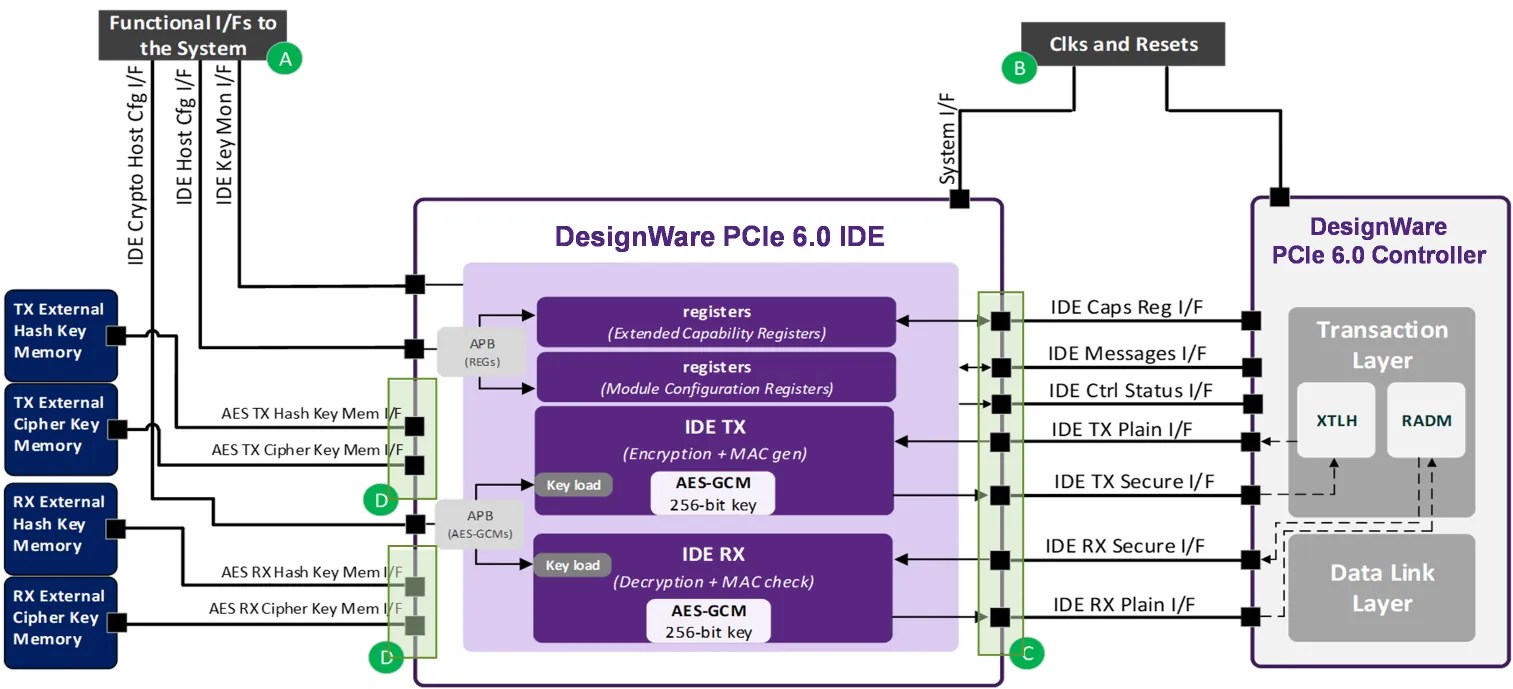

これらおよびその他の要因は、自動車設計者がすべての内部インターフェイスを攻撃ベクトルの可能性があると考慮する必要があることを意味します。 PCI Express には、Integrity and Data Encryption (IDE) と呼ばれる機能が含まれており、これにより、PCIe デバイスは、PCIe リンクを介して転送されるパケットに対してハードウェア暗号化と整合性チェックを実行できます。基本的に、IDE は、高度なツールと被害者のシステムへの直接アクセスを使用して、熟練した攻撃者が実行するハードウェア レベルの攻撃から保護します。 PCIe パケットは、AES-GCM 暗号化アルゴリズムで個別に暗号化および認証され、データの機密性と整合性が確保されます。 IDE 仕様内のメカニズムは、PCIe プロトコル スタック全体で機能し、再試行の強制や、同じデータの繰り返し送信を強制して使用されている暗号キーを暴露しようとする不良パケットの挿入など、PCIe 固有の攻撃から保護します。このような低レベルのプロトコルの相互作用のため、保護メカニズムの利点を最大限に活用し、最適なソリューションを提供するには、IDE を PCIe コントローラーと連携して実装する必要があります。整合性チェックの結果、IDE によって保護された PCIe リンクは、さらに 1 層の信頼性チェックの恩恵を受けることになります。これは、IDE で保護された PCIe パケットの悪意のない変更であっても、システム レベルの応答がトリガーされるためです。

図 1: PCIe コントローラー内の Synopsys IDE 実装例。

まとめ

今日のコネクテッドカーは、高帯域幅、極めて高い信頼性、堅牢なセキュリティを備えた相互接続を必要とする計算プラットフォームとアーキテクチャに依存しています。 PCI Express 6.0 は、レーンあたり最大 64GT/s のシグナリング、信頼性の高い配信のための多数のハードウェア メカニズム、および完全性チェックによる完全なデータ暗号化を組み合わせることで、これらの要件を満たす独自の立場にあります。シノプシスのオファー IDE セキュリティ モジュールを備えた PCIe 6.0 および 5.0 コントローラー ISO 26262 および ASIL 認証のオプションとともに、SoC 設計者が PCIe 上のデータ転送を改ざんや物理的攻撃から保護できるようにします。 PCI Express 用のシノプシス IP はこれらすべての機能をサポートし、自動車設計者が次の製品で PCIe 6.0 を利用できるようにします。

リチャード・ソロモン

Richard Solomon は、Synopsys の DesignWare PCI Express コントローラー IP のシニア テクニカル マーケティング マネージャーです。彼は、NCR 53C810 および PCI 仕様の 1.0 以前のバージョンに遡る PCI チップの開発に携わってきました。シノプシスに入社する前は、Solomon は LSI のストレージ RAID コントローラ チップ シリーズで使用される PCI Express および PCI-X インターフェイス コアの設計と開発を主導していました。彼は 10 年以上 PCI-SIG の取締役を務めており、現在は PCI-SIG の副社長を務めています。彼はライス大学で BSEE を取得しており、25 件の米国特許を取得していますが、その多くは PCI テクノロジーに関連しています。

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- PlatoData.Network 垂直生成 Ai。 自分自身に力を与えましょう。 こちらからアクセスしてください。

- プラトアイストリーム。 Web3 インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- プラトンESG。 カーボン、 クリーンテック、 エネルギー、 環境、 太陽、 廃棄物管理。 こちらからアクセスしてください。

- プラトンヘルス。 バイオテクノロジーと臨床試験のインテリジェンス。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/why-are-automotive-soc-designers-turning-to-pci-express-6-0/

- :持っている

- :は

- :not

- :どこ

- $UP

- 1

- 10

- 12

- 25

- 33

- a

- 能力

- 能力

- 私たちについて

- 上記の.

- 同意

- ことができます。

- 一般に認められた

- アクセス

- こちらからお申し込みください。

- 越えて

- 実際に

- 適応

- 追加

- NEW

- 高度な

- 利点

- 出現

- 広告

- 再び

- に対して

- エージェント

- 前

- アルゴリズム

- すべて

- 全ての記事

- ことができます

- 沿って

- 既に

- また

- 常に

- 量

- an

- および

- 別の

- どれか

- 訴える

- 適用された

- アプローチ

- です

- 周りに

- AS

- At

- 攻撃

- 攻撃

- 試み

- 注意

- 魅力的

- 属性

- 認証された

- オートマチック

- 自動車

- 自動車

- 自動車

- 自律的

- 利用できます

- バック

- 悪い

- 帯域幅

- ベース

- BE

- になる

- き

- 背後に

- さ

- 以下

- 恩恵

- の間に

- 越えて

- ビット

- ボード

- 取締役会

- 壊れた

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 計算

- 呼ばれます

- 呼び出し

- カメラ

- 缶

- 容量

- 自動車

- 自動車

- 例

- キャッチ

- センター

- 認証

- 課題

- 挑戦

- 変更

- 変化

- チェック

- チェック済み

- 点検

- 小切手

- チップ

- クラシック

- クリア

- 閉まっている

- 結合

- コマンドと

- 互換性

- 完全に

- 複雑さ

- コンポーネント

- コンポーネント

- 計算

- 計算的

- 計算能力

- 実施

- 秘密

- 交流

- 結果

- 検討

- 統合

- 消費者

- 貢献する

- コントロール

- コントローラ

- 訂正さ

- 可能性

- CPU

- Crash

- 重大な

- 暗号

- 電流プローブ

- 現在

- サイバー攻撃

- サイバー犯罪

- daily

- データ

- データセンター

- 年代測定

- 数十年

- 決定

- より深い

- 定義済みの

- 配信する

- 配達

- 依存

- デザイナー

- デスクトップ

- デスティネーション

- 開発者

- 開発

- Devices

- DID

- デジタル

- デジタル著作権

- 直接

- 直接アクセス

- 直接に

- 取締役

- 混乱する

- 距離

- do

- ドライブ

- 運転

- 原因

- 簡単に

- 効果的な

- 効率

- 効率良く

- 電子

- enable

- では使用できません

- 暗号化

- 強制します

- 確保

- 環境

- エラー

- エラー

- さらに

- あらゆる

- 邪悪な天才

- 例

- 特別

- 詳細

- 表現します

- 極端な

- 要因

- フェイル

- 不良解析

- 家族

- 家族

- 遠く

- ファッション

- 特徴

- 特徴

- 発見

- 名

- フロー

- フォーカス

- 焦点を当て

- 強

- 強制

- フォワード

- 無料版

- 周波数

- から

- フロント

- 満たす

- フル

- 完全に

- 機能

- 基本的な

- 根本的に

- 世代

- 取得する

- 与える

- 与えられた

- Go

- ハッキング

- ハンドリング

- Hardware

- 持ってる

- he

- 助けます

- こちら

- ハイ

- ハイエンド

- より高い

- 最高

- 保持している

- しかしながら

- HTTP

- HTTPS

- 人間

- i

- アイデア

- アイデンティティ

- 個人情報の盗難

- if

- 直ちに

- 実装

- 実装

- 改善

- 向上させる

- in

- 誘因

- 開始

- 含ま

- 組み込む

- の増加

- 個人

- 個別に

- 産業を変えます

- 業界の

- 情報

- 本質的に

- 内部

- 整合性

- 意図

- 相互作用

- 相互接続

- インタフェース

- インターフェース

- 内部

- に

- 導入

- 概要

- 関係する

- IP

- ISO

- IT

- ITS

- 自体

- 参加

- ただ

- キープ

- キー

- レーン

- 最新の

- 層

- ツェッペリン

- less

- 生活

- ような

- LINE

- LINK

- リンク

- 命

- 長い

- 下側

- 贅沢

- 維持する

- 保守

- make

- 作る

- 管理

- マネージャー

- メーカー

- 多くの

- マージン

- マークされた

- マーケティング

- 最大幅

- 五月..

- 意味する

- メカニズム

- メカニズム

- メッセージ

- かもしれない

- 緩和

- モード

- モダン

- 他には?

- 最も

- 動機

- 安全に移動

- 映画

- ずっと

- の試合に

- しなければなりません

- 国連

- NCR

- 必ずしも

- 必要

- 決して

- 新作

- 次の

- いいえ

- 注意

- 今

- 多数の

- 時折

- 占める

- of

- オフ

- 提供

- オファー

- 頻繁に

- on

- ONE

- の

- 操作する

- オペレーティング

- 最適な

- オプション

- オプション

- or

- その他

- さもないと

- でる

- が

- 全体

- 所有者

- パケット

- 支払われた

- 並列シミュレーションの設定

- パラメータ

- パーキング

- 特許

- 以下のために

- 実行する

- PHP

- 物理的な

- プラットフォーム

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポイント

- 配置された

- 可能

- 投稿

- 潜在的な

- :

- 電力

- 社長

- 前

- 主要な

- 事前の

- 先を見越した

- 処理されました

- 生産された

- 製品

- 利益

- 守る

- 保護

- 保護

- 提供します

- 提供

- は、大阪で

- 購入

- 品質

- 質問

- ラジオ

- RAID

- 急速に

- レート

- 価格表

- 現実の世界

- 現実

- realm

- 受け入れ

- 削減

- リリース

- 信頼性

- 信頼性のある

- 頼る

- 残っている

- リモート

- 繰り返される

- 置換

- レポート

- 必要とする

- の提出が必要です

- 要件

- 要件

- 研究者

- 応答

- 結果

- 再送信

- 米

- 権利

- ロード

- 堅牢な

- ルール

- ランニング

- s

- 悲しげに

- 安全に

- 同じ

- 精通した

- 言う

- シナリオ

- シームレス

- 秘密

- 安全に

- セキュア

- セキュリティ

- と思われる

- 自動運転

- シニア

- センサー

- シリアル

- サービスを提供

- セッションに

- 厳しい

- オンラインストア

- シグナル

- 信号

- 重要

- 単に

- から

- 熟練した

- 小さい

- スマートフォン

- So

- ソフトウェア

- ソフトウェア開発者

- ソリューション

- 一部

- 洗練された

- スペース

- 仕様

- 壮大な

- スピード

- 速度

- 費やした

- スタック

- 驚異的な

- 標準化されました

- 都道府県

- 最先端の

- まだ

- ストレージ利用料

- 構造

- そのような

- サポート

- サポート

- 驚き

- システム

- 取る

- 仕事

- 技術的

- テクノロジー

- より

- それ

- 盗難

- アプリ環境に合わせて

- そこ。

- ボーマン

- 彼ら

- この

- それらの

- 全体

- スループット

- 時間

- 〜へ

- 今日

- 豊富なツール群

- 宣伝した

- 追跡する

- 伝統的な

- トラフィック

- 転送

- 転送

- 遷移

- トリガー

- 順番

- ターニング

- 2

- 私達

- 下

- 思いがけない

- 独特に

- 単位

- 大学

- 無限の

- ロック解除

- まで

- に

- つかいます

- 中古

- 活用

- 自動車

- 車

- ベンダー

- 検証

- バイス

- 副会長

- 被害者

- ビジョン

- 脆弱性

- 待つ

- ました

- 方法

- we

- 兵器

- webp

- WELL

- した

- いつ

- かどうか

- which

- while

- 誰

- なぜ

- 意志

- 以内

- 無し

- 仕事

- 世界

- 不安

- でしょう

- 与えるだろう

- 年

- 年

- まだ

- 貴社

- あなたの

- ゼファーネット