SPIE Advanced Lithography Conference が XNUMX 月に開催されました。 最近、imec の先進パターニング プロセスおよび材料担当副社長 Steven Scheer にインタビューし、imec が発表した厳選された論文をレビューする機会がありました。

今年の SPIE での全体的なメッセージは何かとスティーブに尋ねたところ、高 NA への準備が鍵であると彼は言いました。 彼は XNUMX つの主要なエコシステム領域を特定しました。

- マスクおよび解像度強化テクノロジー (RET) インフラストラクチャ。

- 材料、フォトレジストおよび下層。

- 計量

もちろん暴露ツールも重要ですが、スティーブが話しているのはそれではありません。 著者注 – ASML の SPIE プレゼンテーションについても記事を書く予定です。

マスク

スティーブは続けてマスク関連の問題をリストアップしました。

- フォーカス シフトやコントラスト損失などの 3D 効果をマスクします。高 NA は低角度での露光となり、3D 効果がさらに問題になります。

- 欠陥率の低いマスクブランクスと、粗さおよびCDのばらつきが少ないマスク

- Low-n マスクは、より高いコントラストを有効にし、マスクの 3D 効果を軽減するために必要です。

- 光学的近接効果補正技術。

- マスク描画、マルチビーム。

- マスクステッチ – スキャナーフィールドのサイズが小さいため、ダイを縫い合わせる必要があります。

- 一方向に 4 倍、他方向に 8 倍の場合、ステッチングを可能にする新しいタイプのマスク設計が必要です。

- より高いソースエネルギーのためのペリクル。

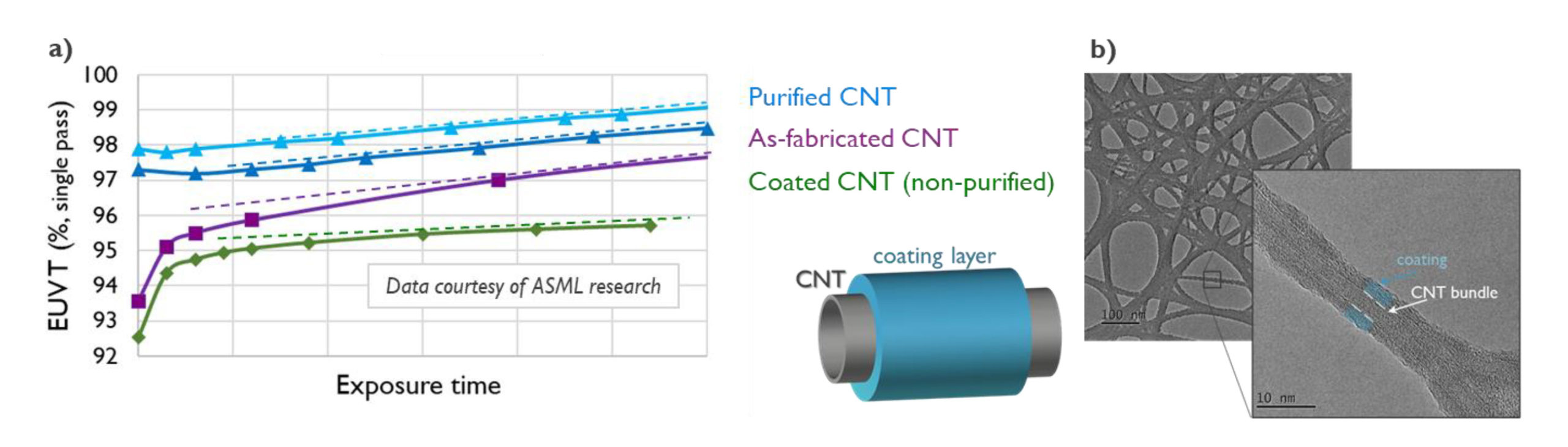

In 「CNT ペリクル: 最近の最適化と暴露の結果」 Joost Bekaert らは、カーボン ナノチューブ ペリクル (CNT) を研究しました。

ASML のロードマップには 600 ワットの電源システムが含まれていますが、金属シリサイドに基づく現在のペリクルは最大約 400 ワットまでしか実行できません。 ペリクルは、粒子をブロックし、高い透過率を持ち、約 110 mm x 140 mm の領域に吊り下げるのに十分な機械的強度を備え、耐久性がある必要があります。 CNT は最大 98% の透過率を示しました。 EUV 放射は非常にエネルギーが高いため、ペリクルをエッチングする水素プラズマを生成し、最終的にはペリクルの機械的完全性の損失につながります。 imec はエッチング速度とペリクルを安定させる方法を評価してきました。

エッチング速度は透過率を調べることで評価できます。エッチングによってペリクルが薄くなるにつれて透過率が増加します。 図 1 は、さまざまな条件下におけるペリクルの時間の経過に伴う透過率を示しています。

ASML は、オフライン プラズマ露光ツールを使用してペリクルの透過率と露光時間を評価します。この研究では、imec が最大 3,000 枚のウェハ (ウェハあたり 96 mJ/cm30 で XNUMX 個のダイ) までの CNT ペリクルの露光を実証し、実際のスキャナ露光から得られた結果間の相関関係を示しました。そしてオフラインツールからのもの。

ペリクルには最初、製造プロセスで発生した揮発性有機不純物が含まれており、燃え尽きるまで EUV エネルギーを吸収します。緑と紫の曲線を参照してください。 ペリクルを高温でベーキングすると、汚染物質が燃焼してペリクルが「浄化」され、その結果、エッチング速度が透過率の変化に影響を及ぼします。 XNUMX つの青い曲線の傾きはエッチング速度によるものです。 緑色の曲線は、より低いエッチング速度を示す「コーティングされた」ペリクルを示していますが、コーティングにより透過率が低下するため、非常に高い出力レベルには対応できない可能性があります。

フォトレジスト

次にスティーブはフォトレジストについて話しました。

フォトレジストの場合、24nm ~ 20nm のピッチが高 NA 挿入のスイートスポットであり、16nm ピッチが究極の解像度となります。 化学増幅レジスト (CAR) は、24nm 未満では性能が低下します。 金属酸化膜レジスト (MOR) は、17nm または 16nm まで有望に見えます。 欠陥は依然として問題です。 24nmピッチの線量は67mJ/cm2 MORおよび77mJ/cmの場合2 車用。 MOR には安定性の問題があり、ドーズ量が低いほどレジストの反応性が高くなり、安定性が低くなります。 これらは課題であり、問題を解決するものではありません。

In 「EUVリソグラフィー用に縮小された堆積下地層」 Guptaらは、フォトレジストの下層を研究した。 ピッチが縮小すると、同じフォトレジスト層でもアスペクト比が増加し、パターンの崩壊につながる可能性があります。 下層の密着性を向上させることで、この問題に対処できます。 あるいは、より薄いフォトレジストを利用してアスペクト比を管理することもできますが、高いエッチング選択性の下層が見つからない限り、エッチングの問題が発生する可能性があります。

imec は、堆積された下層の表面エネルギーをフォトレジストに合わせて接着力を向上できることを発見しました。 堆積された下層の密度調整を利用して、エッチング選択性を改善することができる。

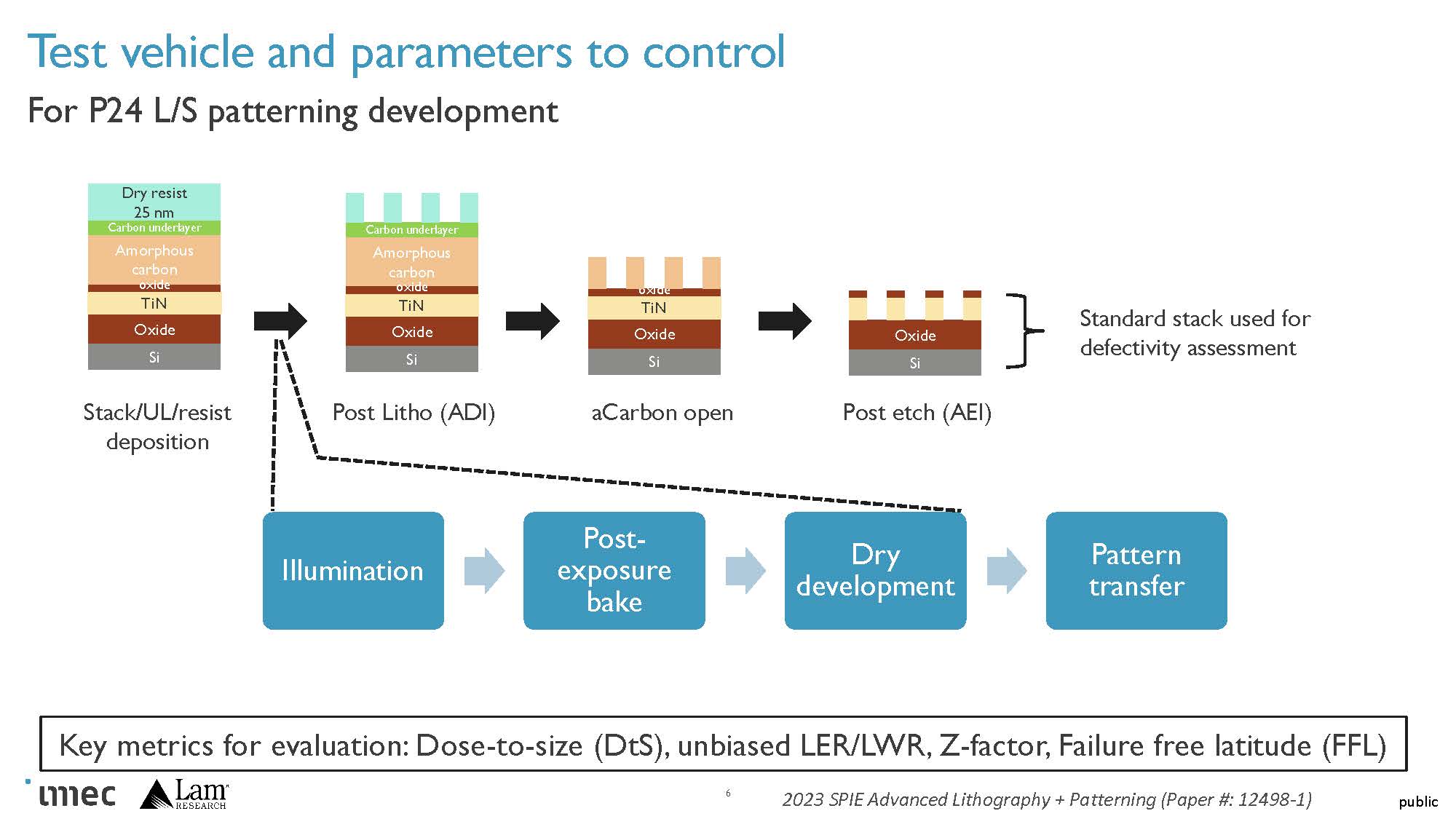

In 「高NA EUVリソグラフィーに向けたドライレジストパターニングの準備」 imecとLamのHyo Sean Suhらは、Lamのドライフォトレジストプロセスを調査した。 N2+ および A14 プロセスの場合、メタル 2 ピッチ (M2P) は 24nm のチップ間 (T15T) で約 2nm になると予想され、A10 では M2P は <22nm T15T で約 2nm になると予想されます。

ラムドライレジストプロセスを図 2 に示します。

露光後ベーク (PEB) は線量低減を強力に促進しますが、ブリッジと粗さに影響を与えることが判明しました。 開発とエッチングを同時に最適化することにより、ブリッジと粗さが軽減され、24nm ピッチの L/S パターニングに対する堅牢なプロセス ウィンドウが示されました。

In 「0.55NA EUVシングルパターニングによるロジックメタルスケーリングの実現可能性」 Dongbo Xu 他は、高 NA (0.55 NA) システムが単一のパターニングで何を達成できるかについての評価を説明しました。

彼らは、24nmピッチは実現可能であると結論付けた。 20nm は水平方向では有望に見えますが、垂直方向ではさらなる作業が必要です。 18nmピッチでは追加の作業が必要です。

EUV は、線の粗さと確率的欠陥の観点から非常に困難な技術であることが証明されています。 Directed Self Assembly (DSA) は、長い間存在しているテクノロジーですが、あまり注目されていません。 DSAはEUVのラインラフネスや確率的欠陥に対処する技術として注目を集めています。

In 「ブロック共重合体による自己組織化による EUV リソグラフィーのラインスペースパターン修正: 粗さと欠陥の研究」 ジュリー・ヴァン・ベル 他DSA と EUV を組み合わせた方が、液浸リソグラフィーに基づく DSA プロセスよりも優れており、線幅の粗さが低く、転位欠陥がないことがわかりました。

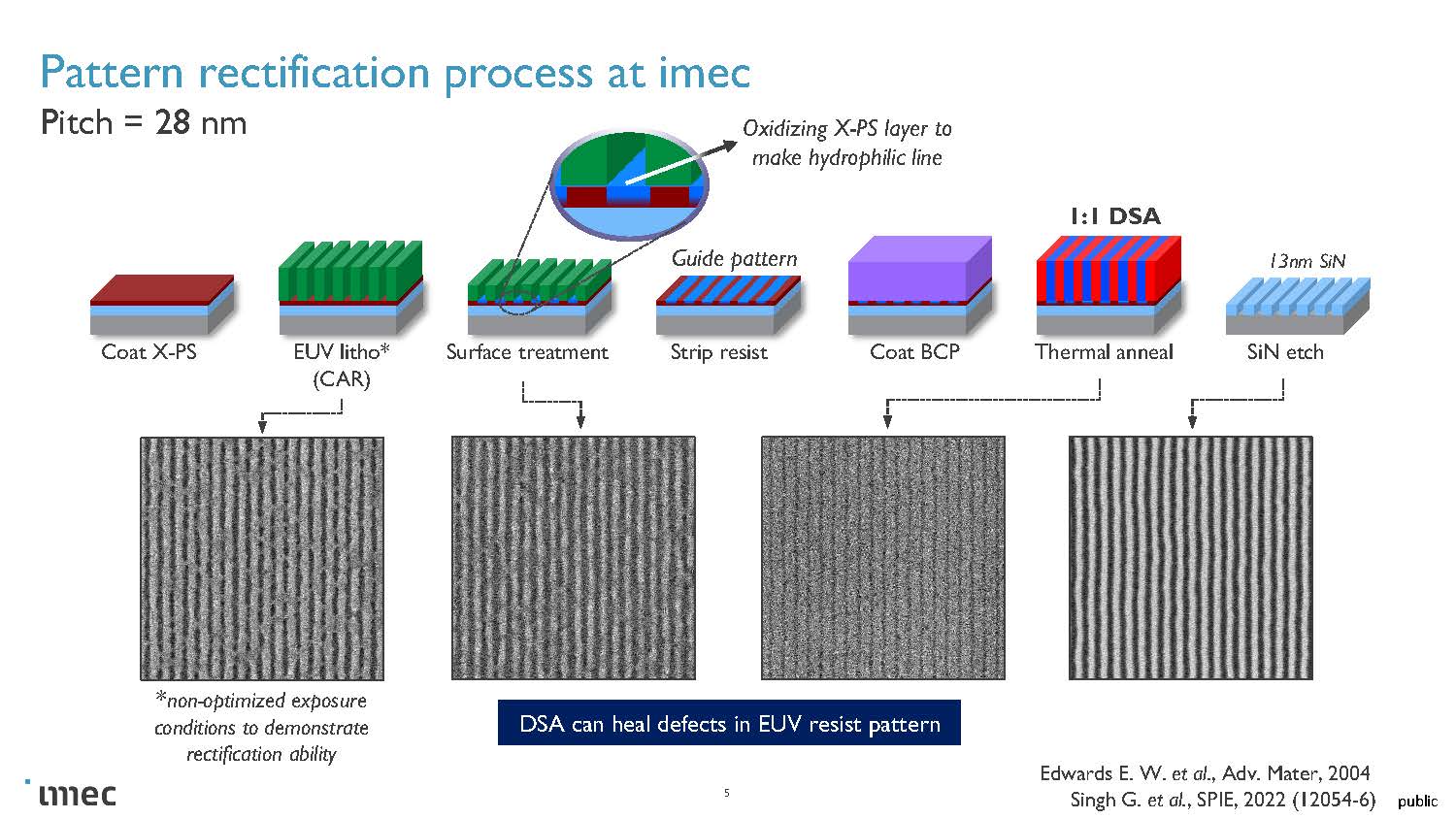

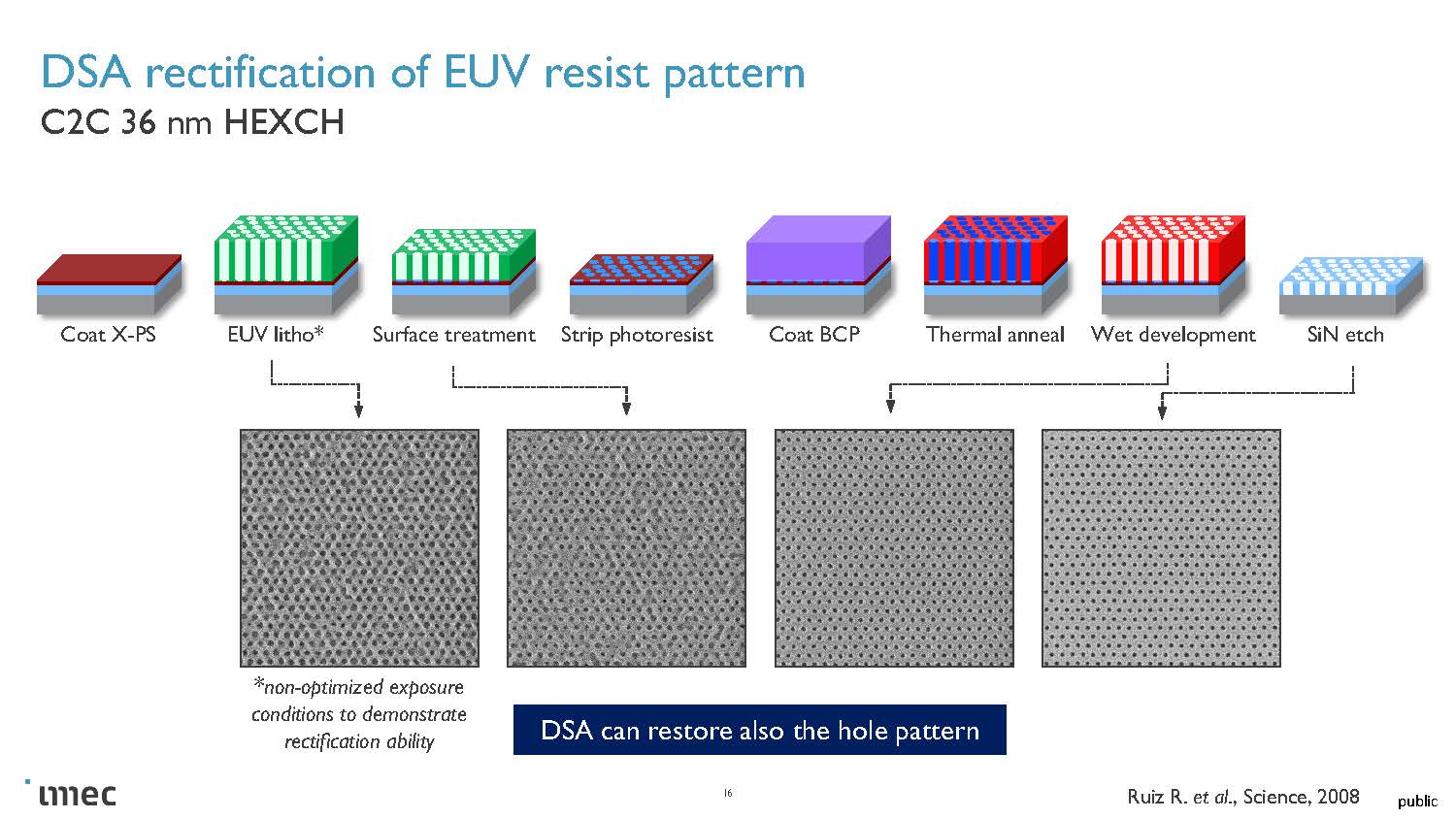

In 「有向自己組織化によるEUVリソグラフィーにおける確率論の軽減」 ランダー・フェルストラエテらEUV 処理における確率的欠陥を軽減するために DSA を使用して調査されました。

ライン/スペース EUV 欠陥を修正する imec プロセスを図 3 に示します。

コンタクトアレイの欠陥を修正する imec プロセスを図 4 に示します。

EUV と DSA は、主な欠陥がブリッジである 28nm ピッチのライン/スペースに対して非常に有望に見えます。 24nm ピッチではブリッジ欠陥が多すぎるため改善が必要です。 欠陥は、ブロックコポリマーの配合とアニール時間に相関します。

コンタクト アレイの EUV + DSA は、局所限界寸法均一性 (LCDU) とパターン配置誤差を改善し、線量の低減を可能にします。

計量

膜厚が減少すると、計測の信号対雑音比が問題になります。

EUV には欠陥プロセス ウィンドウがあり、一方にはパターンの破損が問題となる崖があり、もう一方にはパターン間のブリッジが問題となる崖があります。

新しいピッチを試みると、時間の経過とともに多くの欠陥が解消されます。

十分な感度で十分な面積を測定することは困難です。 E ビーム検査は高感度ですが時間がかかり、光学式検査は高速ですが高感度ではありません。 CFET のような新しい 3D プロセスでは、さらなる課題が生じます。

In 「高NA EUVLに向けたドライレジスト計測の準備」 Gian Francesco Lorusso らは、非常に薄いフォトレジストの特性評価のために原子間力顕微鏡 (AFM)、電子ビーム検査、CD SEM を調査しています。

Lam ドライ フォトレジスト プロセス < CD SEM を使用すると、厚さ 5nm のフォトレジストまで実行可能であることが示されました。 レジストの厚さが減少すると、線の粗さが増加し、ブレーク欠陥は変わらないままブリッジ欠陥の印刷適性が低下しました。 パターンの崩壊は、より厚いフィルムでのみ見られました。 AFM測定により、膜厚の減少が示された。 E ビームは、非常に重要なフィルムであっても欠陥を良好に捕捉することを示しました。

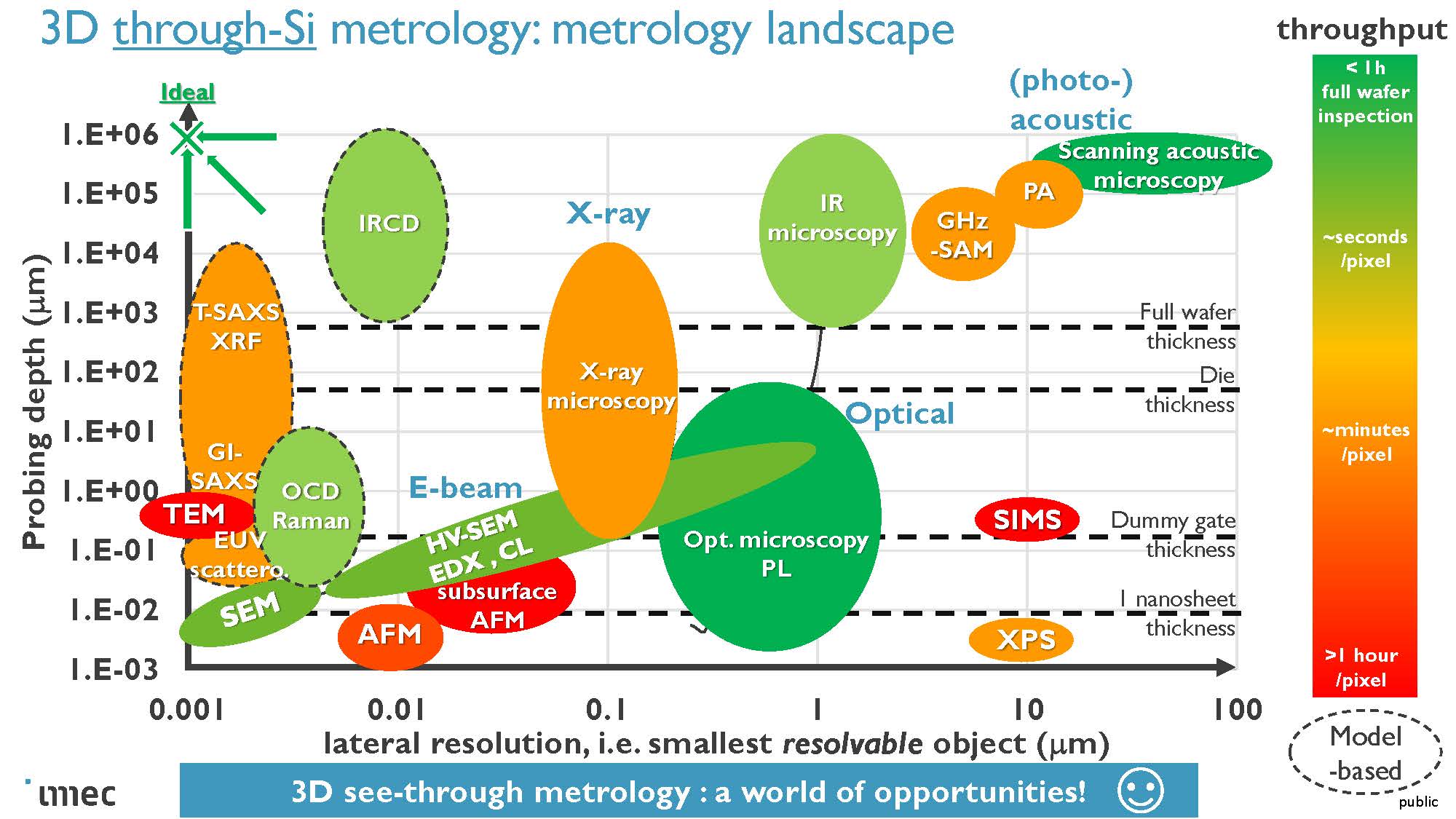

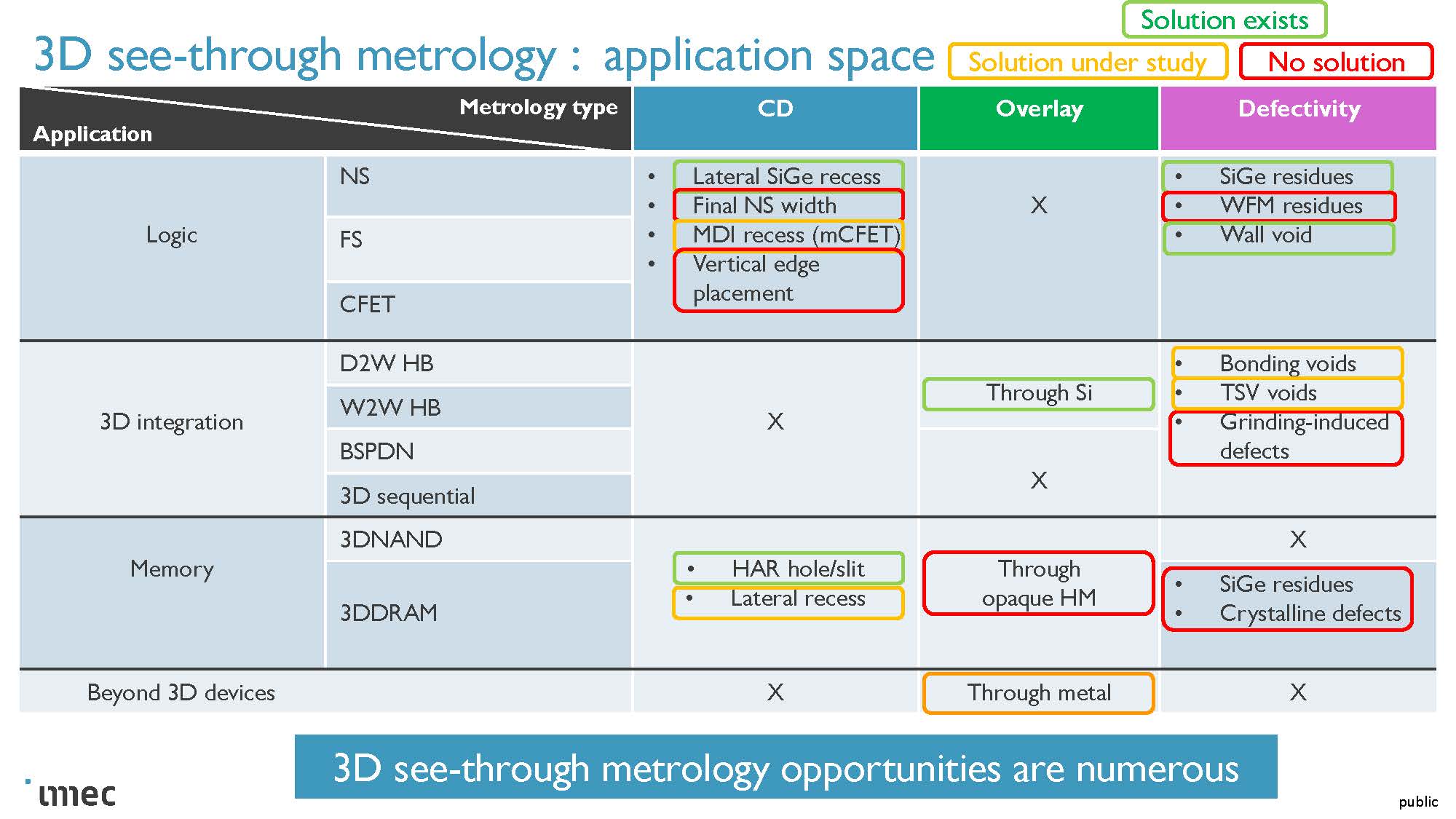

In 「3D時代の半導体計測学」 J. Bogdanowicz らは、3D 構造における計測学の課題を調査しています。

3D 時代では、Z 方向が新しい X/Y スケーリングになりました。 ロジック デバイスの場合、CFET とセミダマシンが課題となり、メモリでは 3D DRAM が将来の課題となり、システム テクノロジ相互最適化 (STCO) のための 3D 相互接続が別の課題となります。

水平ナノシートおよび CFET プロセスの場合、横方向の凹部と充填の特性評価、および多層スタック内の残留物やその他の欠陥の検出が重要になります。 3D メモリでは、高アスペクト比 (HAR) ホール/スプリット プロファイリングや、多層膜内の埋め込み欠陥や残留物を検出するロジックと同様の処理が重要になります。 STCO アプリケーションの場合、接合界面と位置合わせの完全性が鍵となります。

従来の表面計測では感度と速度の間にはすでにトレードオフが存在しますが、現在では検査深度と横方向解像度が重要なトレードオフとなっています。 図 5 は、さまざまな計測技術のプロービング深さと横方向分解能およびスループットを示しています。

図 6 は、さまざまなニーズに対応するための 3D 計測の現在の準備状況をまとめたものです。

図 6 からわかるように、包括的な計測プログラムを達成するには、克服すべき課題がまだ多くあります。

まとめ

高NA EUVの時代が近づいています。 ペリクル、フォトレジスト、計測技術では良好な進歩が見られ、imec はさらなる進歩に向けて XNUMX つの分野すべてで取り組み続けています。

また読む:

TSMC は、あなたが思っているよりも多くのお金を 300mm に費やしてきました

SPIE Advanced Lithography Conference 2023 – AMAT Sculpta® 発表

IEDM 2023 – 2D マテリアル – インテルと TSMC

この投稿を共有する:

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/lithography/329278-spie-2023-imec-preparing-for-high-na-euv/

- :持っている

- :は

- :not

- :どこ

- $UP

- 000

- 1

- 2022

- 2023

- 2D

- 2Dマテリアル

- 30

- 3d

- a

- 達成する

- 実際の

- NEW

- 住所

- 高度な

- 高度なリソグラフィ

- AL

- すべて

- 既に

- また

- 増幅した

- an

- および

- 別の

- 接近する

- 約

- です

- AREA

- エリア

- 周りに

- AS

- 側面

- アセンブリ

- At

- 試みた

- 注意

- 著者

- ベーキング

- ベース

- BE

- ビーム

- になる

- き

- さ

- 以下

- の間に

- ブロック

- 青

- ブレーク

- 休憩

- BRIDGE

- ブリッジ

- 焼く

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- by

- 缶

- キャプチャー

- 自動車

- カーボン

- CD

- 挑戦する

- 課題

- 挑戦

- 変更

- CO

- 崩壊

- 結合

- 互換性のあります

- 包括的な

- 終了する

- 条件

- 講演

- 接触

- 汚染物質

- 続ける

- コントラスト

- 相関

- ここから

- 作成します。

- 重大な

- 電流プローブ

- 曲線

- 減少

- 実証

- 密度

- 寄託

- 深さ

- 記載された

- 設計

- 開発

- Devices

- 死

- 次元

- 方向

- 議論する

- 転位

- すること

- ダウン

- ドライブ

- ドリブン

- 原因

- e

- E&T

- エコシステム

- 効果

- enable

- 可能

- エネルギー

- 強化

- 十分な

- 時代

- エラー

- 評価

- 評価します

- 評価

- さらに

- 最終的に

- 展示

- 予想される

- 探る

- 調査済み

- 暴露

- スピーディー

- 2月

- フィールド

- フィギュア

- 埋める

- 膜

- フォーカス

- 強

- 処方

- 発見

- から

- さらに

- 未来

- 受け

- 良い

- グリーン

- 持っていました

- ハード

- 持ってる

- he

- ヒーロー

- ハイ

- より高い

- 水平な

- 認定条件

- How To

- しかしながら

- HTTPS

- 水素化

- i

- 特定され

- 説明する

- イマージョン

- 改善されました

- 改善

- 向上させる

- in

- 増加した

- 増加

- 示された

- インフラ関連事業

- 当初

- 整合性

- インテル

- 相互接続

- インターフェース

- インタビュー

- 紹介します

- 調べる

- 問題

- 問題

- IT

- JPG

- キー

- ラム

- 風景

- 大

- 層

- 層

- つながる

- 主要な

- レベル

- ような

- LINE

- リスト

- ローカル

- ロジック

- 長い

- 長い時間

- 見て

- 探して

- LOOKS

- 損失

- たくさん

- ロー

- 製

- 作成

- 管理します

- 製造業

- 多くの

- mask

- マスク

- マッチ

- 材料

- 最大幅

- 五月..

- だけど

- 測定結果

- 機械的な

- メモリ

- メッセージ

- 金属

- 計量

- 顕微鏡

- 軽減する

- お金

- 他には?

- ずっと

- マルチ

- 必要

- 必要とされる

- ニーズ

- 新作

- いいえ

- ノイズ

- 今

- 得

- of

- オフ

- オンライン

- on

- ONE

- の

- 機会

- 最適化

- or

- オーガニック

- その他

- でる

- が

- 克服する

- 論文

- パターン

- パターン

- パフォーマンス

- 視点

- ピッチ

- プラズマ

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- さらに

- 貧しいです

- ポスト

- 準備中

- プレゼンテーション

- PLM platform.

- プレゼント

- 社長

- 主要な

- 問題

- プロセス

- ラボレーション

- 処理

- プロファイリング

- 演奏曲目

- 進捗

- 有望

- 実績のある

- 提供します

- 放射線

- レート

- 価格表

- 比

- 読む

- 準備

- 最近

- 最近

- 減らします

- 電話代などの費用を削減

- 軽減

- 削減

- 関連する

- 残った

- 必要

- 解像度

- 結果として

- 結果

- レビュー

- ロードマップ

- 堅牢な

- 前記

- 同じ

- スケーリング

- ショーン

- 見て

- 選択

- 自己

- SEM

- セミ

- 敏感な

- 感度

- シフト

- 示されました

- 示す

- 側

- シグナル

- 同様の

- サイズ

- スロープ

- 遅く

- より小さい

- So

- 一部

- ソース

- スペース

- スピード

- 費やした

- Spot

- 安定性

- 安定させる

- 安定した

- スタック

- スティーブ

- まだ

- 力

- 強く

- 勉強

- テーマ

- そのような

- 十分な

- 優れた

- 表面

- サスペンド

- 甘い

- システム

- トーク

- テクニック

- テクノロジー

- より

- それ

- ブロック

- アプリ環境に合わせて

- その後

- そこ。

- ボーマン

- 彼ら

- もの

- この

- 今年

- それらの

- 三

- スループット

- 時間

- 〜へ

- 一緒に

- あまりに

- ツール

- 豊富なツール群

- に向かって

- 追跡する

- 牽引力

- トレード

- 伝統的な

- 2

- type

- 究極の

- 下

- まで

- 利用された

- 活用

- さまざまな

- 対

- 垂直

- 非常に

- 、

- 実行可能な

- 副会長

- ました

- WELL

- went

- この試験は

- while

- 意志

- ウィンドウズ

- 仕事

- 書きます

- 書き込み

- 年

- 貴社

- ゼファーネット