S2C は、XNUMX 年近くにわたって FPGA プロトタイピングの世界的リーダーであり、その FPGA プロトタイピング プラットフォームは、ザイリンクスとインテルの両方の最新の FPGA を含む、最新の FPGA の入手可能性を綿密に追跡してきました。 そして彼らは、ハイパースケール デザイン プロトタイピングのためのプロトタイピング ソリューションを進化させるという約束を確実に果たしています。 スケールアップする 数十億ゲートの設計をサポートするプロトタイピング プラットフォームの容量と機能。

4 年第 2020 四半期初めにさかのぼると、S2C は、シングル、デュアル、およびクワッド FPGA プロトタイピング プラットフォームを提供する当時の新しいザイリンクス VU19P UltraScale+ FPGA のサポートを発表しました。 その後、2020 年 2 月、S8C は、Logic Matrix あたり 8 個の FPGA、64 つのサーバー ラック (440 個の FPGA) あたり XNUMX 個の Logic Matrix、および複数のサーバーラックをまとめて。 Logic Matrix の最初のイテレーションは、Xilinx VUXNUMX FPGA (と呼ばれる) で提供されました。 LX1)VU19Pバージョン(と呼ばれる)を待ちきれなかった初期の顧客に LX2).

現在、S2C は Logic Matrix ゲームを強化しています。 LX2、VU60 バージョンよりも 440% オーバーのプロトタイピング可能なゲート容量をジャンプします! FPGA ごとに使用可能なゲートが増えるということは、FPGA の数が減り、FPGA インターコネクトが減り、同じプロトタイプのデザインのパフォーマンスが向上することを意味します。 推定ゲート容量は 392 億 XNUMX 万ゲート/ LX2、完全に実装された標準サーバー ラックに 8 台 LX2の 推定 3 億を超える ASIC ゲートのプロトタイピング能力が可能です!

図 1: Prodigy Logic Matrix LX2

| Prodigy Logic Matrixファミリー | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| 推定 ASIC ゲート (M) | 240 | 392 |

| FPGA の数 | 8 | 8 |

| システム ロジック セル (K) | 44,328 | 71,504 |

| FPGA メモリ (Mb) | 709 | 1,327.2 |

| DSP スライス | 23,040 | 30,720 |

| 外部ユーザー I/O | 9,216 | 10,368 |

| SerDes トランシーバー | 384GTH | 640GTY |

| プロディジー コネクタ | 64 | 72 |

| PGT コネクタ | 8 | 0 |

| トランシーバー コネクター | それぞれ 80 GTH + 4 IO を備えた 8 MSAS | 160 GTY + 4 IO でそれぞれ 8 MCIO |

| SerDes パフォーマンス | 16 Gbps | 28 Gbps |

フィギュア 2: ロジックマトリックスファミリー

柔軟で高速な相互接続は、高密度 FPGA プロトタイピングの鍵であり、Logic Matrix は階層的な 3 レベルの相互接続戦略をサポートしています。 ショートブリッジ 隣接する FPGA 間の相互接続用。 シスリンク 高帯域幅 FPGA ケーブル相互接続用、および トランスリンク MCIO ケーブルを介した長距離 FPGA SerDes 相互接続用。 FPGA インターコネクトを簡素化し、FPGA の価値を最大化する トランスリンクS2C のパーティショニング フローは、ザイリンクスが新たに導入した高速トランシーバー ピン多重化 (HSTPM) をサポートし、サイクル精度の高い信号転送、ピン多重化、および低レイテンシの SerDes FPGA 接続を簡素化します。

プロトタイピングまでの時間を最小限に抑え、プロトタイピングの生産性を最大化するために、S2C の他のプロトタイピング生産性ツールは、Logic Matrix を念頭に置いて設計されています。 Player Pro ランタイム ソフトウェア – アドオン S2C プロトタイピング ツール プロトブリッジ, MDMプロ、および S2C の プロトタイプレディIP.

Player Pro ランタイム ソフトウェアが付属 LX2、高度なクロック管理、統合されたセルフテスト、自動ボード検出、I/O 電圧プログラミング、複数の FPGA ダウンロード、およびリモート システムの監視と管理などの便利な機能を提供します。 また、組み込みの AXI-over-Ethernet デバッグ ツールである AXEVision も含まれており、AXI 関連のデザインのリモート デバッグを簡素化します。

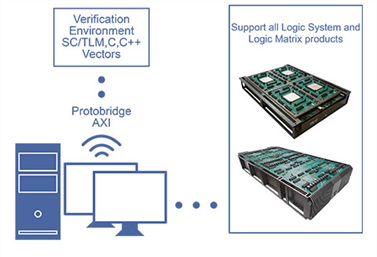

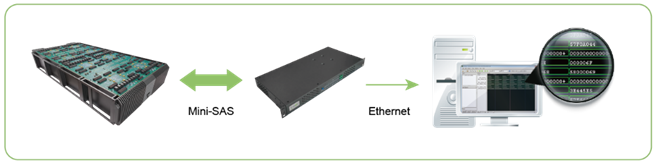

プロトブリッジ ホスト PC と LX2 – 大量のソフトウェア モデル トランザクション、ビデオ ストリーム、またはシステム検証用のその他のテスト スティミュラスの転送を可能にします。

図 3: プロトブリッジ

MDMプロ 最大 64 つの FPGA のクロス トリガーによる詳細なトレース デバッグ、単一の表示ウィンドウからのマルチ FPGA 信号トレースの表示、125GB の外部トレース波形ストレージ、最大 XNUMXMHz のトレース サンプリング レート、および複雑なトレース キャプチャ用のトリガー ステート マシン言語のサポートを備えています。要件。

図 4: MDM プロ

S2C's は、次の豊富なライブラリも提供しています。 プロトタイプレディIP LX2 – プラグ アンド プレイ ドーター カード – FPGA プロトタイプを中心としたプロトタイピング環境の作成を高速化します。

図 5: プロトタイプ対応の IP ドーター カード

プロディジー ロジック マトリックス LX2 が利用可能になりました。 詳細については、最寄りの S2C 営業担当者にお問い合わせいただくか、次の Web サイトをご覧ください。 www.s2ceda.com.

この投稿を共有する: ソース: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- アドオン

- 発表の

- お知らせ

- 周りに

- ASIC

- 賃貸条件の詳細・契約費用のお見積り等について

- 10億

- ボード

- ケーブル

- 容量

- 接続

- 接続性

- Customers

- データ

- 配信する

- 設計

- 検出

- 距離

- 早い

- 環境

- 家族

- 特徴

- イチジク

- 名

- フロー

- FPGA

- ゲーム

- ゲイツ

- グローバル

- HTTPS

- 含めて

- 情報

- インテル

- IP

- キー

- ESL, ビジネスESL <br> 中国語/フランス語、その他

- 大

- 最新の

- 図書館

- ローカル

- 管理

- マトリックス

- 百万

- モニタリング

- 提供すること

- オファー

- その他

- PC

- パフォーマンス

- プラットフォーム

- プラットフォーム

- Pro

- 生産性

- 生産性向上ツール

- プログラミング

- プロトタイピング

- 価格表

- 要件

- セールス

- 拡大する

- ソフトウェア

- ソリューション

- 都道府県

- 刺激

- ストレージ利用料

- 戦略

- ストリーム

- サポート

- サポート

- test

- 取引

- 値

- ビデオ

- wait

- 誰