「超効率コンピューティングのための FDSOI を使用したダイナミック ロジックの非伝統的設計」というタイトルの新しい技術論文が、ドイツ研究財団の資金提供を受けて、シュトゥットガルト大学、カリフォルニア大学バークレー校、インド工科大学カンプール校、およびミュンヘン工科大学の研究者によって出版されました。 。

抽象

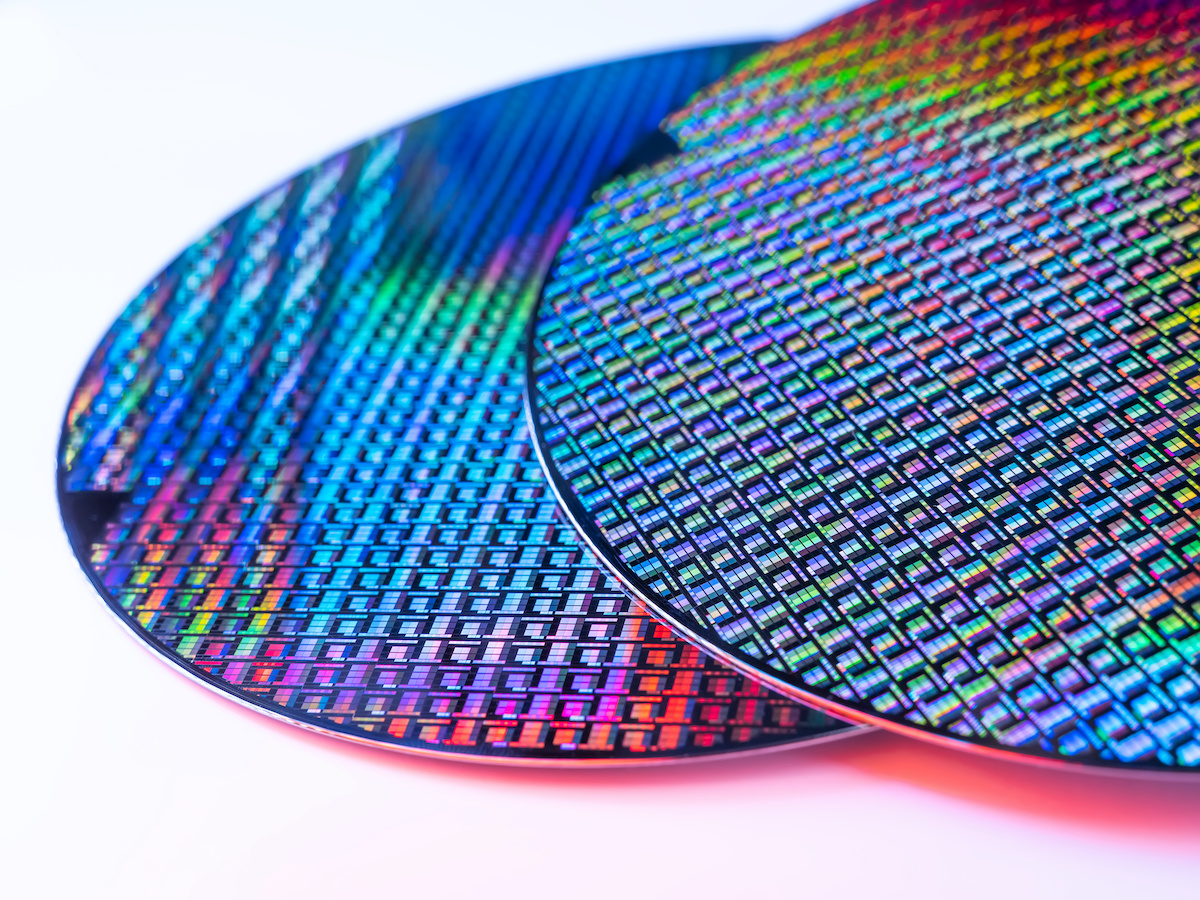

「この論文では、完全空乏型シリコン・オン・インシュレータ (FDSOI) FET を使用したダイナミック論理回路の非伝統的な設計を提案します。 FDSOI FET は、しきい値電圧 (Vt )バックゲートバイアスを使用して調整可能(つまり、低Vt状態と高Vt状態)。 私たちの設計は、FDSOI FET のフロント ゲートとバック ゲートを入力端子として利用し、ダイナミック ロジック ゲート (NAND、NOR、AND、OR、XOR、XNOR など) と回路 (半加算器や全加算器など) を提案します。 従来のダイナミック ロジック設計と比較して、ダイナミック ロジック ゲートの構築に必要なトランジスタの数が少なく、低消費電力で高性能を実現します。 FDSOI FET のコンパクトな産業用モデル (BSIM-IMG) は、ダイナミック ロジック ゲートのシミュレーションに使用されており、14nm FDSOI FET テクノロジ ノード データを再現するために完全にキャリブレーションされています。 キャリブレーションは、電気的特性とプロセス変動の両方に対して実行されます。 シミュレーション結果は、従来の設計と比較して、トランジスタ数、伝播遅延、電力、電力遅延積がそれぞれ 23.43%、57.16%、47.05%、77.29% という平均改善を示しています。 さらに、当社の設計は、ダイナミック論理ゲートの駆動能力に影響を与える電荷共有効果を低減します。 さらに、プロセス、電源電圧、負荷容量の変動がダイナミック ロジック ファミリの伝播遅延に及ぼす影響を詳細に分析しました。 結果は、これらの変動が、従来のダイナミック論理ゲートと比較して、提案されたFDSOIベースのダイナミック論理ゲートの伝播遅延にわずかな影響を与えることを示しています。」

見つける テクニカルペーパーはこちら。 2023年XNUMX月公開。

S. Kumar、S. Chatterjee、CK Dabhi、YS Chauhan、および H. Amrouch、「超効率コンピューティングのための FDSOI を使用したダイナミック ロジックの非伝統的設計」、探索的ソリッドステート計算デバイスおよび回路に関する IEEE ジャーナル、doi: 10.1109/JXCDC.2023.3269141。 オープンアクセスs.

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- :持っている

- :は

- 10

- 2023

- 23

- 77

- a

- 達成する

- 添加

- 調節可能

- ことができます

- an

- &

- 4月

- AS

- At

- 平均

- バック

- BE

- き

- バークリー

- バイアス

- 両言語で

- ビルド

- by

- 特性

- チャージ

- 比べ

- コンピューティング

- 従来の

- データ

- 遅らせる

- 設計

- デザイン

- 詳細

- Devices

- ダイナミック

- e

- 効果

- 家族

- FET

- より少ない

- Foundation

- フロント

- フル

- 完全に

- 資金調達

- さらに

- ゲイツ

- ドイツ語

- 半分

- 持ってる

- ハイ

- HTTPS

- i

- IEEE

- 影響

- 改善

- in

- インディアン

- インダストリアル

- 機関

- IT

- ジャーナル

- ような

- 負荷

- ロジック

- ロー

- マイナー

- ミュンヘン

- 新作

- of

- on

- or

- 私たちの

- 紙素材

- パフォーマンス

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- 電力

- プロセス

- プロダクト

- 提案する

- 提案された

- 提案する

- 公表

- 軽減

- 必要

- 研究

- 研究者

- それぞれ

- 結果

- s

- シェアリング

- 表示する

- シリコン

- 米国

- 供給

- 技術的

- テクノロジー

- それ

- ボーマン

- この

- しきい値

- タイトル

- 〜へ

- 大学

- 中古

- 利用

- 電圧

- ました

- we

- which

- ゼファーネット