Chiplets are beginning to impact chip design, even though they are not yet mainstream and no commercial marketplace exists for this kind of hardened IP.

There are ongoing discussions about silicon lifecycle management, the best way to characterize and connect these devices, and how to deal with such issues as uneven aging and thermal mismatch. In addition, a big effort is underway to improve observability of チップレット over time, something that is particularly important as these devices are used in safety-critical and mission-critical applications.

All of these issues need to be solved to enable widespread adoption, and the chip industry has recognized that the slowing of Moore’s Law combined with fixed reticle sizes will require changes in how chips are designed, manufactured, and packaged. It’s physically impossible to fit all the functions required for many applications into a single SoC, and the goal now is for an orderly, predictable, and repeatable approach to disaggregating many of these components. In theory, this will allow devices to be more easily customized, speed time to market, and avoid expensive scaling of components that don’t require it, such as analog functions.

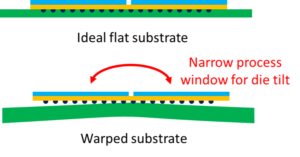

Achieving that goal will require solving some complex and thorny issues, however. For one thing, it will require much better observability, monitoring, and analysis of what goes into a package. While the concept of putting multiple chips into a package dates back to the 1990s with マルチチップモジュール, with chiplets the dies typically are smaller and thinner, and the dynamics of how to characterize, test, and observe them have changed significantly.

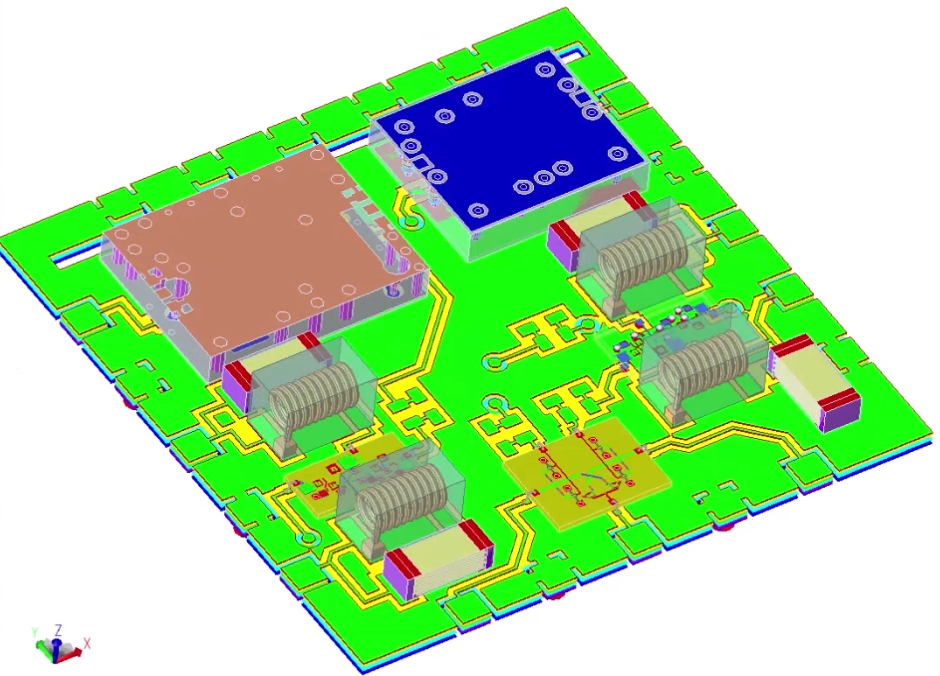

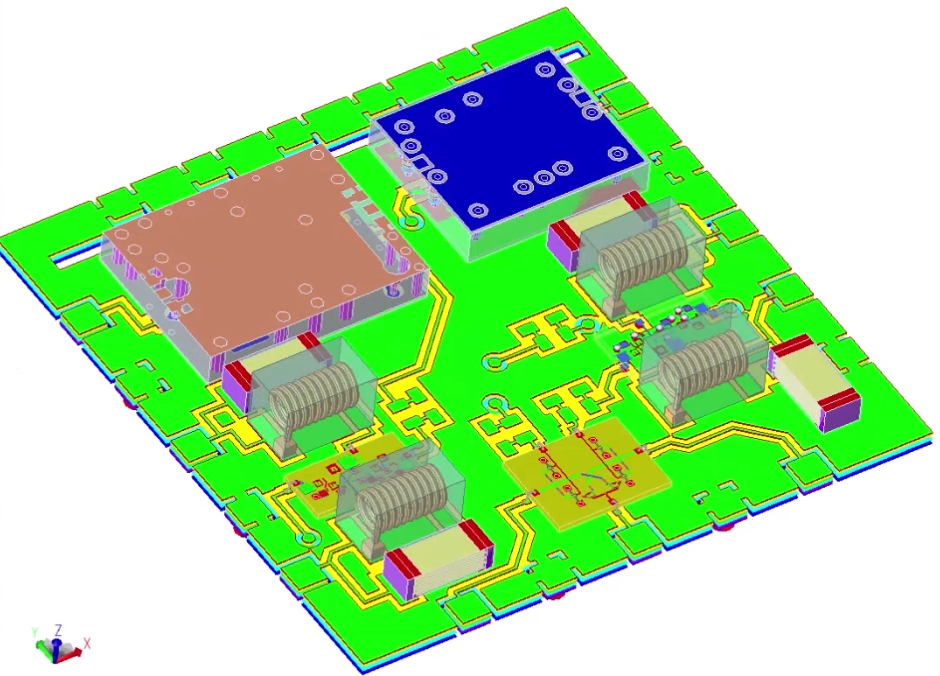

“Historically we have called these multi-chip modules, which are very popular in the wireless world today,” said Nilesh Kamdar, RF/microwave portfolio lead at キーサイト. “You pick up any smartphone, and the wireless piece of the smartphone is a front-end module that’s 20 to 30 chips squeezed together on a small space that’s smaller than a fingernail. That has been happening in the industry for at least a decade, if not longer. Also, several aerospace, and other high-frequency problems have required this kind of integration, so we’ve done this in the past.”

Fig. 1. Multi-chip RF module layout shown in Keysight’s PathWave ADS. Source: Keysight

The big shift now underway involves a much broader application for this approach, as well as improvements in the chiplet design, and standard ways to connect, test, and measure what’s happening inside the chiplets themselves, as well as the advanced package that surrounds them.

“Automotive is a great example of what’s changing,” Kamdar said. “At a recent conference, a vice president from a major OEM spoke about not being able take a data center and put it in the backseat of a car, because that’s what it takes to have an autonomous vehicle today. If you do more integration — and if you somehow make the board disappear, and everything is squeezed together — maybe vertically we can squeeze that into the backseat of a car. There are many similar use cases. The power need for chiplets might be lower if you consider physical data centers. There are a lot of benefits, and that’s what’s driving chiplets today.”

However, these changes are deceptively complex, and the industry may need to go back to school on this. “Building chiplets at scale is such a different model that we all need to reassess our skills,” he said. “We need to reassess how organizations are set up and how architecture happens. We need to reassess the role of a system designer. They may have been looking at things in a different way, and they may have been saying, ‘I’m a system designer. I design the spec for the systems. I break it down into smaller level components, individual ICs, and distribute the specs. I walk away and come back six months later and see how everyone did.’ Maybe that’s not even possible. Maybe there are multiple system designers that need to exist up and down the chain. Those are the kinds of conversations that need to happen. Within the biggest players in the industries, those conversations are happening already, but not everywhere.”

The number of potential interactions in the context of a multi-chiplet design is significant, and in many cases, design-specific. “If you believe in multi-die, if you believe in chiplets, you’ve got to believe it will only exacerbate the whole [design and integration] problem,” said Shekhar Kapoor, senior director of product line management for the シノプシス EDA グループ. “Chiplets are going to come from many places, many sources. There are going to be a lot of choices, a lot of options for everyone. The biggest issue is the current usages around all this. Large companies are doing this in a bespoke and customized fashion. But if you go broad go with standardization, how do you know a chiplet coming in is going to fit into the environment, in the product that you are trying to build?”

Despite a focus on standards such as UCIe and Bunch of Wires, there are still the nuances in terms of how the individual chiplets are characterized in the context of a system. “How do you really know the profile of it? That’s where even more monitoring will come into the picture, which is almost like a signature,” Kapoor said. “You can read it and know if it is ideal for your environment. Given that the industry is moving toward more chiplet enablement, this will be a core consideration. More requirements will emerge, more standards will emerge, so then you can see whether something is going to be a fit or not.”

There are other challenges to overcome, as well.

“With chiplets, all the high-speed signals are within the package, so observability is much more challenging,” said Sue Hung Fung, product line marketing manager for UCIe at ケイデンス. “This can be done through link error checks, eye scans, BiST, etc., in order to get to a known good die (KGD). Test methods are all built around this. In addition, having good monitors for the health of the link would be valuable, and there are new and different proposals from different vendors.”

The key is to monitor signal quality in the context of the rest of the components in a package, which becomes more difficult as more functions are disaggregated into chiplets.

“Can we monitor the signals and quality of these during data transfer? Training techniques are done prior to mission mode to improve data transfer robustness,” Hung Fung noted. “Retraining is not desired as it can cause data interrupt. We need to be able to continuously monitor and report each lane and detect any events that may cause failure before a failure occurs. Prevention of system failure and repair of those failures includes redundant lane remapping or other repair methods to detect marginally failing lanes. Training and continuous monitoring of these internal chiplet signals are the challenges for analyzing the link behavior.”

Working groups for UCIe are looking to standardize some of this observability in order to have an open link ecosystem. But adding observability and monitoring also can vary greatly by vertical segment.

Randy Fish, director of product line management for the Synopsys EDA Group, explained that because there’s been no standard approach and few commercial suppliers for observability solutions, almost all the solutions have been bespoke. “If you go into any of the leading semis, they do something,” he said. “The question is, are there functions around multi-die that will force us to standardize to have a cohesive or coherent infrastructure for monitoring and debug — basically to see what is going on especially if you’re getting multiple die from multiple suppliers. Some of the multi-die solutions are going into automotive, and there they do care about things like aging and what is happening to these die. And as we know, it’s advanced nodes. It’s not like you have 6 die of mature 10-year-old technologies. These are advanced nodes that don’t have a long history. For that reason, there are a number of factors forcing this to happen.”

Chiplets also introduce some interesting contrasts. Keysight’s Kamdar noted that during a recent CEO panel, one of the panelists said chiplets have a unique dichotomy. “On the one hand, each chiplet could be an independent IP that you can procure from an IP vendor and integrate it into your system for relatively low cost, relatively easily. However, the entire stack up that you’re trying to build suddenly forces you to know everything. Previously, you could have just said, ‘I need six things. I’m going to buy five off the shelf from an IP vendor and they will figure out what it needs. I’m going to focus on one.’ But now you may not be successful in doing that. You may actually need to know how to do all six, and figure out how all of that happens because the complexity of the problem just went up. This may force the industry to initially only allow the big players to figure this out. It may take a lot longer for the smaller vendors to be able to be successful in this environment.”

Nevertheless, it will take more than one company to accelerate chiplet integration and adoption.

“Keysight attended the TSMC Symposium, which is a more public event, and as a follow-up there was a workshop with just the partners that are part of the 3D Fabric Alliance,” Kamdar said. “TSMC started and ended the whole day by talking about how we all need to work on this together, which was echoed by other participants, including AMD and Qualcomm. Speakers from both companies said not a single EDA company knows how to solve the chiplet problem on their own. The entire industry must work together.”

技術的課題

Another key concern with chiplets is heat dissipation. This is part of the characterization, but it also is highly dependent on use cases, packaging choices, and the overall system-in-package architecture.

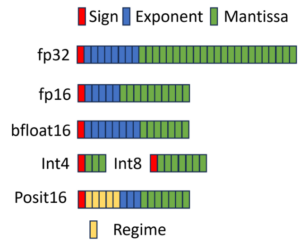

“For chiplets marginality in the design is slim given optimal PPA (targeting aggressive pj/bit and beachfront density), which is crucial when designing chiplet PHYs,” said Rishi Chugh, vice president of product marketing, IP Group at Cadence. “Reliability is key, and so is observability to screen the KGD, as well as get it to commercial operational success. Data integrity schemes like CRC (cyclic redundancy check), eye scan, BiST, and monitoring circuits are implemented in the design for robustness, and the design must be over-provisioned with failure mechanisms to ensure the data line is resilient.”

An entire chapter within the UCIe protocol is dedicated to initialization and training associated with the UCIe protocol, which covers the observability aspect of the protocol, Chugh added.

Additionally, there is debate as to whether the actual fundamentals of adding observability into a system is the hardest part, or whether the change in thinking around these concepts is more difficult.

“It’s actually not that complicated in contrast to other things because it’s ‘just’ another block to be connected to. There’s observation, and we have capabilities to trace things,” said Frank Schirrmeister, vice president solutions and business development at アルテリスIP. “Users are already requesting things like looking at the registers from a software perspective. So now the challenge becomes making those registers available in the NoC. From a NoC perspective, there are the protocols themselves like CHI, ACE, AMBA, OCP or others, and those are the mechanisms of the language — how they talk and how they interact. Within the NoC, with the more complex protocols, there are things happening over multiple cycles, so you need to wait for responses, you put things in the pipeline.”

This is similar to speculative execution in processors. “We talk about these credits, like how long do I have to wait for response and so forth,” Schirrmeister explained. “Those are all parts of the protocols. In the NoC, you need to understand issues like how deep are the buffers? When am I actually waiting for data? It is partly performance. Then, for the observability, you can connect to the data, and the sensors might use their own network depending on how you want to configure it. In the case of on-chip monitors, you need to decide whether to put this on a special observability bus, for example. There’s always a discussion how much debug do I do actually have? At the end of the day, it’s ‘just’ another interconnect of those components and you need to decide how to export it out of the chip, and so forth. How much you store on chip is all a question of how much silicon real estate am I willing to spend for that?”

That becomes particularly important when stitching together chiplets. “How do I ensure I’ve got enough space for this computational entity that’s just looking like data, which isn’t actually adding any value to the immediate function?” asks Gajinder Panesar, chief architect at Picocom. “Also, I may not be a monitoring expert, but I know I need it. So I need something that says, ‘Just press that button.’ You have an environment, we are doing the designing, and ‘this’ happens. Ideally, we should be observing the behavior of CPU performance and then dynamically tuning certain aspects of the core to get better performance.”

One of the pieces that has yet to be developed is dynamic control of the devices, and the adjustments that can be made over its lifetime.

“Say we have all the ability to model everything up front,” said Lee Harrison, director of product marketing in the Tessent group at Siemens Digital Industries Software. “We’ve got all of the monitors built in to do the in-system side of things, but it’s closing that loop. For the newer geometries, there’s still quite a bit of learning to be done to really optimize how we can tweak the various parameters of the device to extend that reliability. The piece that closes that loop to in-life system is where there’s a huge amount of value. Yet there is still work to be done.

Changing responsibility roles

Commercial chiplets add another thorny issue, which is who’s responsible when something unexpected is observed or goes wrong.

“If I’m a chipmaker, I make the chip and I may go through an OSAT for testing,” said Paul Karazuba, vice president of marketing at エクスペデラ. “I may use ASE as a packaging house, but I’m selling it with my name and my warranty. It’s going to get interesting when we have chiplets. In all of our meetings concerning chiplets, the question is always raised about who is going to be responsible for what. Let’s say I was to make an AI chiplet and I sell into a system and package with six other companies’ chiplets. Which company is going to be the warranty? Which company will do the service on it? There is no real consensus right now.”

The working idea is the company whose name is on the outside of the package will be responsible, Karazuba said. “That company is probably going to be the one that has an end responsibility for the service to its customers, but it brings in another layer of service that chiplet makers need to provide, and that’s going to be interesting. The fear is that circa 2000, Intel-Microsoft-Dell triangle of everyone pointing fingers at each other. That’s an unspoken fear in the industry right now.”

And maybe it’s not one of the chiplets. What happens if a substrate or a physical interconnect is defective?

“From a testing point of view, a chiplet may test perfectly well,” Karazuba said. “But when there’s a physical interconnect problem, how does the chiplet maker understand that versus the multichip module maker? It’s going to be interesting. The only way to solve these issues is going to be trial and error. We can design as many legal contracts as we want to as semiconductor makers, but we’re in uncharted waters here and things are going to have to be adjusted. Support models are going to have to be adjusted to reflect the new reality of monolithic silicon not being a primary vehicle of the semiconductor sale.”

Synopsys’ Kapoor already has seen reflections in the ecosystem. “There always have been ecosystems, but your active ecosystem from wherever you are was maybe the next circle around it. If you are doing design, you’d only be concerned about the foundry design rules and design rule manual. That’s changing when you talk about the chiplets. Even with the design, now you’re thinking about test even more than you ever did before. You’re talking to アドバンテスト および テラダイン. Even though you’re just a designer, you have to figure out what you need to put in from an ATPG point of view and how it’s going to be tested. The relevant ecosystem size is increasing.”

Still, the industry has no choice but to solve these issues. “We’ve talked about the chiplet marketplace. You’ll be able to pull a die out and have it ready. We’re still far away from that, but the steps are becoming clearer about what we need to achieve. Connectivity is fundamental. UCIe standards are a must, and with that comes the protocols and the rules from a connectivity point of view that you have to establish. Next would be very clearly defined models. The challenges we’re talking about are impacted by thermals, in particular, and power. Some standards already exist around that, and we will go from connectivity to the characterized model, so we can more reliably use that. Then we’ll need some sort of signature, which is where we can see from a testability point of view the lifespan and how all die are going to be changing differently.”

The inputs into all of this will come from chip and system monitors, which will also need to be based on standards.

- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- プラトアイストリーム。 Web3 データ インテリジェンス。 知識増幅。 こちらからアクセスしてください。

- 未来を鋳造する w エイドリエン・アシュリー。 こちらからアクセスしてください。

- PREIPO® を使用して PRE-IPO 企業の株式を売買します。 こちらからアクセスしてください。

- 情報源: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- :持っている

- :は

- :not

- :どこ

- $UP

- 1

- 20

- 30

- 3d

- a

- 能力

- できる

- 私たちについて

- 加速する

- 達成する

- アクティブ

- 実際の

- 実際に

- 加えます

- 追加されました

- 追加

- 添加

- 調整

- 調整

- 養子縁組

- 広告

- 高度な

- 航空宇宙

- 積極的な

- 高齢化

- AI

- すべて

- アライアンス

- 許す

- 既に

- また

- 常に

- am

- AMD

- 量

- an

- 分析

- 分析する

- および

- 別の

- どれか

- 申し込み

- アプローチ

- 建築

- です

- 周りに

- AS

- 側面

- 側面

- 関連する

- At

- 自動車

- 自律的

- 自律車両

- 利用できます

- 避ける

- 離れて

- バック

- ベース

- 基本的に

- BE

- なぜなら

- になる

- になる

- き

- 開始

- さ

- 信じる

- 利点

- BEST

- より良いです

- ビッグ

- 最大の

- ビット

- ブロック

- ボード

- 両言語で

- ブレーク

- もたらす

- 広い

- より広い

- ビルド

- 内蔵

- 束

- バス

- ビジネス

- 事業開発

- 焙煎が極度に未発達や過発達のコーヒーにて、クロロゲン酸の味わいへの影響は強くなり、金属を思わせる味わいと乾いたマウスフィールを感じさせます。

- (Comma Separated Values) ボタンをクリックして、各々のジョブ実行の詳細(開始/停止時間、変数値など)のCSVファイルをダウンロードします。

- 購入

- by

- ケイデンス

- 呼ばれます

- 缶

- 機能

- 自動車

- これ

- 場合

- 例

- 原因となる

- センター

- センター

- 最高経営責任者(CEO)

- 一定

- チェーン

- 挑戦する

- 課題

- 挑戦

- 変化する

- 変更

- 変更

- 変化

- 章

- 特徴づけます

- 特徴付けられた

- チェック

- 小切手

- チーフ

- チップ

- チップ

- 選択

- 選択肢

- サークル

- より明確に

- はっきりと

- 閉じ

- 閉鎖

- コヒーレント

- 凝集

- 組み合わせた

- 来ます

- 来ます

- 到来

- コマーシャル

- 企業

- 会社

- 複雑な

- 複雑さ

- 複雑な

- コンポーネント

- コンセプト

- コンセプト

- 懸念

- 心配

- 講演

- お問合せ

- 交流

- 接続性

- コンセンサス

- 検討

- 考慮

- コンテキスト

- 連続的な

- 連続的に

- 契約

- コントラスト

- コントラスト

- コントロール

- 会話

- 基本

- 費用

- 可能性

- カバー

- CPU

- CRC

- Applied Deposits

- 重大な

- 電流プローブ

- Customers

- カスタマイズ

- サイクル

- データ

- データセンター

- データセンター

- 試合日

- 中

- 取引

- 議論

- 十年

- 決めます

- 専用の

- 深いです

- 定義済みの

- 密度

- 依存

- によっては

- 設計

- 設計

- デザイナー

- デザイナー

- 設計

- 希望

- 発展した

- 開発

- デバイス

- Devices

- DID

- 死

- 異なります

- 難しい

- デジタル

- 取締役

- 姿を消す

- 議論

- 議論

- 分配します

- do

- ありません

- すること

- 行われ

- ドント

- ダウン

- 運転

- 間に

- ダイナミック

- 動的に

- ダイナミクス

- 各

- 簡単に

- エコシステム

- 生態系

- 努力

- 出てくる

- enable

- 有効化

- end

- 十分な

- 確保

- 全体

- エンティティ

- 環境

- エラー

- 特に

- 確立する

- 不動産

- 等

- さらに

- イベント

- イベント

- EVER

- 誰も

- すべてのもの

- 例

- 実行

- 存在する

- 存在

- 高価な

- エキスパート

- 説明

- export

- 伸ばす

- 目

- ファブリック

- 要因

- 失敗

- 不良解析

- 遠く

- ファッション

- 恐怖

- 少数の

- イチジク

- フィギュア

- 魚

- フィット

- 固定の

- フォーカス

- 強

- 軍隊

- 前進

- ファウンドリ

- から

- フロント

- function

- 機能

- 基本的な

- 基礎

- ギア

- 取得する

- 受け

- 与えられた

- Go

- 目標

- ゴエス

- 行く

- 良い

- 素晴らしい

- 大いに

- グループ

- グループの

- ハンド

- 起こる

- 出来事

- 起こります

- 持ってる

- 持って

- he

- 健康

- こちら

- ハイ

- 高周波

- 非常に

- history

- お家の掃除

- 認定条件

- How To

- しかしながら

- HTTPS

- 巨大な

- i

- ICS

- アイデア

- 理想

- if

- 即時の

- 影響

- 影響を受けた

- 実装

- 重要

- 不可能

- 改善します

- 改善

- in

- 含ま

- 含めて

- の増加

- 独立しました

- 個人

- 産業

- 産業を変えます

- インフラ

- 当初

- 入力

- 統合する

- 統合

- 整合性

- 対話

- 相互作用

- 興味深い

- 内部

- に

- 紹介する

- IP

- 問題

- 問題

- IT

- ITS

- ただ

- カプール

- キー

- キック

- 種類

- 知っている

- 既知の

- レーン

- 言語

- 大

- 後で

- 法律

- 層

- レイアウト

- つながる

- 主要な

- 学習

- 最低

- リー

- リーガルポリシー

- レベル

- wifecycwe

- 寿命

- 一生

- ような

- LINE

- LINK

- 長い

- より長いです

- 探して

- たくさん

- ロー

- 製

- 主流

- 主要な

- make

- メーカー

- メーカー

- 作成

- 管理

- マネージャー

- マニュアル

- 製造された

- 多くの

- 市場

- マーケティング

- 市場

- 成熟した

- 最大幅

- 五月..

- だけど

- メカニズム

- ミーティング

- メソッド

- かもしれない

- ミッション

- モード

- モデル

- モジュール

- モジュール

- モニター

- モニタリング

- モニター

- 一枚岩

- ヶ月

- 他には?

- 移動する

- ずっと

- の試合に

- しなければなりません

- my

- 名

- 必要

- ニーズ

- ネットワーク

- 新作

- 次の

- いいえ

- ノード

- 注意

- 今

- 数

- 観察する

- of

- オフ

- on

- ONE

- 継続

- の

- 開いた

- オペレーショナル

- 最適な

- 最適化

- オプション

- or

- 注文

- 組織

- その他

- その他の参加者

- その他

- 私たちの

- でる

- 外側

- が

- 全体

- 克服する

- 自分の

- パッケージ

- パッケージ化された

- 包装

- パネル

- パラメータ

- 部

- 参加者

- 特定の

- 特に

- パートナー

- 部品

- 過去

- Paul Cairns

- パフォーマンス

- 視点

- 物理的な

- 物理的に

- 選ぶ

- 画像

- ピース

- ピース

- パイプライン

- 場所

- 計画

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- プレーヤー

- ポイント

- 視点

- 人気

- ポートフォリオ

- 可能

- 潜在的な

- 電力

- 予測可能な

- 社長

- 防止

- 前に

- 主要な

- 事前の

- 多分

- 問題

- 問題

- プロセッサ

- プロダクト

- プロフィール

- 提案

- プロトコル

- 提供します

- 公共

- 置きます

- パッティング

- クアルコム

- 品質

- 質問

- 隆起した

- 読む

- 準備

- リアル

- 不動産

- 現実

- 本当に

- 理由

- 最近

- 認識

- 反映する

- 感想

- レジスタ

- 相対的に

- 関連した

- 信頼性

- 修理

- 繰り返し可能

- レポート

- 必要とする

- の提出が必要です

- 要件

- 弾力性のあります

- 応答

- 回答

- 責任

- 責任

- REST

- 右

- 丈夫

- 職種

- ルール

- ルール

- 前記

- 塩

- 言う

- 格言

- 言う

- 規模

- スケーリング

- スキャン

- スキーム

- 学校

- 画面

- 見て

- セグメント

- 売る

- 販売

- 半導体

- シニア

- センサー

- サービス

- セッションに

- いくつかの

- 棚

- シフト

- すべき

- 示す

- 側

- シグナル

- 信号

- 重要

- 著しく

- シリコン

- 同様の

- SIX

- 半年

- サイズ

- サイズ

- スキル

- 減速

- 小さい

- より小さい

- スマートフォン

- So

- ソフトウェア

- ソリューション

- 解決する

- 解決

- 一部

- 何か

- ソース

- ソース

- スペース

- スピーカー

- 特別

- スペック

- 投機的な

- スピード

- 過ごす

- 絞る

- スタック

- 標準

- 規格

- 開始

- ステップ

- まだ

- 店舗

- 成功

- 成功した

- そのような

- 訴える

- サプライヤー

- サポート

- シンポジウム

- システム

- 取る

- 取り

- Talk

- 会話

- ターゲット

- テクニック

- テクノロジー

- 条件

- test

- テスト

- より

- それ

- アプリ環境に合わせて

- それら

- 自分自身

- その後

- 理論

- そこ。

- サーマル

- ボーマン

- 彼ら

- もの

- 物事

- 考え

- この

- それらの

- しかし?

- 介して

- 時間

- 〜へ

- 今日

- 一緒に

- に向かって

- トレース

- トレーニング

- 転送

- トライアル

- 試行錯誤

- tsmc

- 一般的に

- わかる

- 進行中の

- 予期しない

- ユニーク

- us

- つかいます

- 中古

- 貴重な

- 値

- さまざまな

- 自動車

- ベンダー

- ベンダー

- 対

- 垂直

- 垂直に

- 非常に

- 副会長

- 詳しく見る

- wait

- 待っています

- 欲しいです

- ました

- ウォーターズ

- 仕方..

- 方法

- we

- WELL

- 行ってきました

- この試験は

- 何ですか

- いつ

- かどうか

- which

- while

- 誰

- 全体

- その

- 広範囲

- 意志

- 喜んで

- 無線

- 以内

- 仕事

- 共に働く

- ワーキング

- ワークショップ

- 世界

- でしょう

- 間違った

- まだ

- 貴社

- あなたの

- ゼファーネット