In integrated circuit terminology, a droop is the voltage drop that happens in a circuit. This is a well-known phenomenon and can happen due to the following reasons. The power supply falls below the operating range for which a chip was designed for, resulting in a droop. More current is drawn by the conductive elements than they were designed for, resulting in a droop. Sometimes, signal interference or noise on the power supply can also cause voltage fluctuations, resulting in a droop.

Droops can impact the operations of a circuit. Reduced performance of the chip, leading to longer processing times is one such impact. But the following are some of the more serious and/or catastrophic impacts. The chip could draw more current to maintain the level of performance leading to increased power consumption and heat dissipation. This can lead to reduced life of the chip and in severe cases, a complete failure of the chip due to setup and hold variations. Droops can also cause data corruption or errors in the output. This is a very serious issue for applications that depend on the accuracy and reliability of the chip.

Naturally, the phenomenon of droops is taken into serious consideration when designing chips and systems. The most common methods to mitigate droops are power supply decoupling, voltage regulation, circuit optimization and system-level power management. The conditions and the operating environment in which the chip will be performing are carefully considered when designing droop mitigating solutions.

Modern Day Problems

As SoCs become more complex, droop issues can get quite complex too. A SoC’s design needs to be optimized for performance, power, cost, form factor, etc. in addition to optimizing for droop mitigation. Sometimes these optimization goals can compete with each other and run counter and tradeoffs have to be made. For example, SoC architects can raise the operating voltage, adding margin, to circumvent local and global droop, but this rise quadratically increases power. Alternatively, designers can have their clock generation adapt to droop, which makes performance a function of clock generation switching time.

Consequently, large SoCs in the datacenter compute and AI space are notably susceptible to droop. Customer workloads are very diverse and dynamic, leading to significant fluctuations in switching activity and current draw. Of course, systems cannot afford to let droop issues go unaddressed. The potential liability from inaccurate output or catastrophic failure of a chip is too high for today’s systems and applications.

Localized Droop Issues

Application-specific accelerators are widely used in tandem with general-purpose processors to deliver the performance and power efficiency required in today’s demanding computing environments. But these accelerators as well as the increasing number of cores and the asymmetric nature of workloads, increase the risk of localized voltage droops. These localized voltage drops are a result of sudden increase in switching activity and can cause transient glitches and potential mission-mode failures.

When localized droop occur, the impact can be mitigated through dynamic frequency scaling. This is achieved by adjusting the timing of a circuit using a programmable clock. A programmable clock allows the clock frequency and timing to be adjusted dynamically based on the current operating conditions of the circuit.

Movellus Makes it Easy to Address Localized Droops

Movellus, a leading digital system-IP provider, has developed the Aeonic Generate family of products to address localized droops. The Movellus Aeonic portfolio offers adaptive clocking solutions that deliver rapid droop response. The portfolio includes the adaptive clocking system. The building blocks are built with synthesizable Verilog, making them intrinsically flexible. The solutions are configurable, scannable and process-portable for a wide range of advanced SoC applications.

The Aeonic Generate family of products is also significantly smaller than traditional analog solutions. As a result, designers can instantiate the IP at the granularity required without any significant impact on the area. Additionally, as designs move to finer process geometries, the Aeonic Generate area continues to scale, making it an ideal solution for future designs.

A Couple of Use Cases

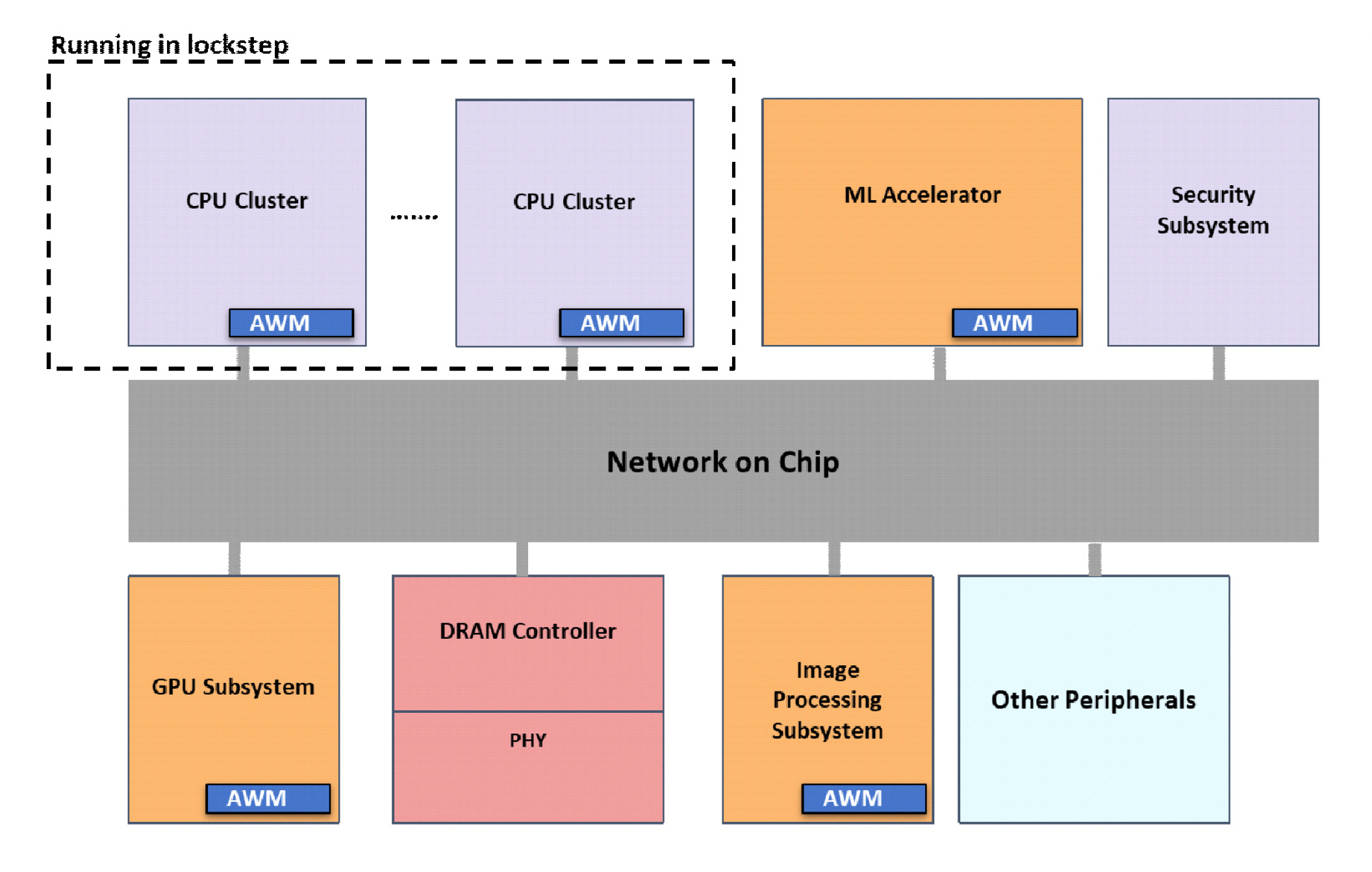

The following Figure from Movellus shows an example architecture of an ADAS processor with the Aeonic Generate AWM Platform for localized droop support. An architect would pair an AWM module with an application-specific sub-block or accelerator to respond to workload-driven localized droops within five clock cycles with glitch-less and rapid frequency shifts. This approach provides a reliable and efficient solution for addressing the challenges of localized droops in ADAS, 5G, and data center networking markets.

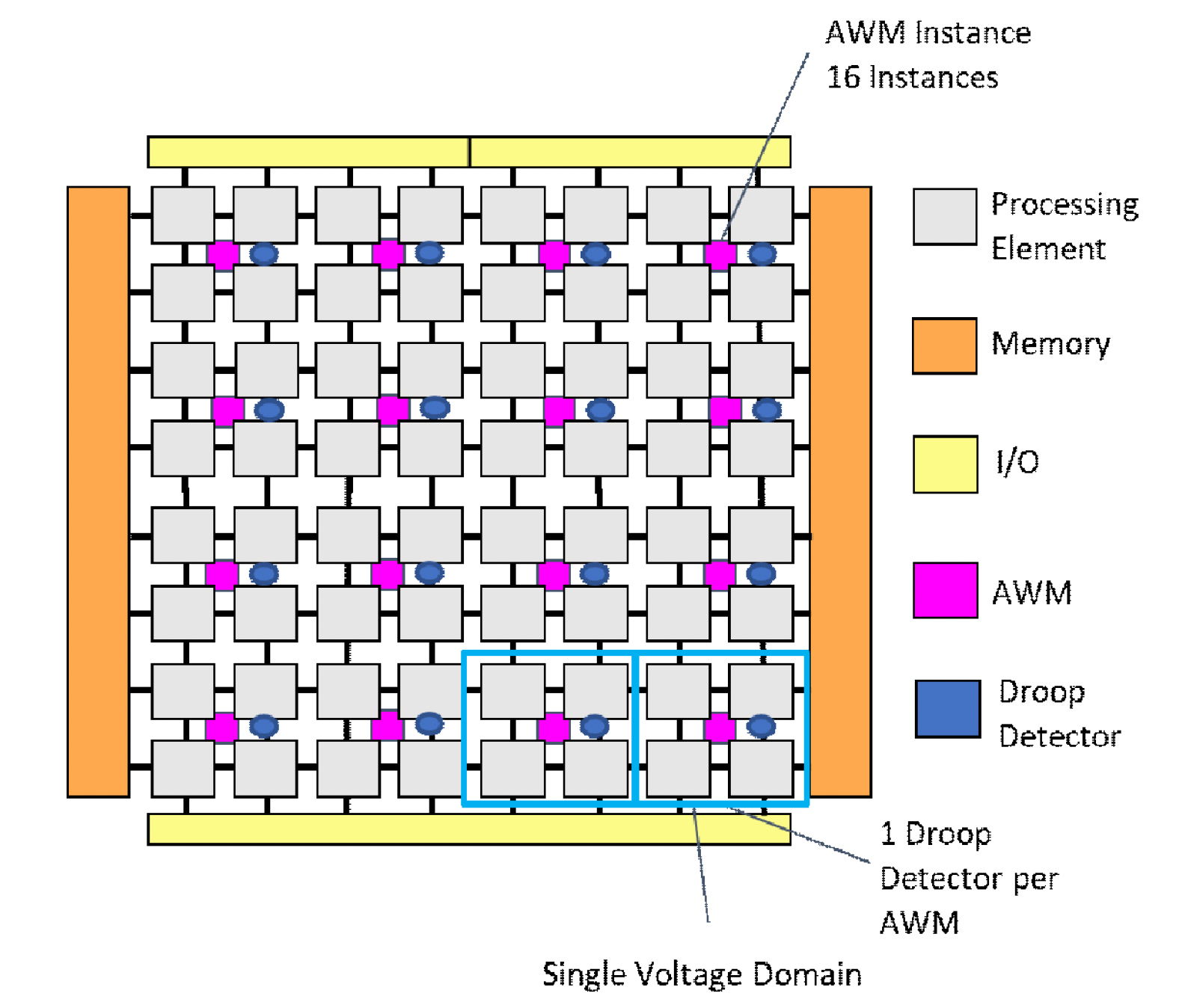

The following Figure from Movellus shows an example architecture of a sea of processor SoC with Aeonic Generate for localized droop support. An architect would pair an Aeonic Generate AWM module with a droop detector for the processor cluster and associated voltage domain to rapidly respond to workload-driven localized droops. This allows designers to deliver localized and independent droop response without altering the performance of neighboring processor clusters.

まとめ

Localized voltage droops can occur in heterogeneous SoCs containing application-specific accelerators. These droops can lead to timing glitches, transient glitches and mission-mode failures in ADAS, data center networking and 5G applications. System architects can implement adaptive clocking to respond to these droops and mitigate the impact.

The Movellus™ Aeonic Generate Adaptive Workload Module (AWM) family of high-performance clock generation IP products are part of the Aeonic Intelligent Clock Network™ architecture. For more information, refer to Movellus’ Aeonic Generate™ AWM page.

また読む:

Advantages of Large-Scale Synchronous Clocking Domains in AI Chip Designs

Performance, Power and Area (PPA) Benefits Through Intelligent Clock Networks

この投稿を共有する:- SEO を活用したコンテンツと PR 配信。 今日増幅されます。

- Platoblockchain。 Web3メタバースインテリジェンス。 知識の増幅。 こちらからアクセスしてください。

- 情報源: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :は

- 5G

- a

- 加速器

- 加速器

- 精度

- 達成

- アクティビティ

- 適応する

- ADA

- 添加

- さらに

- 住所

- アドレッシング

- 調整

- 高度な

- AI

- ことができます

- &

- アプローチ

- 建築

- です

- AREA

- AS

- 関連する

- At

- ベース

- BE

- になる

- 以下

- 利点

- ブロック

- ブロック

- 建物

- 内蔵

- by

- 缶

- 取得することができます

- 慎重に

- 例

- 壊滅的な

- 原因となる

- センター

- 課題

- チップ

- チップ

- 時計

- クラスタ

- コマンドと

- 競争する

- コンプリート

- 複雑な

- 計算

- コンピューティング

- 条件

- 考慮

- 見なさ

- 消費

- 続ける

- 腐敗

- 費用

- 可能性

- カウンター

- カップル

- ここから

- 電流プローブ

- 顧客

- サイクル

- データ

- データセンター

- データセンター

- 中

- 配信する

- 厳しい

- 設計

- 設計

- デザイナー

- 設計

- デザイン

- 発展した

- デジタル

- 配布

- 異なる

- ドメイン

- ドメイン

- 描かれた

- Drop

- ドロップス

- ダイナミック

- 動的に

- 各

- 効率

- 効率的な

- 要素は

- 環境

- 環境

- エラー

- 等

- 例

- 不良解析

- フォールズ

- 家族

- フィギュア

- フレキシブル

- 変動

- フォロー中

- フォーム

- 周波数

- から

- function

- 未来

- 一般的用途

- 生成する

- 世代

- 取得する

- グローバル

- Go

- 目標

- 起こる

- 起こります

- 持ってる

- ハイ

- ハイパフォーマンス

- HTTPS

- 理想

- 影響

- 影響

- 実装する

- in

- 不正確

- 含ま

- 増える

- 増加した

- 増加

- の増加

- 独立しました

- 情報

- 統合された

- 統合

- インテリジェント-

- 本質的に

- IP

- 問題

- 問題

- IT

- 大

- 大規模

- つながる

- 主要な

- レベル

- 賠償責任

- 生活

- ローカル

- より長いです

- 製

- 維持する

- 作る

- 作成

- 管理

- マージン

- マーケット

- 最大幅

- メソッド

- 軽減する

- 緩和する

- 緩和

- モジュール

- モジュール

- 他には?

- 最も

- 自然

- ニーズ

- ネットワーク

- ネットワーキング

- ノイズ

- 特に

- 数

- of

- オファー

- on

- ONE

- オペレーティング

- 業務執行統括

- 最適化

- 最適化

- 最適化

- その他

- 出力

- 部

- パフォーマンス

- 実行

- 現象

- プラットフォーム

- プラトン

- プラトンデータインテリジェンス

- プラトデータ

- ポートフォリオ

- ポスト

- 潜在的な

- 電力

- 電源

- プロセス

- 処理

- プロセッサ

- プロセッサ

- 製品

- プロバイダー

- は、大阪で

- 上げる

- 範囲

- 急速な

- 急速に

- 読む

- への

- 理由は

- 電話代などの費用を削減

- 規制

- 信頼性

- 信頼性のある

- の提出が必要です

- 反応します

- 応答

- 結果

- 結果として

- 上昇

- リスク

- ラン

- 規模

- スケーリング

- SEA

- 深刻な

- 厳しい

- シフト

- 作品

- シグナル

- 重要

- 著しく

- より小さい

- スマート

- 溶液

- ソリューション

- 一部

- スペース

- そのような

- 突然の

- 供給

- サポート

- がち

- システム

- タンデム

- テクノロジー

- 用語

- それ

- エリア

- アプリ環境に合わせて

- それら

- ボーマン

- 介して

- 時間

- <font style="vertical-align: inherit;">回数</font>

- タイミング

- 〜へ

- 今日の

- あまりに

- 伝統的な

- つかいます

- 非常に多様

- 、

- 電圧

- WELL

- 周知

- which

- ワイド

- 広い範囲

- 広く

- 意志

- 以内

- 無し

- でしょう

- ゼファーネット