זה היה חזרה פנימה 1991 ש-Cadence הכריזה לראשונה על שם המוצר Virtuoso, והנה אנחנו 32 שנים מאוחר יותר והמוצר חי ועושה די טוב. סטיבן לואיס מקידנס נתן לי עדכון על משהו חדש שהם קוראים לו סטודיו וירטואוז, וזה הכל על עיצוב IC מותאם אישית לעולם האמיתי. באותן 32 שנים ראינו את תהליך המוליכים למחצה צועד לאורך חוק מור מ-600 ננומטר באמצעות CMOS מישוריים, מטה לעידן FinFET מתחת ל-22 ננומטר, ומגיע ל-GAA בצומת ה-3 ננומטר. ברור שדרישות כלי ה-EDA השתנו כאשר צמתים קטנים יותר הביאו השפעות פיזיות חדשות שצריך לעצב ולדמות כדי להבטיח הצלחה ראשונה בסיליקון.

המיקוד של Cadence Virtuoso Studio הוא לעזור למעצבי IC להתמודד עם אתגרי היום באמצעות שישה תחומים:

- מורכבות מוגברת של התהליך

- טיפול ב-10,000 אלפי סימולציות מעגלים

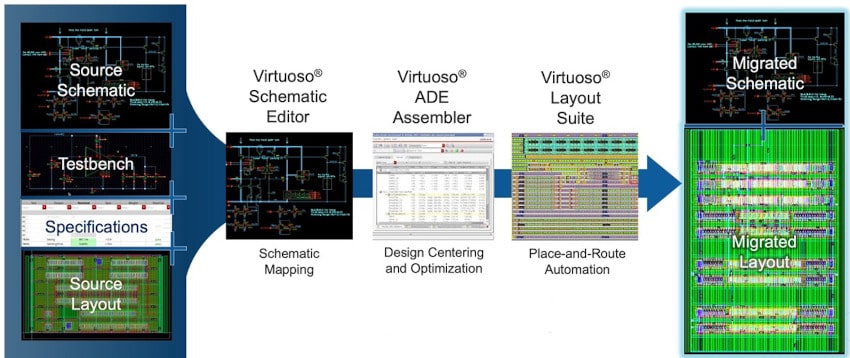

- תכנון אוטומציה והגירת מעגלים

- אינטגרציה הטרוגנית

- AI

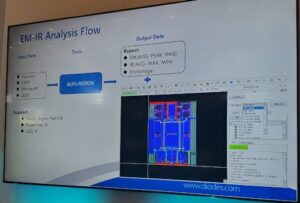

- חתימה, אימות וניתוח בתכנון

אל האני ADE וירטואוזית (סביבת עיצוב אנלוגי) מאפשרת למהנדסי מעגלים לחקור את העיצובים האנלוגיים, האותות המעורבים וה-RFIC שלהם באמצעות לכידה סכמטית והדמיית מעגלים. הארכיטקטורה של Virtuoso ADE שופצה לשליטה טובה יותר בעבודה, הפחתת שימוש ב-RAM והאצת סימולציות על ידי שימוש בענן. לדוגמה, זיכרון ה-RAM הנדרש להפעלת Spectre ב-10,000 אלפי סימולציות הצטמצם מ-420MB ל-18MB בלבד לניטור סימולציה, בעוד הערכות ביטוי ירדו מ-420MB של RAM ל-280MB בלבד.

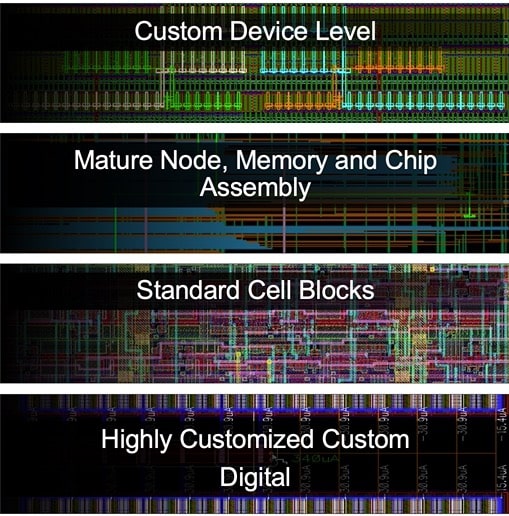

עדכונים ל- סוויטת פריסה וירטואוזית כוללים ארבע אפשרויות של טכנולוגיית מקום ומסלול, כל אחת מתאימה למשימה הייחודית שעל הפרק באמצעות הסביבה הוירטואוזית:

ארבע טכנולוגיות P&R

ריצות DRC ו-LVS הן חלק מאימות פיזי, והרצת אלה במצב אצווה, תיקון וחזרה, מובילה ללוחות זמנים של פיתוח ארוכים. אימות בתכנון מאפשר שימוש אינטראקטיבי ב-DRC ו-LVS תוך כדי עבודה על פריסת IC, כך שמשוב על מה לשנות מודגש במהירות, ומאיץ את הפרודוקטיביות. מעצב פריסה המשתמש ב-Virtuoso Layout Suite נהנה מאימות בתוך העיצוב באמצעות פגסוס טכנולוגיית DRC ו-LVS.

Chiplets, אריזות 2.5D ו-3D משתרעות על התחומים הנפרדים באופן מסורתי של תחומי עיצוב PCB, חבילות ו-IC. Virtuoso Studio מאפשר עיצוב משותף ואימות של חבילות, מודולים ו-ICs על ידי:

במבט אל העתיד הקרוב אתה יכול לצפות לראות פרטים על האופן שבו AI מיושם כדי לעבור אוטומטית מסכימה אנלוגית לפריסה המבוססת על למידת מכונה ומפרטים. פריסות ניסוי שנוצרו אוטומטית יזרזו עוד יותר תהליך עתיר עבודה. תחום פיתוח שני ליישום AI הוא הבעיה של העברת IP אנלוגי מותאם אישית לצומת תהליך חדש. המשך לעקוב.

לקוחות מוקדמים של Virtuoso Studio כוללים מכשירים אנלוגיים לעיצוב משותף של IC וחבילה, עיצובי צרכני IC מובילים ב-MediaTek והגירת תהליכים מבוססי בינה מלאכותית ב-Renesas.

<br> סיכום

Virtuoso Studio הכניס לגרסה 23.1 כמה תכונות חדשות ומרשימות שצוותי עיצוב IC יכולים להתחיל להשתמש בהן כדי להיות פרודוקטיביים יותר. התשתית הוירטואוזית השתנתה כדי לעמוד באתגרים של חוק מור, סימולציות עם סימולציות של 10,000 מעגלים הן מעשיות, RFIC ועיצוב משותף 2.5D/3D נתמכים, אימות DRC/LVS בתכנון לוקח הרבה פחות זמן, ובינה מלאכותית היא מיושם לאוטומציה של משימות אנלוגיות.

בלוגים קשורים

שתף את הפוסט הזה באמצעות:- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- Platoblockchain. Web3 Metaverse Intelligence. ידע מוגבר. גישה כאן.

- הטבעת העתיד עם אדריאן אשלי. גישה כאן.

- מקור: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :יש ל

- :הוא

- $ למעלה

- 1

- 10

- 3d

- a

- אודות

- מאיצה

- AI

- תעשיות

- מאפשר

- לאורך

- ו

- הודיע

- יישומית

- ארכיטקטורה

- ARE

- AREA

- אזורים

- AS

- At

- אוטומטי

- באופן אוטומטי

- אוטומציה

- בחזרה

- מבוסס

- BE

- היה

- להיות

- להלן

- הטבות

- מוטב

- מובא

- by

- קיידנס

- שיחה

- CAN

- ללכוד

- האתגרים

- שינוי

- בחירות

- בבירור

- ענן

- צרכן

- לִשְׁלוֹט

- מנהג

- לקוחות

- יְוֹם

- דרישות

- עיצוב

- מְעַצֵב

- מעצבים

- עיצובים

- פרטים

- צעצועי התפתחות

- התקנים

- עושה

- תחומים

- מטה

- כל אחד

- תופעות

- מאפשר

- מהנדסים

- לְהַבטִיחַ

- סביבה

- תקופה

- הערכות

- דוגמה

- לצפות

- לחקור

- תכונות

- מָשׁוֹב

- ראשון

- להתמקד

- בעד

- ארבע

- החל מ-

- נוסף

- עתיד

- Go

- יד

- יש

- לעזור

- כאן

- מודגש

- איך

- HTML

- HTTPS

- ICS

- מרשים

- in

- לכלול

- תשתית

- אינטראקטיבי

- IP

- עבודה

- jpg

- עבודה

- חוק

- מערך

- מוביל

- למידה

- לואיס

- ארוך

- מכונה

- למידת מכונה

- צעדה

- max-width

- לִפְגוֹשׁ

- הֲגִירָה

- מצב

- מודול

- מודולים

- ניטור

- יותר

- שם

- ליד

- נחוץ

- חדש

- תכונות חדשות

- צומת

- צמתים

- of

- on

- ONE

- חבילה

- חבילות

- אריזה

- חלק

- גופני

- מקום

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- הודעה

- מעשי

- להציג

- בעיה

- תהליך

- המוצר

- פּרוּדוּקטִיבִי

- פִּריוֹן

- גם

- מהירות

- RAM

- הגעה

- ממשי

- עולם אמיתי

- מופחת

- הפחתה

- לשחרר

- נדרש

- מסלול

- הפעלה

- ריצה

- דרוג

- שְׁנִיָה

- ראה פרטים

- סמיקונדקטור

- נפרד

- סיליקון

- הדמיה

- שישה

- קטן יותר

- So

- כמה

- משהו

- משך

- מפרטים

- ספקטרום

- מְהִירוּת

- התחלה

- להשאר

- סטודיו

- הצלחה

- מערכת

- נתמך

- לקחת

- לוקח

- המשימות

- משימות

- צוותי

- טכנולוגיה

- זֶה

- אל האני

- שֶׁלָהֶם

- אלה

- דרך

- זמן

- ל

- כלי

- באופן מסורתי

- מִשׁפָּט

- ייחודי

- עדכון

- נוֹהָג

- להשתמש

- אימות

- באמצעות

- טוֹב

- מה

- בזמן

- יצטרך

- עם

- עובד

- עוֹלָם

- שנים

- זפירנט