מאמר טכני חדש שכותרתו "עיצוב לא מסורתי של לוגיקה דינמית באמצעות FDSOI עבור מחשוב יעיל במיוחד" פורסם על ידי חוקרים מאוניברסיטת שטוטגרט, UC ברקלי, המכון ההודי לטכנולוגיות Kanpur ו-TU מינכן, במימון קרן המחקר הגרמנית .

תַקצִיר

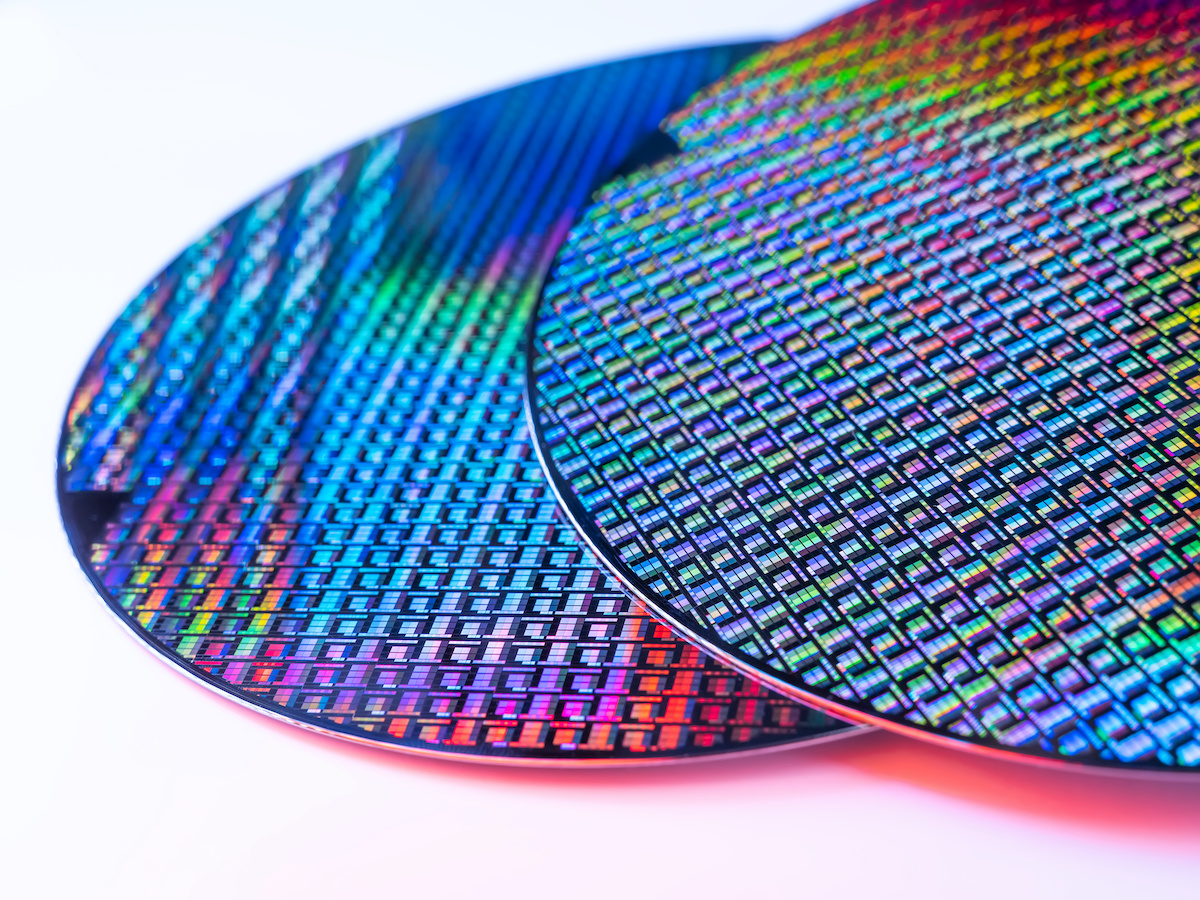

"במאמר זה, אנו מציעים תכנון לא מסורתי של מעגלים לוגיים דינמיים באמצעות FETs של סיליקון מבודד לחלוטין (FDSOI). FDSOI FET מאפשר את מתח הסף (Vt ) להיות מתכוונן (כלומר, מצבי Vt נמוך ו-Vt גבוה) באמצעות הטיית השער האחורי. התכנון שלנו מנצל את השערים הקדמיים והאחוריים של FDSOI FET כמסופי הכניסה ומציע את השערים הלוגיים הדינמיים (כמו; NAND, NOR, AND, OR, XOR ו-XNOR) ומעגלים (כמו; חצי מוסיף ומוסיף מלא). זה דורש פחות טרנזיסטורים כדי לבנות שערים לוגיים דינמיים ומשיג ביצועים גבוהים עם פיזור הספק נמוך בהשוואה לתכנונים לוגיים דינמיים קונבנציונליים. המודל התעשייתי הקומפקטי של FDSOI FET (BSIM-IMG) שימש כדי לדמות שערים לוגיים דינמיים והוא מכויל במלואו לשחזור נתוני ה-FDSOI FET של טכנולוגיית 14nm. הכיול מתבצע הן עבור מאפיינים חשמליים והן עבור וריאציות של תהליך. תוצאות הסימולציה מראות שיפור ממוצע בספירת טרנזיסטורים, עיכוב התפשטות, הספק ותוצר השהיית הספק של 23.43%, 57.16%, 47.05% ו-77.29%, בהתאמה, בהשוואה לתכנונים המקובלים. יתר על כן, העיצוב שלנו מפחית את אפקט חלוקת המטענים, אשר משפיע על יכולת הנסיעה של שערי הלוגיקה הדינמיים. בנוסף, ניתחנו בפירוט את ההשפעה של התהליך, מתח האספקה וריאציות קיבול העומס על עיכוב ההתפשטות של משפחת הלוגיקה הדינמית. התוצאות מראות שלווריאציות אלו יש השפעה מינורית על עיכוב ההתפשטות של השערים הלוגיים הדינמיים המוצעים מבוססי FDSOI בהשוואה לשערי הלוגיקה הדינמיים הרגילים".

מצא מאמר טכני כאן. פורסם באפריל 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan ו-H. Amrouch, "עיצוב לא מסורתי של לוגיקה דינמית באמצעות FDSOI עבור מחשוב יעיל במיוחד," ב-IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. פתח את הגישהs.

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoAiStream. Web3 Data Intelligence. הידע מוגבר. גישה כאן.

- הטבעת העתיד עם אדריאן אשלי. גישה כאן.

- קנה ומכירה של מניות בחברות PRE-IPO עם PREIPO®. גישה כאן.

- מקור: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- :יש ל

- :הוא

- 10

- 2023

- 23

- 77

- a

- משיגה

- תוספת

- מתכוונן

- מאפשר

- an

- ו

- אַפּרִיל

- AS

- At

- מְמוּצָע

- בחזרה

- BE

- היה

- ברקלי

- הטיה

- שניהם

- לִבנוֹת

- by

- מאפיינים

- תשלום

- לעומת

- מחשוב

- מקובל

- נתונים

- עיכוב

- עיצוב

- עיצובים

- פרט

- התקנים

- דינמי

- e

- השפעה

- משפחה

- FET

- פחות

- בעד

- קרן

- חזית

- מלא

- לגמרי

- מימון

- נוסף

- גייטס

- גרמנית

- מחצית

- יש

- גָבוֹהַ

- HTTPS

- i

- IEEE

- פְּגִיעָה

- השבחה

- in

- הוֹדִי

- התעשייה

- קלט

- מכון

- IT

- כתב עת

- כמו

- לִטעוֹן

- הגיון

- נמוך

- קטין

- מודל

- מינכן

- חדש

- צומת

- of

- on

- or

- שלנו

- מאמר

- ביצועים

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- כּוֹחַ

- תהליך

- המוצר

- להציע

- מוּצָע

- מציע

- לאור

- מפחית

- דורש

- מחקר

- חוקרים

- בהתאמה

- תוצאות

- s

- שיתוף

- לְהַצִיג

- סיליקון

- הדמיה

- הברית

- לספק

- טכני

- טכנולוגיה

- זֶה

- אל האני

- אלה

- זֶה

- סף

- שכותרתו

- ל

- אוניברסיטה

- מְשׁוּמָשׁ

- באמצעות

- מנצל

- מתח

- היה

- we

- אשר

- עם

- זפירנט