Synopsys פרסמה באתר SolvNet הרצאה מרתקת שהעביר ד"ר תיאו דריין מ-Intel Graphics. הנושא הוא בדיקת שוויון נתיב נתונים. אולי נשמע כמו עוד אישור DPV פורמלי של Synopsys VC, אבל אתה צריך לראות את זה בכל מקרה. זהו דיון מרחיב תודעה על השימושים והשיקולים בפורמלי, אשר ייקח אותך מעבר לסוג של מדריך למשתמש השגרתי של נדנדה לטריטוריה מרתקת יותר.

הבנה אינטלקטואלית לעומת בדיקה לדוגמה

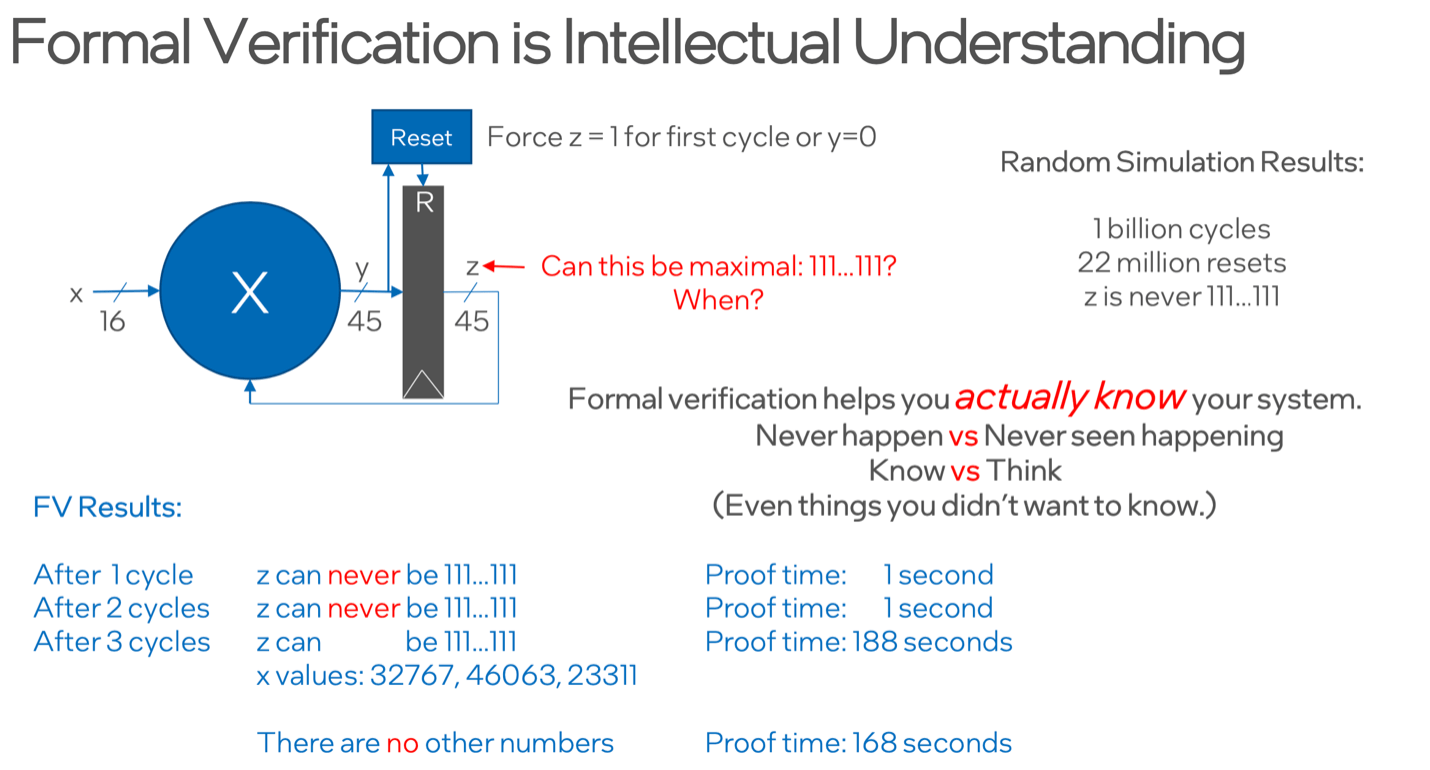

סימולציה מונעת מבחן על כל צורותיה היא מצוינת ולעיתים בלתי ניתנת להחלפה באימות נכונות מפרט או יישום תכנון. זה גם קל להתחיל. פשוט כתוב תוכנית בדיקה ותתחיל לדמות. אבל הצד השני של הפשטות הזו הוא שאנחנו לא צריכים לגמרי להבין מה אנחנו בודקים כדי להתחיל. אנחנו משכנעים את עצמנו שקראנו את המפרט בעיון ומבינים את כל המקרים הפיננסיים, אבל לא צריך הרבה מורכבות מורכבת כדי להציף את ההבנה שלנו.

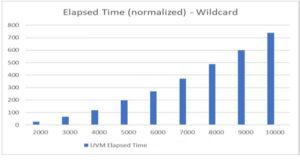

פורמלי מעודד אותך להבין את הפונקציונליות ברמה עמוקה (לפחות אם אתה רוצה לספק תוצאה בעלת ערך). בדוגמה שלמעלה, שאלה פשוטה - האם z יכול להיות כל 1 - לא מצליחה להדגים דוגמה במיליארד מחזורים בסימולטור. לא מפתיע, שכן מדובר במקרה פינתי קיצוני. מבחן רשמי מספק דוגמה ספציפית ומאוד לא ברורה ב-188 שניות ויכול להוכיח שזהו המקרה היחידי בקצת פחות זמן.

בסדר רשמי עשה את מה שבדיקות דינמיות לא יכלו לעשות, אבל חשוב מכך למדת משהו שהסימולטור אולי לא אמר לך מעולם. שהיה רק מקרה אחד אפשרי שבו המצב הזה יכול לקרות. פורמלי עזר לך להבין טוב יותר את העיצוב ברמה אינטלקטואלית, לא רק כסיכום הסתברותי על פני קבוצה סופית של מקרי מבחן.

בעיות במפרט

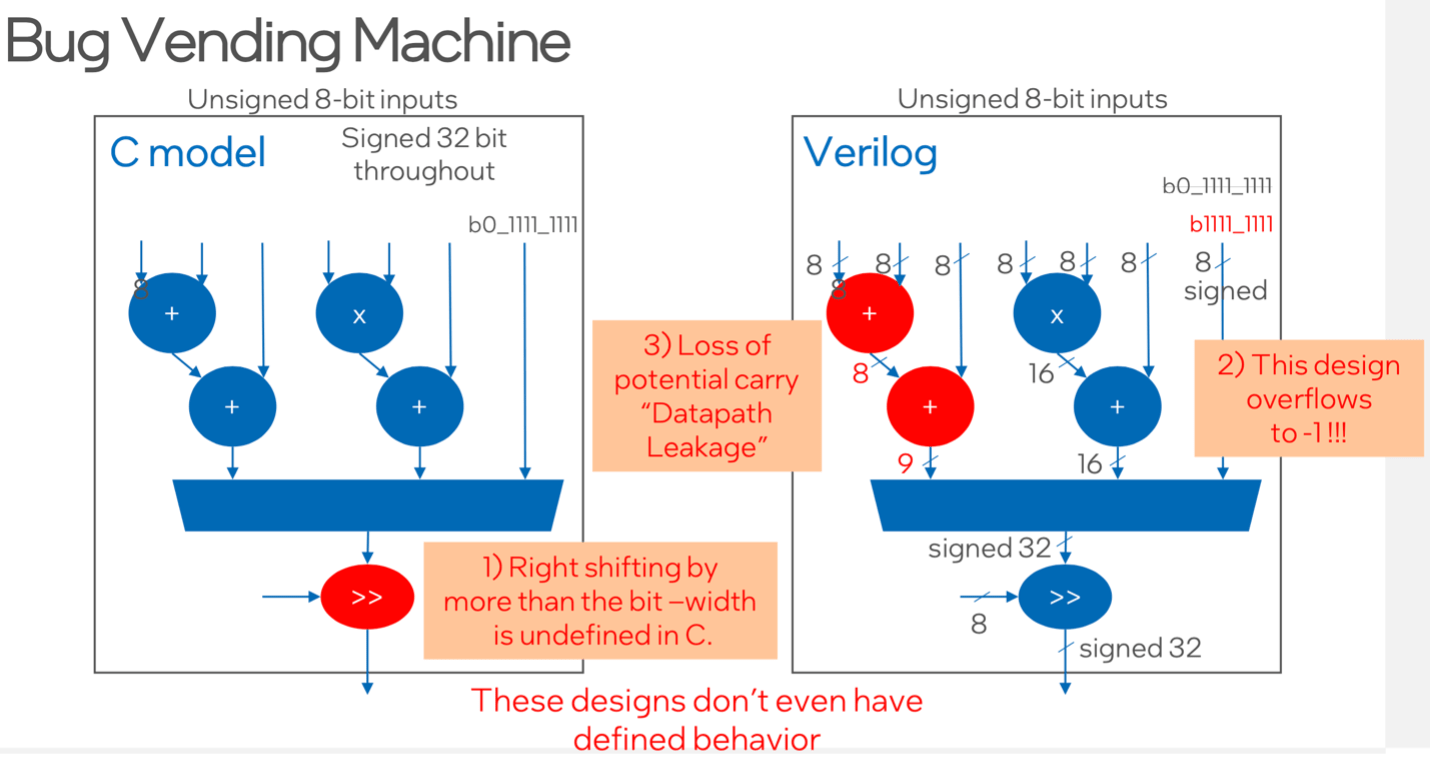

הדוגמה הבאה של תיאו מבוססת על מכונה אוטומטית של באגים (נקראת כך כי כשאתה לוחץ על כפתור אתה מקבל באג). זה נראה כמו בעיה די פשוטה של בדיקת שוויון C ל-RTL, דגם C משמאל, דגם RTL מימין. אחת ההפתעות עבור תיאו בימיו הראשונים בפורמליות הייתה שהתנהגות העברה ימנית בדגם C אינה מוגדרת לחלוטין בתקן C, למרות ש-gcc יתנהג בצורה סבירה. עם זאת, DPV תתלונן על אי התאמה בהשוואה ל-RTL, כפי שצריך. התנהגות לא מוגדרת היא דבר מסוכן להסתמך עליו.

השוואת מפרט בין C ל-RTL מגיעה עם סיכונים אחרים, במיוחד סביב רוחבי סיביות. חיתוך או אובדן של סיבית העברה באות ביניים (מס' 3 לעיל) הן דוגמאות טובות. האם אלו בעיות מפרט? אולי אזור אפור בין מפרט ובחירות יישום.

מעבר לבדיקת שוויון

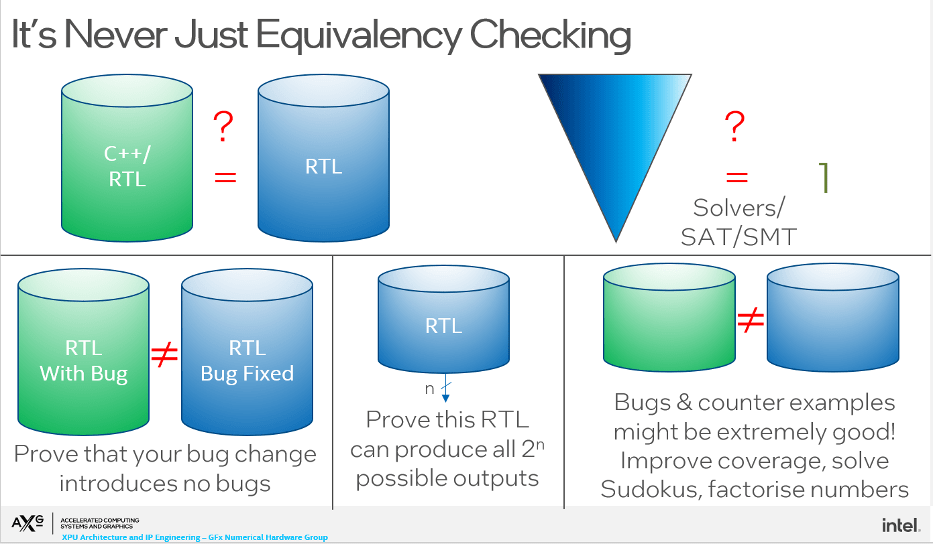

המטרה העיקרית של DPV, כך נראה, היא לבדוק שוויון בין התייחסות C או RTL לבין יישום RTL. אבל הצורך הזה הוא נדיר יחסית ויש דרכים שימושיות אחרות שטכנולוגיה כזו עשויה להיות מיושמת, אם היא קצת מחוץ לקופסה. תחילה קלאסיקה בעולם ההטמעה - עשיתי שינוי, תיקנתי באג - האם הצגתי באגים חדשים כתוצאה מכך? קצת כמו בדיקת SEQ לאחר הוספת שער שעון. ניתוח נגישות בפלטי בלוק עשוי להיות יישום שימושי נוסף במקרים מסוימים.

תיאו נעשה אפילו יותר יצירתי, ומבקש מהחניכים להשתמש בדוגמאות נגד כדי להבין טוב יותר את העיצוב, לפתור סודוקוס or לפרק מספרים שלמים. הוא מכיר בכך ש-DPV מהווה דרך מוזרה לגשת לבעיות כאלה, אך מציין שכוונתו היא לשבור את האשליה ש-DPV מיועד רק לבדיקת שוויון. רעיון מעניין ובהחלט מותח את המוח לחשוב על אתגרים כאלה. (אני מודה שהתחלתי מיד לחשוב על בעיית הסודוקו ברגע שהוא הזכיר אותה.)

לעטוף

תיאו מסיים בדיון על מתודולוגיות חשובות בשימוש בייצור, סביב אילוצים, רגרסיות והשוואות עם מודלים של RTL מדור קודם. כמו כן האתגרים לדעת אם מה שאתה בודק אכן תואם את מפרט השפה הטבעית ברמה העליונה.

דיבור ממריץ מאוד, שווה צפייה כאן ב-SolvNet!

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- Platoblockchain. Web3 Metaverse Intelligence. ידע מוגבר. גישה כאן.

- מקור: https://semiwiki.com/eda/325878-intel-keynote-on-formal-a-mind-stretcher/

- :הוא

- a

- אודות

- מֵעַל

- לרוחב

- למעשה

- לאחר

- תעשיות

- אנליזה

- ו

- אחר

- בקשה

- יישומית

- גישה

- ARE

- AREA

- סביב

- AS

- At

- מבוסס

- BE

- כי

- מוטב

- בֵּין

- מעבר

- B

- קצת

- לחסום

- אריזה מקורית

- לשבור

- חרק

- באגים

- לַחְצָן

- by

- נקרא

- CAN

- בזהירות

- לשאת

- מקרה

- מקרים

- בהחלט

- האתגרים

- שינוי

- לבדוק

- בדיקה

- בחירות

- קלאסי

- שעון

- השוואה

- לחלוטין

- מורכבות

- מצב

- שיקולים

- אילוצים

- לְשַׁכְנֵעַ

- בפינה

- יכול

- דלפק

- יְצִירָתִי

- מחזורי

- מסוכן

- ימים

- עמוק

- מוגדר

- למסור

- להפגין

- עיצוב

- DID

- דיון

- לא

- לא

- דינמי

- מוקדם

- מעודד את

- במיוחד

- אֲפִילוּ

- אי פעם

- דוגמה

- דוגמאות

- מצוין

- קיצוני

- נכשל

- מקסים

- ראשון

- קבוע

- Flip

- בעד

- רִשְׁמִי

- צורות

- פונקציונלי

- GCC

- לקבל

- נתן

- טוב

- גרפיקה

- אפור

- אזור אפור

- לקרות

- יש

- עזר

- אולם

- HTTPS

- i

- רעיון

- מיד

- הפעלה

- חשוב

- in

- אינטל

- אִינטֶלֶקְטוּאַלִי

- כוונה

- מעניין

- ביניים

- מבוא

- בעיות

- IT

- שֶׁלָה

- Keynote

- סוג

- יודע

- שפה

- למד

- מוֹרֶשֶׁת

- רמה

- כמו

- קְצָת

- נראה

- את

- מכונה

- עשוי

- לעשות

- max-width

- מוּזְכָּר

- מתודולוגיות

- יכול

- מודל

- מודלים

- יותר

- טבעי

- שפה טבעית

- צורך

- חדש

- הבא

- of

- on

- ONE

- אחר

- גובה הצליל

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- נקודות

- אפשרי

- הודעה

- פורסם

- ללחוץ

- יפה

- יְסוֹדִי

- בעיה

- בעיות

- הפקה

- תָכְנִית

- להוכיח

- מספק

- מטרה

- שאלה

- חומר עיוני

- יחסית

- תוצאה

- שניות

- סט

- צריך

- לאותת

- פָּשׁוּט

- פשטות

- הדמיה

- מדמה

- since

- אתר

- So

- כמה

- משהו

- בקרוב

- קול

- ספציפי

- מפרט

- תֶקֶן

- התחלה

- החל

- פשוט

- כזה

- סיכום

- הפתעה

- מפתיע

- לקחת

- לדבר

- טכנולוגיה

- מבחן

- בדיקות

- זֶה

- השמיים

- אלה

- דבר

- חושב

- דרך

- זמן

- ל

- הרמה העליונה

- נושא

- גְמִימָה

- להבין

- הבנה

- נוֹהָג

- להשתמש

- בעל ערך

- VC

- אימות

- נגד

- באמצעות

- שעון

- צופה

- דֶרֶך..

- דרכים

- טוֹב

- מה

- אם

- אשר

- יצטרך

- עם

- עוֹלָם

- ראוי

- היה

- לכתוב

- זפירנט