צ'יפלטים פישטו תחום עיצוב אחד אך פתחו את תיבת הפנדורה בחזית אחרת. מורכבות הסימולציה של כל אחד מהם שבב הוא נמוך יותר, אך כעת החיבור בין שבב לצ'יפלט הפך למורכב. אנשים מתנסים עם פרוטוקולי חיבור שונים, וריאציות של UCIe, שינוי הגדרות UCIe, מהירויות ממשק, מספר שכבות פיזיות וכדומה. כעת הוסף סטנדרטים מדור קודם כמו AXI, פרוטוקולים חדשים כמו PICe6.0 וקוהרנטיות מטמון לתערובת.

בסך הכל, זה יוצר סט חדש לגמרי של ניסויים. כזה שעבורו האמולציה המסורתית ודוגמנות RTL לא יעבדו. תחילה עליך להשקיע מאמץ בשינוי בארכיטקטורה, לא רק בבחירת רכיבים. משמעות הדבר היא שתצטרך לבצע ניתוח תעבורה, חלוקת אפליקציות, גודל מערכת והשפעה של סוגים שונים של שכבות פיזיות. כמו כן, בהתאם ליישום המדד יהיה שונה מאוד.

מפרט ה-UCIe חדש ואין אמות מידה ברורות. כמו כן, מפרט UCIe מספק הנחיות רק לגבי זמן השהייה והספק. שתיהן דרישות מחמירות. המשמעות היא שמחקר כוח-ביצועים-אזור הוא נמנע. מכיוון שיש לך המרת פרוטוקול-פרוטוקול-פרוטוקול כגון PCIe 6.0 ל-UCIe ל-AXI, הגדרת המודלים מורכבת.

פתרון אחד הוא להסתכל על מודלים של מערכת באמצעות VisualSim החל מ- מיראביליס לְעַצֵב. לאחרונה הם השיקו מודל IP ברמת מערכת UCIe וידגימו מספר מקרי שימוש של החיבור בין פסגת צ'יפלט. כדי להדריך את המעצבים, הם פרסמו מדריך עם המון מקרי שימוש, תוצאות צפויות של ביצועי כוח ואפשרויות אופטימיזציה. יש להם גם מצגת נייר וגם דוכן בפסגה. אני מקווה לראות אותך שם!

כמו כן, הנה הקישור למאמר שאנשים יכולים להשיג: מודל ביצועים של מערכת מחשוב הטרוגנית המבוססת על ארכיטקטורת UCIe Interconnect

תקציר:

עיצובי השבבים המורכבים של היום בצמתים מובילים מורכבים בדרך כלל ממספר קוביות (או שבבים). הגישה מאפשרת תבניות מיצרנים או תהליכים שונים, כמו גם IP לשימוש חוזר. מעצבים צריכים מודל ברמת המערכת כדי להעריך יישומים שונים של מצבים מורכבים כאלה.

מערכת לדוגמה מורכבת מצ'יפלט קלט/פלט, שבבי ליבה בהספק נמוך, שבפל ליבה בעל ביצועים גבוהים, שבבי אודיו-וידאו וצ'יפלט אנלוגי, המחוברים ביניהם באמצעות תקן Universal Chiplet Interconnect Express (UCIe).

הצוות שלנו שקל מספר תרחישים ותצורות, כולל חבילות מתקדמות וסטנדרטיות, פרופילי תנועה ומשאבים מגוונים וטיימר להרחבת טווח ההגעה ולהערכת אירועים בזמן קצוב. זיהוי החוזקות והחולשות של חיבור UCIe עבור יישומי משימה עזר לנו להשיג את התצורה האופטימלית עבור כל תת-מערכת כדי לעמוד בדרישות הביצועים, הכוח והפונקציונליות.

אודות Mirabilis Design Inc.

Mirabilis Design היא חברת תוכנה מעמק הסיליקון, המספקת פתרונות תוכנה והדרכה לזיהוי וביטול סיכונים במפרט המוצר, חיזוי מדויק של משאבי האנוש והזמן הנדרשים לפיתוח המוצר, ושיפור התקשורת בין הנדסה מגוונת.

צוותים.

VisualSim Architect משלב קניין רוחני, מידול ברמת המערכת, סימולציה, ניתוח סביבה ותבניות יישומים כדי לשפר משמעותית את בניית המודל, הדמיה, ניתוח ואימות RTL. הסביבה מאפשרת למעצבים להתכנס במהירות לעיצוב העונה על מערך מגוון של דרישות זמן והספק תלויות הדדית. נעשה בו שימוש מוקדם מאוד בתהליך התכנון במקביל (וכעזר ל) המפרט הכתוב ולפני יישום (לדוגמה, RTL, קוד תוכנה או סכימה) של המוצר.

גם לקרוא:

WEBINAR: כיצד להשיג מדידת כוח מדויקת של 95%+ במהלך חקר אדריכלות

קורסי עיצוב מבוסס מודלים לסטודנטים

שתף את הפוסט הזה באמצעות:

- הפצת תוכן ויחסי ציבור מופעל על ידי SEO. קבל הגברה היום.

- PlatoData.Network Vertical Generative Ai. העצים את עצמך. גישה כאן.

- PlatoAiStream. Web3 Intelligence. הידע מוגבר. גישה כאן.

- PlatoESG. פחמן, קלינטק, אנרגיה, סביבה, שמש, ניהול פסולת. גישה כאן.

- PlatoHealth. מודיעין ביוטכנולוגיה וניסויים קליניים. גישה כאן.

- מקור: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :יש ל

- :הוא

- :לֹא

- a

- מדויק

- במדויק

- להשיג

- להוסיף

- מתקדם

- סיוע

- מאפשר

- לאורך

- גם

- an

- אנליזה

- ו

- אחר

- בקשה

- יישומים

- גישה

- ארכיטקטורה

- ARE

- AREA

- AS

- At

- מבוסס

- BE

- להיות

- לפני

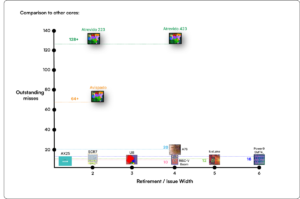

- בנצ 'מרק

- מבחני ביצועים

- בֵּין

- שניהם

- אריזה מקורית

- אבל

- מטמון

- CAN

- יכול לקבל

- מקרים

- שבב

- ברור

- קוד

- משלב

- תקשורת

- חברה

- לחלוטין

- מורכב

- מורכבות

- רכיבים

- מחשוב

- לנהל

- תְצוּרָה

- נחשב

- מורכב

- בניה

- לְהִתְכַּנֵס

- המרה

- ליבה

- קורסים

- יוצר

- הפגנה

- תלוי

- עיצוב

- תהליך עיצוב

- מעצבים

- עיצובים

- לפתח

- אחר

- שונה

- בְּמַהֲלָך

- כל אחד

- מוקדם

- מאמץ

- בוטל

- אמולציה

- מאפשר

- סביבה

- להעריך

- אירועים

- דוגמה

- צפוי

- ניסויים

- ניסויים

- אקספרס

- להאריך

- ראשון

- בעד

- החל מ-

- חזית

- פונקציונלי

- בדרך כלל

- לקבל

- הדרכה

- מדריך

- חומרה

- יש

- עזר

- כאן

- ביצועים גבוהים

- לקוות

- איך

- איך

- HTTPS

- בן אנוש

- i

- לזהות

- זיהוי

- פְּגִיעָה

- הפעלה

- יישומים

- לשפר

- in

- כולל

- אִינטֶלֶקְטוּאַלִי

- קניין רוחני

- מקושרים

- מִמְשָׁק

- IP

- IT

- jpg

- רק

- חֶבִיוֹן

- הושק

- שכבה

- שכבות

- מוֹרֶשֶׁת

- רמה

- כמו

- קשר

- נראה

- הרבה

- נמוך

- להוריד

- התעשיינים

- max-width

- אומר

- אומר

- מדידה

- לִפְגוֹשׁ

- פוגשת

- משימה

- לערבב

- מודל

- דוגמנות

- דוּגמָנוּת

- מספר

- צורך

- חדש

- לא

- צמתים

- עַכשָׁיו

- מספר

- להשיג

- of

- on

- ONE

- רק

- לפתוח

- נפתח

- אופטימלי

- אופטימיזציה

- אפשרויות

- or

- חבילות

- מאמר

- מקביל

- ביצועים

- גופני

- אפלטון

- מודיעין אפלטון

- אפלטון נתונים

- הודעה

- כּוֹחַ

- ניבוי

- הצגה

- תהליך

- תהליכים

- המוצר

- פרופילים

- רכוש

- פרוטוקולים

- מספק

- מתן

- לאור

- מהר

- לְהַגִיעַ

- חומר עיוני

- לאחרונה

- נדרש

- דרישות

- משאבים

- תוצאות

- לשימוש חוזר

- הסיכון

- תרחישים

- לִרְאוֹת

- בחירה

- סט

- הגדרות

- התקנה

- כמה

- באופן משמעותי

- סיליקון

- עמק הסיליקון

- פשוט

- הדמיה

- מצבים

- So

- תוכנה

- פִּתָרוֹן

- פתרונות

- מפרט

- מהירויות

- לבלות

- תֶקֶן

- תקנים

- חוזק

- מחמירות

- לימוד

- כזה

- פסגה

- מערכת

- נבחרת

- תבניות

- זֶה

- השמיים

- שם.

- הֵם

- זֶה

- זמן

- ל

- מסורתי

- תְנוּעָה

- הדרכה

- סוגים

- אוניברסלי

- us

- להשתמש

- מְשׁוּמָשׁ

- באמצעות

- עֶמֶק

- וריאציות

- אימות

- מאוד

- באמצעות

- חולשות

- טוֹב

- אשר

- יצטרך

- עם

- תיק עבודות

- כתוב

- אתה

- זפירנט