Era rientrato 1991 che Cadence annunciò per la prima volta il nome del prodotto Virtuoso, ed eccoci qui 32 anni dopo e il prodotto è vivo e sta andando abbastanza bene. Steven Lewis di Cadence mi ha dato un aggiornamento su qualcosa di nuovo che chiamano Studio Virtuosistico, ed è tutta una questione di progettazione di circuiti integrati personalizzati per il mondo reale. In questi 32 anni abbiamo visto il processo dei semiconduttori marciare lungo la Legge di Moore da 600 nm utilizzando CMOS planare, scendendo fino all'era FinFET al di sotto di 22 nm, raggiungendo GAA al nodo di 3 nm. Chiaramente le esigenze degli strumenti EDA sono cambiate poiché i nodi più piccoli hanno introdotto nuovi effetti fisici che dovevano essere modellati e simulati per garantire il primo successo del silicio.

L'obiettivo di Cadence Virtuoso Studio è aiutare i progettisti di circuiti integrati ad affrontare le sfide odierne attraverso sei aree:

- Maggiore complessità del processo

- Gestione di decine di migliaia di simulazioni di circuiti

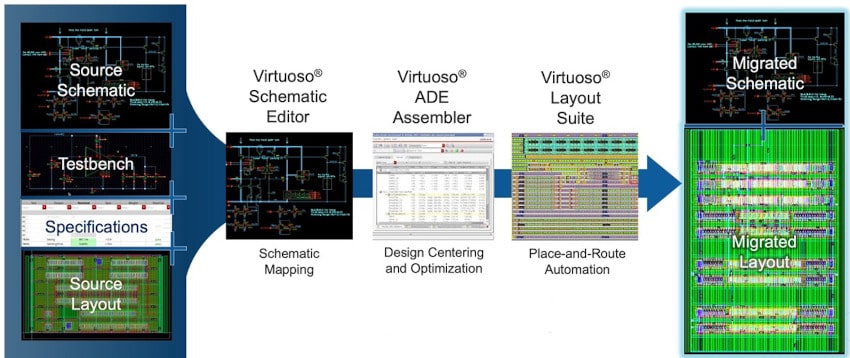

- Automazione della progettazione e migrazione dei circuiti

- Integrazione eterogenea

- AI

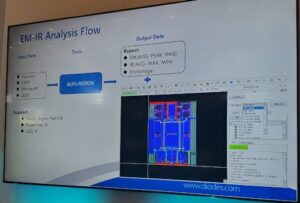

- Approvazione, verifica e analisi in fase di progettazione

I Virtuoso ADE (Analog Design Environment) consente agli ingegneri di circuiti di esplorare i loro progetti analogici, a segnale misto e RFIC attraverso l'acquisizione di schemi e la simulazione di circuiti. L'architettura di Virtuoso ADE è stata rinnovata per un migliore controllo del lavoro, riducendo l'utilizzo della RAM e accelerando le simulazioni utilizzando il cloud. Ad esempio, la RAM richiesta per eseguire Spectre su 10,000 simulazioni è stata ridotta da 420 MB a soli 18 MB per il monitoraggio delle simulazioni, mentre le valutazioni delle espressioni sono diminuite da 420 MB di RAM a soli 280 MB.

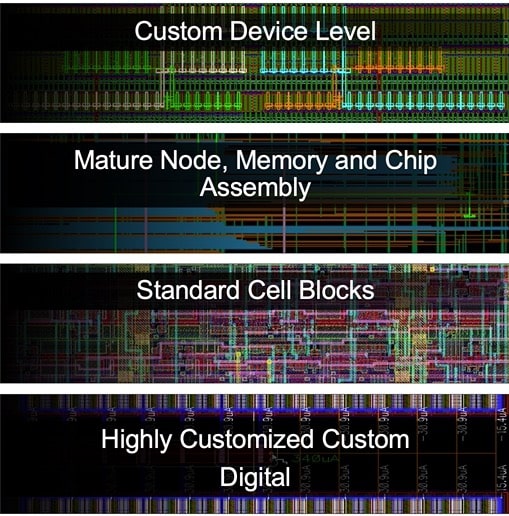

Aggiornamenti al Suite di layout virtuoso includono quattro scelte di luogo e tecnologia del percorso, ciascuna adatta al compito unico da svolgere attraverso l'ambiente Virtuoso:

Quattro tecnologie P&R

Le esecuzioni DRC e LVS fanno parte della verifica fisica e l'esecuzione di queste in modalità batch, correzione e ripetizione, porta a lunghi programmi di sviluppo. La verifica in fase di progettazione consente l'uso interattivo di DRC e LVS mentre si lavora su un layout IC, in modo che il feedback su cosa modificare venga rapidamente evidenziato, accelerando la produttività. Un progettista di layout che utilizza Virtuoso Layout Suite beneficia della verifica in-design utilizzando il file Pegasus Tecnologia DRC e LVS.

I chiplet, il packaging 2.5D e 3D abbracciano i regni tradizionalmente separati dei domini di progettazione PCB, package e IC. Virtuoso Studio consente la co-progettazione e la verifica di pacchetti, moduli e circuiti integrati tramite:

Guardando al prossimo futuro puoi aspettarti di vedere emergere dettagli su come viene applicata l'intelligenza artificiale per passare automaticamente da uno schema analogico a un layout basato sull'apprendimento automatico e sulle specifiche. Questi layout di prova generati automaticamente accelereranno ulteriormente un processo ad alta intensità di manodopera. Una seconda area di sviluppo per l’applicazione dell’IA è il problema della migrazione dell’IP analogico personalizzato verso un nuovo nodo di processo. Rimani sintonizzato.

I primi clienti di Virtuoso Studio includono Analog Devices per la co-progettazione di circuiti integrati e pacchetti, progetti di consumatori di circuiti integrati all'avanguardia presso MediaTek e migrazione di processi basati sull'intelligenza artificiale presso Renesas.

Sommario

Virtuoso Studio ha inserito nella versione 23.1 alcune nuove funzionalità impressionanti che i team di progettazione di circuiti integrati possono iniziare a utilizzare per essere più produttivi. L'infrastruttura Virtuoso è cambiata per affrontare le sfide della Legge di Moore, le simulazioni con 10,000 simulazioni di circuiti sono pratiche, sono supportati RFIC e la co-progettazione del modulo 2.5D/3D, la verifica DRC/LVS in-design richiede molto meno tempo e l'intelligenza artificiale è applicato per automatizzare attività analogiche.

Blog correlati

Condividi questo post tramite:- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Fonte: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :ha

- :È

- $ SU

- 1

- 10

- 3d

- a

- Chi siamo

- accelerando

- AI

- Tutti

- consente

- lungo

- ed

- ha annunciato

- applicato

- architettura

- SONO

- RISERVATA

- aree

- AS

- At

- automatizzare

- automaticamente

- Automazione

- precedente

- basato

- BE

- stato

- essendo

- sotto

- vantaggi

- Meglio

- portato

- by

- Cadenza

- chiamata

- Materiale

- catturare

- sfide

- il cambiamento

- scelte

- chiaramente

- Cloud

- Consumer

- di controllo

- costume

- Clienti

- giorno

- richieste

- Design

- Designer

- designer e gli illustratori veneziani,

- disegni

- dettagli

- Mercato

- dispositivi

- fare

- domini

- giù

- ogni

- effetti

- Abilita

- Ingegneri

- garantire

- Ambiente

- epoca

- valutazioni

- esempio

- attenderti

- esplora

- Caratteristiche

- feedback

- Nome

- Focus

- Nel

- quattro

- da

- ulteriormente

- futuro

- Go

- cura

- Avere

- Aiuto

- qui

- Evidenziato

- Come

- HTML

- HTTPS

- ICS

- impressionante

- in

- includere

- Infrastruttura

- interattivo

- IP

- Lavoro

- jpg

- lavoro

- Legge

- disposizione

- Leads

- apprendimento

- Lewis

- Lunghi

- macchina

- machine learning

- Marzo

- max-width

- Soddisfare

- migrazione

- Moda

- modulo

- moduli

- monitoraggio

- Scopri di più

- Nome

- Vicino

- di applicazione

- New

- Nuove funzionalità

- nodo

- nodi

- of

- on

- ONE

- pacchetto

- Packages

- imballaggio

- parte

- Fisico

- posto

- Platone

- Platone Data Intelligence

- PlatoneDati

- Post

- Pratico

- presenti

- Problema

- processi

- Prodotto

- produttivo

- della produttività

- metti

- rapidamente

- RAM

- raggiungendo

- di rose

- mondo reale

- Ridotto

- riducendo

- rilasciare

- necessario

- strada

- Correre

- running

- scala

- Secondo

- guarda i detagli

- semiconduttore

- separato

- Silicio

- simulazione

- SIX

- inferiore

- So

- alcuni

- qualcosa

- campata

- Specifiche tecniche

- Spettro

- velocità

- inizia a

- soggiorno

- studio

- il successo

- suite

- supportato

- Fai

- prende

- Task

- task

- le squadre

- Tecnologia

- che

- I

- loro

- Strumenti Bowman per analizzare le seguenti finiture:

- Attraverso

- tempo

- a

- tradizionalmente

- prova

- unico

- Aggiornanento

- Impiego

- uso

- Convalida

- via

- WELL

- Che

- while

- volere

- con

- lavoro

- mondo

- anni

- zefiro