S2C è leader globale nella prototipazione FPGA da quasi due decenni e le sue piattaforme di prototipazione FPGA hanno monitorato da vicino la disponibilità degli ultimi FPGA, inclusi gli ultimi FPGA sia di Xilinx che di Intel. E stanno sicuramente mantenendo la promessa di far progredire le loro soluzioni di prototipazione per la prototipazione di progetti su larga scala - ridimensionamento capacità e capacità della piattaforma di prototipazione per supportare progetti di gate multimiliardari.

Guardando indietro all'inizio del quarto trimestre del 4, S2020C ha annunciato il supporto per gli allora nuovi FPGA Xilinx VU2P UltraScale+, che offrono piattaforme di prototipazione FPGA singole, doppie e quadruple. Quindi, nel dicembre del 19, S2020C ha fatto seguito all'annuncio della sua famiglia di piattaforme di prototipazione Prodigy Logic Matrix ad alta densità con 2 FPGA per Logic Matrix, 8 Logic Matrix per singolo server rack (8 FPGA) e la connessione di più rack di server insieme. Le prime iterazioni di Logic Matrix sono state fornite con Xilinx VU64 FPGA (soprannominato il LX1) ai primi clienti che non vedevano l'ora della versione VU19P (soprannominata la LX2).

Ora, S2C sta intensificando il suo gioco Logic Matrix con il LX2, che aumenta la capacità del gate utilizzabile per la prototipazione del 60% in più rispetto alla versione VU440! Più porte utilizzabili per FPGA significano meno FPGA, meno interconnessioni FPGA e prestazioni più elevate per lo stesso progetto prototipo. Con una capacità di gate stimata di 392 milioni di gate per LX2, un server rack standard completamente popolato con 8 di LX2 consente una capacità di prototipazione stimata di oltre 3 miliardi di porte ASIC!

Figura 1: matrice logica Prodigy LX2

| Famiglia di matrici logiche Prodigy | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Porte ASIC stimate (M) | 240 | 392 |

| Numero di FPGA | 8 | 8 |

| Celle logiche di sistema (K) | 44,328 | 71,504 |

| Memoria FPGA (Mb) | 709 | 1,327.2 |

| Slice DSP | 23,040 | 30,720 |

| I/O utente esterno | 9,216 | 10,368 |

| Ricetrasmettitori SerDes | 384 GTH | 640 GT |

| Connettori Prodigy | 64 | 72 |

| Connettori PGT | 8 | 0 |

| Connettori ricetrasmettitori | 80 MSAS ciascuno con 4 GTH + 8 IO | 160 MCIO ciascuno con 4 GTY + 8 IO |

| Prestazioni SerDes | 16 Gbps | 28 Gbps |

figura 2: Famiglia di matrici logiche

L'interconnessione flessibile e ad alta velocità è fondamentale per la prototipazione FPGA ad alta densità e Logic Matrix supporta una strategia di interconnessione gerarchica a 3 livelli: Ponte Corto per l'interconnessione tra FPGA adiacenti; Syslink per l'interconnessione del cavo FPGA a larghezza di banda elevata e TransLink per interconnessione SerDes FPGA a lunga distanza su cavi MCIO. Per semplificare l'interconnessione FPGA e massimizzare il valore di TransLink, il flusso di partizionamento di S2C supporta il nuovo High-Speed Transceiver Pin Multiplexing (HSTPM) di Xilinx, che semplifica il trasferimento del segnale accurato al ciclo, il multiplexing dei pin e la connettività SerDes FPGA a bassa latenza.

Per ridurre al minimo il tempo necessario per la prototipazione e massimizzare la produttività della prototipazione, gli altri strumenti di produttività per la prototipazione di S2C sono progettati pensando a Logic Matrix, tra cui Runtime Player Pro software e strumenti di prototipazione S2C aggiuntivi, inclusi Protoponte, MDM Proe S2C IP pronto per il prototipo.

Runtime Player Pro il software è incluso con LX2, fornendo funzionalità utili come la gestione avanzata dell'orologio, l'autotest integrato, il rilevamento automatico della scheda, la programmazione della tensione I/O, il download di più FPGA e il monitoraggio e la gestione remoti del sistema. È incluso anche AXEVision, uno strumento di debug AXI-over-Ethernet integrato per semplificare il debug remoto dei progetti relativi ad AXI.

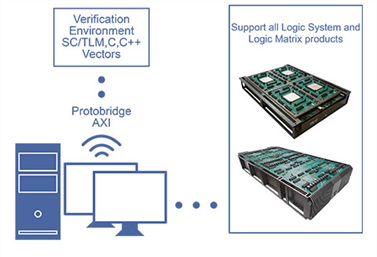

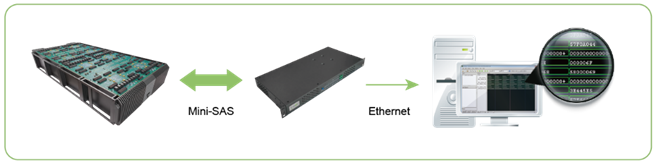

Protoponte supporta trasferimenti di dati ad alta velocità (fino a 1 GB/s) tra il PC host e il LX2 – consentire il trasferimento di grandi quantità di transazioni modellate da software, flussi video o altri stimoli di test per la convalida del sistema.

Figura 3: ProtoBridge

MDM Pro offre debug della traccia profonda con trigger incrociati per un massimo di otto FPGA, visualizzazione della traccia del segnale multi-FPGA da un'unica finestra di visualizzazione, 64 GB di memoria esterna della forma d'onda della traccia, velocità di campionamento della traccia fino a 125 MHz e supporta i linguaggi della macchina a stati di trigger per acquisizioni di tracce complesse requisiti.

Figura 4: MDM Pro

S2C offre anche una ricca libreria di IP pronto per il prototipo per l' LX2 – Schede figlie plug-and-play – che velocizzano la creazione dell'ambiente di prototipazione attorno al prototipo FPGA.

Figura 5: Schede IP figlie pronte per il prototipo

Matrice logica prodigio LX2 è ora disponibile. Per ulteriori informazioni, contattare il rappresentante di vendita S2C locale o visitare www.s2ceda.com.

Condividi questo post tramite: Fonte: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Aggiungi su

- ha annunciato

- Annuncio

- in giro

- ASIC

- disponibilità

- Miliardo

- tavola

- cavi

- Ultra-Grande

- veloce

- Connettività

- Clienti

- dati

- consegna

- Design

- rivelazione

- distanza

- Presto

- Ambiente

- famiglia

- Caratteristiche

- Fico

- Nome

- flusso

- FPGA

- gioco

- Gates

- globali

- HTTPS

- Compreso

- informazioni

- Intel

- IP

- Le

- Le Lingue

- grandi

- con i più recenti

- Biblioteca

- locale

- gestione

- Matrice

- milione

- monitoraggio

- offerta

- Offerte

- Altro

- PC

- performance

- piattaforma

- Piattaforme

- Pro

- della produttività

- Strumenti di produttività

- Programmazione

- prototipazione

- Requisiti

- vendite

- una scale-up

- Software

- Soluzioni

- Regione / Stato

- stimolo

- conservazione

- Strategia

- flussi

- supporto

- supporti

- sistema

- test

- Le transazioni

- APPREZZIAMO

- Video

- aspettare

- OMS