Un nuovo documento tecnico intitolato "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing" è stato pubblicato dai ricercatori dell'Università di Stoccarda, UC Berkeley, Indian Institute of Technology Kanpur e TU Munich, con il finanziamento della German Research Foundation .

Astratto

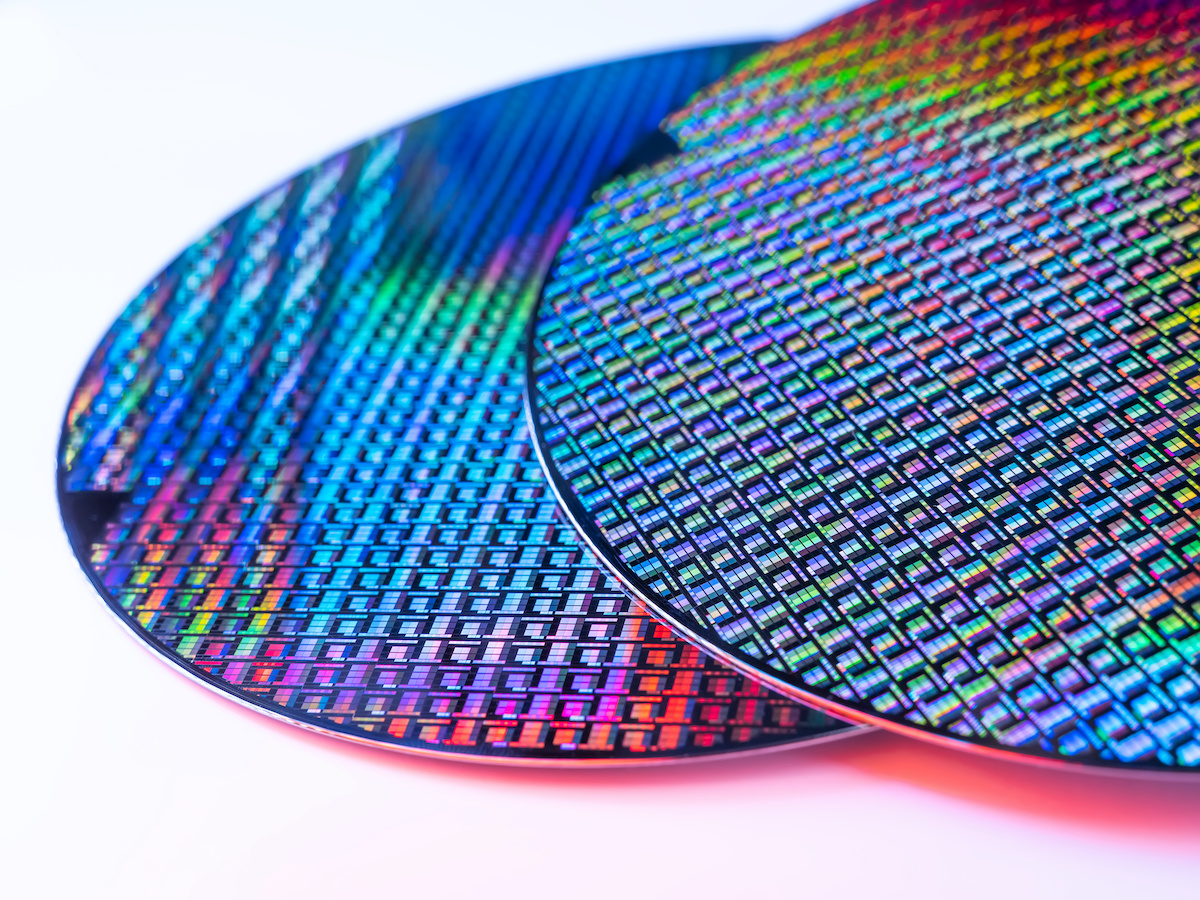

“In questo documento, proponiamo una progettazione non tradizionale di circuiti logici dinamici utilizzando FET di silicio completamente impoverito su isolante (FDSOI). FDSOI FET consente la tensione di soglia (Vt ) per essere regolabile (vale a dire, stati Vt basso e Vt alto) utilizzando la polarizzazione back gate. Il nostro progetto utilizza le porte anteriore e posteriore di un FET FDSOI come terminali di ingresso e propone le porte logiche dinamiche (come; NAND, NOR, AND, OR, XOR e XNOR) e circuiti (come; half adder e full adder). Richiede meno transistor per costruire porte logiche dinamiche e raggiunge prestazioni elevate con una bassa dissipazione di potenza rispetto ai progetti logici dinamici convenzionali. Il modello industriale compatto di FDSOI FET (BSIM-IMG) è stato utilizzato per simulare porte logiche dinamiche ed è completamente calibrato per riprodurre i dati del nodo della tecnologia FDSOI FET a 14 nm. La calibrazione viene eseguita sia per le caratteristiche elettriche che per le variazioni di processo. I risultati della simulazione mostrano un miglioramento medio del numero di transistor, del ritardo di propagazione, della potenza e del prodotto del ritardo di potenza rispettivamente del 23.43%, 57.16%, 47.05% e 77.29%, rispetto ai progetti convenzionali. Inoltre, il nostro progetto riduce l'effetto di condivisione della carica, che influisce sulla guidabilità delle porte logiche dinamiche. Inoltre, abbiamo analizzato in dettaglio l'impatto delle variazioni di processo, tensione di alimentazione e capacità di carico sul ritardo di propagazione della famiglia logica dinamica. I risultati mostrano che queste variazioni hanno un impatto minore sul ritardo di propagazione delle porte logiche dinamiche basate su FDSOI proposte rispetto alle porte logiche dinamiche convenzionali».

Trovare il documento tecnico qui. Pubblicato aprile 2023.

S. Kumar, S. Chatterjee, CK Dabhi, YS Chauhan e H. Amrouch, "Non-Traditional Design of Dynamic Logics using FDSOI for Ultra-Efficient Computing", in IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, doi: 10.1109/JXCDC.2023.3269141. Apri accessos.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoAiStream. Intelligenza dei dati Web3. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Acquista e vendi azioni in società PRE-IPO con PREIPO®. Accedi qui.

- Fonte: https://semiengineering.com/non-traditional-design-of-dynamic-logic-gates-and-circuits-with-fdsoi-fets/

- :ha

- :È

- 10

- 2023

- 23

- 77

- a

- Realizza

- aggiunta

- regolabile

- consente

- an

- ed

- Aprile

- AS

- At

- media

- precedente

- BE

- stato

- Berkeley

- pregiudizio

- entrambi

- costruire

- by

- caratteristiche

- carica

- rispetto

- informatica

- convenzionale

- dati

- ritardo

- Design

- disegni

- dettaglio

- dispositivi

- dinamico

- e

- effetto

- famiglia

- FET

- meno

- Nel

- Fondazione

- anteriore

- pieno

- completamente

- finanziamento

- ulteriormente

- Gates

- Tedesco

- Metà

- Avere

- Alta

- HTTPS

- i

- IEEE

- Impact

- miglioramento

- in

- indiano

- industriale

- ingresso

- Istituto

- IT

- rivista

- piace

- caricare

- logica

- Basso

- minore

- modello

- Monaco

- New

- nodo

- of

- on

- or

- nostro

- Carta

- performance

- Platone

- Platone Data Intelligence

- PlatoneDati

- energia

- processi

- Prodotto

- offre

- proposto

- propone

- pubblicato

- riduce

- richiede

- riparazioni

- ricercatori

- rispettivamente

- Risultati

- s

- compartecipazione

- mostrare attraverso le sue creazioni

- Silicio

- simulazione

- stati

- fornire

- Consulenza

- Tecnologia

- che

- I

- Strumenti Bowman per analizzare le seguenti finiture:

- questo

- soglia

- titolato

- a

- Università

- utilizzato

- utilizzando

- utilizza

- Tensione

- Prima

- we

- quale

- con

- zefiro