La vecchia frase che la cura è peggiore della malattia è appropriata quando si discute di MBIST per grandi SOC in cui l'esecuzione di molti test MBIST in parallelo può superare le capacità della rete di distribuzione dell'energia (PDN). Memory Built-In Self-Test (MBIST) di solito viene eseguito automaticamente durante gli eventi di accensione. A causa del desiderio di accelerare i tempi di test e avvio del chip, questi test vengono spesso eseguiti in parallelo. Il problema è che possono facilmente produrre un'attività di commutazione di un ordine di grandezza superiore ai livelli riscontrati durante il normale funzionamento del chip. In effetti, questi livelli di attività di commutazione più elevati non solo possono causare un calo dell'alimentazione che influisce sui risultati del test, ma anche l'elevato calore generato può danneggiare i chip. Questi effetti possono portare a un binning errato o a guasti diretti e latenti di eventi.

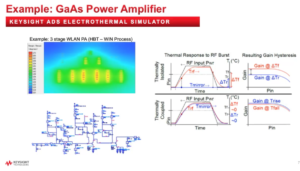

La soluzione è simulare l'attività MBIST per prevedere il carico sul PDN e i relativi effetti termici. Con i risultati della simulazione in mano, i progettisti possono decidere correttamente quanti e quali blocchi di memoria possono essere testati in parallelo. Tuttavia, questo non è sempre fattibile in SOC di grandi dimensioni con molti blocchi di memoria perché i tempi di simulazione possono essere proibitivi. Con il livello di gate e una simulazione RTL ancora meno accurata potrebbe non essere possibile eseguire abbastanza cicli per ottenere le informazioni necessarie.

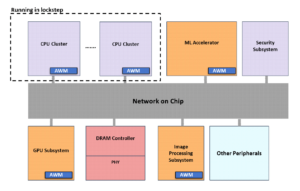

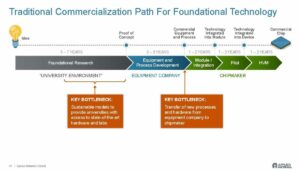

In un white paper intitolato "Analisi delle implicazioni di potenza dell'utilizzo di MBIST", Siemens EDA esamina come i progettisti possono eseguire una simulazione sufficiente per prendere decisioni informate sulla strategia di test prima del tapeout. Siemens ha lavorato con ARM su uno dei loro chip di prova per creare un test case in cui potevano applicare l'emulazione hardware con le app DFT e Power per l'emulatore hardware Siemens Veloce. Innanzitutto, l'app Veloce DFT viene utilizzata per generare l'attività interna durante l'emulazione MBIST. L'app utilizza lo Standard Test Interface Language (STIL) e produce file di output standard del settore.

L'app Veloce Power prende le informazioni sull'attività dalle esecuzioni MBIST per generare forme d'onda, profili di potenza e mappe di calore che possono indicare quando si verificano picchi di potenza superiori ai limiti specificati. Con questo test di informazioni gli ingegneri possono prendere decisioni informate sul sequenziamento di MBIST.

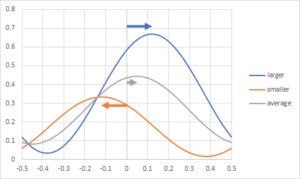

Il test case ARM descritto nel white paper Siemens contiene 176 milioni di gate. Siemens ha utilizzato un sistema Veloce con 6 schede Veloce Strato per questo test case. L'esecuzione dell'emulatore Veloce ha richiesto solo 26 ore, che è 15,600 volte più veloce della simulazione a livello di gate. Un altro vantaggio del flusso Veloce è che le informazioni sull'attività vengono trasmesse in streaming dall'app Power agli utensili elettrici nel flusso, risparmiando spazio e tempo su disco. I risultati del test case hanno mostrato diversi picchi di alimentazione che hanno violato le specifiche di progettazione SOC. L'output dell'app Veloce Power mostra i livelli di potenza totali attraverso la simulazione insieme ai contributi di potenza separati per l'orologio, la logica combinatoria e la memoria. Allo stesso modo, ci sono informazioni su dove sul dado viene utilizzato il potere. Queste informazioni consentono di determinare facilmente dove ci sono problemi.

Trovare problemi come questi richiede l'esecuzione di milioni o miliardi di cicli di clock. Le limitazioni dei simulatori software rendono proibitivo eseguire le analisi necessarie. L'emulazione offre una strada unica per esaminare da vicino gli impatti sull'alimentazione di MBIST e altre operazioni di test molto prima del silicio. Il white paper Siemens offre informazioni sul metodo di alimentazione utilizzato in un vero e proprio banco di prova. Il white paper è disponibile per il download per la lettura sul sito Web Siemens.

Condividi questo post tramite: Fonte: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Chi siamo

- .

- App

- applicazioni

- ARM

- disponibile

- essendo

- Causare

- patata fritta

- Chips

- Orologio

- contiene

- potuto

- cura

- Design

- Malattia

- durante

- facilmente

- Ingegneri

- Evento

- eventi

- più veloce

- Nome

- flusso

- essere trovato

- Gates

- generare

- Hardware

- Alta

- Come

- HTTPS

- industria

- informazioni

- IT

- Lingua

- grandi

- portare

- Livello

- livelli

- caricare

- Lunghi

- Maps

- milione

- milioni

- di applicazione

- Rete

- Offerte

- Operazioni

- minimo

- Altro

- Carta

- energia

- Problema

- Profili

- Lettura

- Risultati

- Correre

- running

- risparmio

- Siemens

- simulazione

- Software

- lo spazio

- velocità

- Strategia

- streaming

- fornire

- sistema

- test

- Testing

- test

- termico

- Attraverso

- tempo

- strumenti

- unico

- generalmente

- Sito web

- white paper

- lavorato