L'incisione al plasma è forse il processo più essenziale nella produzione di semiconduttori e forse la più complessa di tutte le operazioni favolose accanto alla fotolitografia. Quasi la metà di tutti i passaggi favolosi si basa su un plasma, un gas ionizzato energetico, per svolgere il proprio lavoro.

Nonostante transistor e celle di memoria sempre più ridotti, gli ingegneri continuano a fornire processi di incisione affidabili.

"Per creare in modo sostenibile chip con precisione a livello di nanoscala e la giusta struttura dei costi, i produttori di apparecchiature per wafer fab devono spingere i confini della fisica del plasma, dell'ingegneria dei materiali e della scienza dei dati per fornire le soluzioni di apparecchiature necessarie", ha affermato Thomas Bondur, vicepresidente aziendale per Marketing del gruppo di prodotti Etch a Ricerca Lam. Da nessuna parte questo è più evidente che nell'incisione al plasma, che funziona di pari passo con la litografia per creare caratteristiche precise e ripetibili sui wafer.

Questo rapporto esamina i passaggi chiave dell'incisione in 3D NAND, DRAM, FET nanosheet e interconnessioni, con uno sguardo in avanti ai dispositivi 2D e all'elaborazione back-end a basso budget. L'industria sta anche perseguendo prodotti chimici di incisione più sostenibili per ridurre la CO equivalente2 emissioni dai suoi stabilimenti.

Per molti produttori di utensili, la modellazione del processo svolge un ruolo fondamentale nello sviluppo del processo di incisione. L'obiettivo è abbreviare il time-to-market riducendo al contempo i costi di wafer e maschere.

"L'ottimizzazione del processo di Etch su alcuni dei passaggi più difficili può richiedere un anno o più per essere completata", ha affermato Barrett Finch, direttore marketing senior di Lam Research. "Recentemente abbiamo completato un lavoro di simulazione di processo in tre settimane che avrebbe dovuto richiedere tre mesi utilizzando test e sviluppo tipici basati su silicio".

Questo può ammontare a centinaia di migliaia, o addirittura milioni di dollari, solo per i costi di maschere e wafer per un produttore di dispositivi.

Nozioni di base sull'incisione

Il processo di incisione funziona di pari passo con la litografia. L'incisione tipicamente è preceduta dalla deposizione di un film (mediante epitassia, deposizione chimica o fisica da vapore, ecc.). Tipicamente, un CVD il film è rivestito con fotoresistenza e poi esposto attraverso un motivo reticolo (maschera) usando litografia ottica (248 nm o 193 nm UV, 13.5 nm EUV). Lo sviluppo di resistenza rivela quindi il modello. In una camera di attacco al plasma a singolo wafer, tipicamente i prodotti chimici e gli ioni di attacco bombardano e rimuovono il film CVD dove manca il fotoresist (in tono positivo resist). Dopo l'incisione, resistere all'incenerimento, alla pulizia chimica a umido e/o all'incisione a umido per rimuovere i residui.

I processi di incisione al plasma possono essere approssimativamente raggruppati come incisioni dielettriche, al silicio o conduttrici. I dielettrici come il biossido di silicio e il nitruro di silicio vengono incisi meglio utilizzando gas fluorurati, mentre gli strati di silicio e metallo reagiscono meglio con le sostanze chimiche del cloro. Esistono essenzialmente tre modalità di incisione a secco: incisione con ioni reattivi, incisione al plasma e incisione sputter (fascio ionico). I processi di incisione riguardano le complesse interazioni tra i reagenti chimici, il plasma e i materiali dei wafer. Quando la polarizzazione RF viene applicata a un gas reattivo, gli elettroni e gli ioni caricati positivamente bombardano il wafer per rimuovere fisicamente (attacco) il materiale mentre le specie chimiche e i radicali liberi reagiscono con il materiale esposto per formare sottoprodotti volatili. L'incisione può essere isotropica (reagisce in modo uguale verticalmente e orizzontalmente), anisotropica (solo verticale) o una via di mezzo.

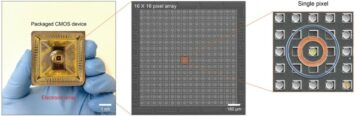

Fig. 1: La transizione da finFET a GAA determina requisiti critici di incisione selettiva isotropica. Fonte: Lam Research

Le metriche a cui gli ingegneri di incisione si preoccupano maggiormente sono la velocità di incisione, il controllo del profilo, l'uniformità (attraverso il wafer) e la selettività di incisione, perché incidono sulla resa e sulla produttività. La selettività di incisione è semplicemente il rapporto di rimozione del materiale che si desidera incidere rispetto al suo sottostrato, ad esempio SiO2 sul silicio. Durante l'attacco, è anche vantaggioso non rimuovere troppo fotoresist. Ma quando questo è il caso, spesso il modello viene trasferito su una maschera dura (biossido di silicio, nitruro di silicio, SiOC, TiN) prima di essere trasferito al film sottostante.

Le specifiche di selettività variano da 2:1 fino a 1,000:1 (attacco altamente selettivo). Con ogni nuovo nodo, queste specifiche si restringono. "Con l'EUV ad alto NA che inizia a sostituire l'EUV normale entro i prossimi quattro anni, l'attenzione è molto più bassa, quindi non è più possibile esporre fotoresist spesso - e per spessore intendo 30 nanometri", ha affermato Philippe Bézard, ingegnere R&S di dry etch presso imec. “Ma devi ancora modellare lo stesso spessore del film di seguito. Quindi ora stai chiedendo una selettività molto più elevata, nel senso che invece di 2:1 dobbiamo raggiungere qualcosa di più simile a 10:1, che è un improvviso miglioramento della selettività da 4 a 5 volte".

Dal proof of concept (POC) alla produzione ad alto volume (HVM)

Bézard descrive tre fasi di sviluppo del processo di incisione:

- Determinazione di quale incisore, gas, strati di assistenza, ecc., sono necessari per eseguire l'attacco;

- Dimostrazione delle prestazioni nella rimozione completa della pellicola entro le specifiche con uniformità di processo su un wafer e

- Determinare come il processo può essere ripetuto su migliaia di wafer in HVM con resa elevata e poca deriva.

In genere, ingegneri esperti di etch e integrazione gestiscono le prime due fasi di sviluppo. La terza fase potrebbe nuovamente utilizzare le competenze ingegneristiche, ma l'apprendimento automatico potrebbe aiutare.

"L'apprendimento automatico e l'analisi dei dati in generale sono utili solo nella terza fase", ha affermato. “È molto potente perché ha accesso a un'enorme quantità di dati e può dare un senso a un milione di piccole cose semplici che interagiscono tutte. Quindi per un cervello umano cercare di capirlo è molto difficile, ma è più gestibile per un programma per computer. Ma nei casi in cui si dispone di una nuova applicazione, di nuovo materiale da incidere o di una nuova integrazione, non mostra alcun miglioramento rispetto agli umani".

L'uso del machine learning riguarda anche i costi di produzione perché nella fase tre vengono utilizzati migliaia di wafer, almeno un ordine di grandezza maggiore rispetto a quelli utilizzati nelle fasi uno e due.

Barrett Finch, direttore senior dell'Etch Product Group presso Lam Research, descrive la ricerca di nuovi processi come l'acquisizione di una prova di concetto da un flusso e un layout di processo nominali e lo sviluppo di uno o più dispositivi funzionanti su un wafer. Questo POC viene quindi trasferito a un team di sviluppo prodotto nella fabbrica per aumentare il processo e migliorare la resa.

"La quantità di lavoro necessaria per trasformare una prova di concetto nominale in un prodotto redditizio praticabile è spesso sottovalutata, e questo crea un grande divario per la redditività", ha affermato Finch. "La modellazione della finestra di processo cerca di colmare questa lacuna introducendo favolose variazioni nelle prime fasi del percorso di ricerca e sviluppo". Suggerisce che i DOE virtuali e l'analisi basata su Monte Carlo su una serie di parametri di processo verifichino un POC simulando la variabilità prevista.

“La modellazione della finestra di processo può rispondere alla domanda: 'Quale CD o livello di variabilità devo mantenere per raggiungere le prestazioni e il rendimento minimi del dispositivo?' Abbiamo completato i test delle finestre di processo virtuali con oltre 1 milione di wafer virtuali in pochi giorni, il che sarebbe impossibile da realizzare nella vita reale", ha affermato.

Più parametri influenzano la velocità di incisione, il profilo e la selettività. Una chiave è la temperatura. “L'impatto degli effetti termici nella lavorazione dell'incisione è visto dai nostri clienti mentre controllano velocità di incisione, selettività e profili incisi. Tutti questi parametri possono influire sia sulla resa del dispositivo che sulla produttività della fabbrica", ha affermato Benjamin Vincent, senior manager per il processo dei semiconduttori e l'ingegneria dell'integrazione presso Lam Research. Sostiene che la simulazione può essere particolarmente utile quando una fase del processo ha più configurazioni possibili (lo spazio del processo è ampio) o quando i risultati a valle della fase sono altamente imprevedibili.

"Il processo di incisione si basa sulla temperatura superficiale del wafer, che dipende da diversi flussi di calore, tra cui conduzione termica, energie di impatto ionico, reazioni superficiali e flussi di calore radiativo del plasma", ha dichiarato Alex Guermouche, product marketing manager presso Esgee Technologies, a Società di ricerca Lam. “Di conseguenza, i modelli al plasma devono incorporare tutte queste caratteristiche fisiche per rappresentare con precisione i cambiamenti di temperatura sulla superficie del wafer. Il software di simulazione del processo può modellare una gamma di attributi di incisione, consentendoci di ottenere un risultato di incisione migliore più rapidamente e di accelerare la capacità del cliente di aumentare la produzione o ottimizzare la resa".

Tempistica precisa del processo di incisione

Con geometrie più strette e film più sottili, è necessario bilanciare la velocità di incisione con un grande controllo su altri parametri operativi.

"Con la riduzione delle regole di progettazione, molti processi di incisione si stanno spostando verso fasi di processo di incisione al plasma molto veloci che richiedono un controllo estremamente preciso di tutti gli input di reazione: potenza, pressione, chimica e temperatura", ha affermato Finch, osservando che esiste anche una tendenza verso l'ottimizzazione del plasma comportamento pulsante per generare un particolare rapporto ione-neutro, quindi spazzare via i sottoprodotti. "La modellazione avanzata di tali condizioni sarà fondamentale per consentire un ulteriore ridimensionamento del dispositivo".

I produttori di sistemi di incisione utilizzano da tempo software di modellazione per accelerare lo sviluppo del nodo successivo o aumentare i rendimenti. Questa non è una sorpresa, data l'assoluta complessità del processo e tutte le sue variabili.

"Semplicemente non c'è abbastanza tempo o abbastanza wafer per eseguire tutti i possibili esperimenti di processo durante lo sviluppo di tecnologie del nodo successivo", ha affermato Finch. "Il numero di combinazioni di impostazioni delle apparecchiature di incisione può raggiungere milioni, o addirittura miliardi, e lo sviluppo di wafer a forza bruta utilizzando tutte le possibilità di processo è semplicemente impossibile."

Naturalmente, tutti i buoni modelli vengono verificati su chip reali. "Un modello accurato dovrebbe essere predittivo e dovrebbe risolvere il problema mirato che un utente desidera risolvere", ha affermato Finch. “Ogni volta che viene raccomandata una modifica di processo o di progettazione sulla base di un lavoro di simulazione, i dati fab effettivi dovrebbero riflettere i risultati della raccomandazione. Nel nostro caso, siamo stati in grado di prevedere con precisione l'effetto delle modifiche al processo utilizzando risultati basati su modelli e risolvere rapidamente problemi di sviluppo tecnologico e di processo difficili".

I fornitori di strumenti stanno anche lavorando su processi di incisione avanzati per integrare più strettamente le linee e trasformare quello che una volta era un processo a livello di due maschere (due fasi di litografia) in uno per la semplificazione del processo e la riduzione dei costi.

"Invece di adattare l'hardware esistente per rendere il coltellino svizzero ancora più equipaggiato, le aziende stanno introducendo tecnologie specifiche per l'applicazione, come nuovi sistemi per affrontare i problemi da punta a punta", ha affermato Bézard. L'obiettivo è avvicinare due linee una di fronte all'altra, il che attualmente comporta una fase di modellazione delle linee seguita da una maschera di taglio. "Ciò che Applied Materials e altri stanno introducendo è un modo per incidere direttamente in direzione orizzontale". Tali processi possono anche allargarsi tramite fori.

Etch passaggi per FET nanosheet

L'attacco più critico interviene nanofoglio i flussi di processo includono l'attacco del cancello fittizio, l'attacco del pilastro anisotropico, l'attacco del distanziatore isotropo e la fase di rilascio del canale. [1] L'attacco del profilo attraverso strati alternati di silicio e SiGe è anisotropico e utilizza la chimica fluorurata. L'attacco del distanziatore interno (indentazione) e la fase di rilascio del canale sono ottimizzati per rimuovere SiGe con una perdita di silicio estremamente bassa.

La fase di rilascio del canale è fondamentale. "Il rilascio del nanosheet richiede una selettività estremamente elevata", ha affermato Bézard. “La maggior parte dei nanosheets sono silicio, poi silicio-germanio e silicio. Hai livelli alternati e devi rimuoverne uno senza modificare affatto l'altro. Alcune pubblicazioni hanno discusso l'esecuzione di un attacco SiGe in più passaggi per ridurre lo stress alla struttura indotto da un singolo passaggio di attacco.

Il passo successivo nel processo è la formazione di contatti autoallineati. “Qui quello che stiamo cercando di fare è fondamentalmente incidere il biossido di silicio e non toccare o incassare il nitruro di silicio. Le specifiche attuali sono, diciamo, 3 nm di recesso, ma le persone chiedono zero perdite ", ha affermato Bézard. “In questo caso non usiamo nemmeno la parola selettività. Parliamo solo di recesso – e zero recesso”.

3D NAND

Nel 3D NAND flash, il numero di livelli continua a crescere e richiede l'adozione di più livelli sovrapposti in futuro, creando infine stringhe verticali di dispositivi sovrapposti. "Inoltre, c'è molta spinta a ridimensionare il passo della linea di parola o il passo verticale/Z degli strati man mano che il numero di strati cresce per continuare ad aumentare la densità di bit", ha affermato Robert Clark, membro senior dello staff tecnico e direttore tecnologico presso TEL. "Dal punto di vista del processo, i processi di incisione e deposizione avranno bisogno di miglioramenti costanti per adattarsi ai rapporti di aspetto sempre più elevati a dimensioni critiche sempre più piccole che il continuo ridimensionamento richiede".

Clark ha descritto i cambiamenti futuri. “Guardando verso nodi avanzati di dispositivi di trappola di carica con più livelli, sarà necessaria la progettazione degli stack di gate per ottenere lunghezze di gate più brevi, più livelli per cella e una migliore efficienza di programmazione, potenzialmente attraverso l'adozione di materiali high-k. In futuro saranno probabilmente necessari anche canali a conduttività più elevata per sostituire i canali poli-Si", ha affermato.

Una delle incisioni più critiche nella NAND 3D comporta l'incisione profonda di circa 100 nm di fori attraverso pile multistrato di ossido-nitruro (più di 200 strati), che possono essere profonde fino a 10 µm. Bézard di Imec ha affermato che questa fase di incisione è particolarmente costosa.

"Abbiamo un fenomeno fisico che si verifica, chiamato effetto di carica differenziale", ha detto. “Nel plasma abbiamo elettroni, ioni e specie neutre per semplificare molto. Gli elettroni si muovono in ogni direzione, ma gli ioni vengono accelerati perpendicolarmente alla superficie. Quindi hai una carica positiva nella parte inferiore del buco e cariche negative nella parte superiore, e ottieni un campo elettrico che sta cercando di respingere gli ioni in arrivo.

Di conseguenza, sono necessari alti livelli di potenza per incidere completamente la trincea. "Stiamo cercando di sostenere da 30 a 50 gigawatt di potenza senza arco, quindi il mandrino deve essere estremamente ben lucidato e ben fabbricato", ha affermato.

Le incisioni profonde inducono anche sollecitazioni che devono essere ridotte al minimo, soprattutto perché la fabbricazione NAND a più livelli richiede successivamente assottigliamento del wafer, allineamento preciso e legame ibrido al livello successivo.

Altri processi

Non tutti i produttori di chip producono chip all'avanguardia che richiedono la litografia EUV. Molte fabbriche stanno estendendo i loro processi litografici e di incisione a 193 nm.

"Abbiamo un materiale SOC ad alta temperatura che abbiamo recentemente iniziato a introdurre, che estende la sua capacità di modellazione e può resistere a temperature più elevate, sia che venga utilizzato come sottostrato per uno strato CVD o maschera", ha affermato Brian Wilbur, direttore della diversificazione dei prodotti a semiconduttore presso Scienza del birraio.

BEOL per le linee metalliche più strette si prevede una drammatica transizione da schemi di integrazione a doppio damasco a deposizione sottrattiva e incisione di interconnessioni diverse dal rame. Qui, due metalli - rutenio e molibdeno - sono stati i più sviluppati. Tuttavia, è più probabile che il molibdeno si ossidi durante l'incisione, rendendolo più compatibile con gli schemi a doppio damasco. Il rutenio è un metallo nobile quindi non presenta gli stessi problemi di corrosione, ma è più costoso.

Anche le strutture dei dispositivi stanno diventando intolleranti errori di posizionamento dei bordi. Saranno necessari nuovi schemi per l'autoallineamento da strato a strato e tra vie e linee, secondo Clark di TEL. "Le prime implementazioni riguarderanno probabilmente cose come le linee di parole sepolte nella DRAM e gli strati metallici MOL a passo ridotto per la logica in cui sono necessarie una maggiore stabilità termica e una resistività inferiore o metalli senza rivestimento".

Sviluppi di nuova generazione

A lungo termine, l'industria passerà idealmente a processi back-end con budget termico inferiore (più vicino a 300°C che a 400°C) per integrare i dispositivi nei livelli di interconnessione back-end.

"L'industria ha una reale necessità di iniziare a costruire dispositivi in più livelli", ha affermato Clark di TEL. "Ciò significa che abbiamo bisogno di memoria e dispositivi logici costruiti all'interno del BEOL con budget termici BEOL".

Finora, i dispositivi realizzati utilizzando ossidi semiconduttori sembrano promettenti, sia per l'integrazione di dispositivi di memoria in un flusso BEOL logico, sia per la creazione di array CMOS in cima all'array di memoria nelle DRAM.

Un altro cambiamento sostanziale riguarda l'integrazione di materiali 2D, che le case di ricerca e i principali produttori di chip stanno già iniziando a testare. Si stanno prendendo in considerazione processi di incisione per materiali come il disolfuro di tungsteno o il disolfuro di molibdeno. I film sono costituiti da un monostrato di materiale, quindi lo sviluppo di processi favolosi per integrarli è estremamente impegnativo.

Sostenibilità

I produttori di chip e i fornitori di materiali stanno perseguendo prodotti chimici alternativi per ridurre le emissioni di carbonio. Nell'incisione, i principali colpevoli sono i gas fluorurati con un elevato potenziale di riscaldamento globale.

"Un motivo per cui hai PFOS (acido perfluorottano sulfonico), che è problematico, è perché la molecola è così stabile", ha detto Bézard di imec. "La luce o le reazioni chimiche nell'atmosfera non sono sufficienti per abbatterla".

Ha affermato che un certo numero di miscele di gas alternative con un contenuto di ossigeno più elevato si dissociano più facilmente e hanno un GWP inferiore. "Tuttavia, qualsiasi candidato deve fornire prestazioni altrettanto buone o addirittura superiori per iniziare."

Ma la sostenibilità non è particolarmente una sfida di incisione o deposito. È una sfida olistica del settore, dalla litografia al packaging, in cui l'impatto di un nuovo materiale influenza l'intera elaborazione del dispositivo.

Riferimento

1. K.Derbyshire, "Cosa c'è di diverso nei transistor di nuova generazione", Ingegneria dei semiconduttori, 20 ottobre 2022.

ARTICOLI cORRELATI

L'incisione altamente selettiva viene lanciata per i chip di nuova generazione

La produzione di strutture 3D richiederà un controllo a livello atomico di ciò che viene rimosso e ciò che rimane su un wafer.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoAiStream. Intelligenza dei dati Web3. Conoscenza amplificata. Accedi qui.

- Coniare il futuro con Adryenn Ashley. Accedi qui.

- Acquista e vendi azioni in società PRE-IPO con PREIPO®. Accedi qui.

- Fonte: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :ha

- :È

- :non

- :Dove

- $ SU

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- Materiali 2D

- 30

- 3d

- 50

- a

- capacità

- capace

- Chi siamo

- accelerare

- accelerata

- accesso

- ospitare

- realizzare

- Secondo

- preciso

- con precisione

- operanti in

- presenti

- indirizzo

- Adozione

- Avanzate

- vantaggioso

- influenzare

- ancora

- puntare

- alex

- Tutti

- Consentire

- già

- anche

- alternativa

- quantità

- an

- .

- ed

- Un altro

- rispondere

- in qualsiasi

- apparire

- Applicazioni

- specifico dell'applicazione

- applicato

- SONO

- Army

- Italia

- AS

- aspetto

- assistere

- At

- Atmosfera

- gli attributi

- lontano

- Back-end

- Equilibrio

- basato

- fondamentalmente

- BE

- Larghezza

- perché

- diventando

- stato

- prima

- Inizio

- essendo

- sotto

- benzoino

- MIGLIORE

- Meglio

- fra

- pregiudizio

- Big

- miliardi

- Po

- entrambi

- Parte inferiore

- confini

- Cervello

- Rompere

- Brian

- forza bruta

- budget limitato.

- Per i bilanci

- Costruzione

- costruito

- ma

- by

- detto

- Materiale

- candidato

- carbonio

- le emissioni di carbonio

- che

- Custodie

- casi

- CD

- Celle

- Challenge

- impegnativo

- Telecamera climatica

- il cambiamento

- Modifiche

- canale

- canali

- carica

- carico

- oneri

- ricarica

- chimico

- chimico

- chimica

- Chips

- Pulizia

- Chiudi

- strettamente

- più vicino

- combinazioni

- Aziende

- azienda

- compatibile

- completamento di una

- Completato

- complesso

- complessità

- computer

- concetto

- condizioni

- conduttività

- conduttore

- considerato

- costante

- contatti

- contenuto

- continua

- continua

- continua

- di controllo

- Rame

- Aziende

- corrosione

- Costo

- riduzione dei costi

- Costi

- potuto

- corso

- creare

- crea

- Creazione

- critico

- Corrente

- Attualmente

- Clienti

- taglio

- dati

- analisi dei dati

- scienza dei dati

- Giorni

- deep

- consegnare

- densità

- dipende

- descritta

- Design

- sviluppato

- in via di sviluppo

- Mercato

- dispositivo

- dispositivi

- diverso

- difficile

- dimensioni

- direzione

- direttamente

- Direttore

- discusso

- diversificazione

- do

- effettua

- dollari

- giù

- drammaticamente

- guidare

- asciugare

- durante

- ogni

- Presto

- facilmente

- effetto

- effetti

- efficienza

- o

- Elettrico

- elettroni

- emissioni

- consentendo

- ingegnere

- Ingegneria

- Ingegneri

- abbastanza

- Allo stesso modo

- usate

- attrezzato

- Equivalente

- particolarmente

- essential

- essenzialmente

- eccetera

- Anche

- alla fine

- Ogni

- esigente

- esamina

- eseguire

- esistente

- previsto

- costoso

- esperimenti

- competenza

- esposto

- estendendo

- estremamente

- di fronte

- lontano

- FAST

- più veloce

- Caratteristiche

- pochi

- campo

- figura

- Film

- attraverso

- Nome

- Cromatografia

- flusso

- flussi

- Focus

- seguito

- i seguenti

- Nel

- forza

- modulo

- formazione

- Avanti

- quattro

- Gratis

- da

- completamente

- ulteriormente

- futuro

- divario

- GAS

- Generale

- generare

- ottenere

- dato

- globali

- il riscaldamento globale

- scopo

- buono

- grande

- Gruppo

- Crescere

- cresce

- Metà

- maniglia

- Hard

- Hardware

- Avere

- he

- utile

- qui

- Alta

- Ad alto rendimento

- superiore

- vivamente

- Foro

- Fori

- olistica

- Orizzontale

- case

- Come

- Tuttavia

- HTTPS

- umano

- Gli esseri umani

- centinaia

- IBRIDO

- i

- Impact

- impossibile

- competenze

- migliorata

- miglioramento

- in

- includere

- Compreso

- In arrivo

- incorporare

- crescente

- industria

- Ingressi

- esempio

- invece

- integrare

- Integrazione

- integrazione

- si interagisce

- interazioni

- interconnessioni

- ai miglioramenti

- l'introduzione di

- sicurezza

- IT

- SUO

- jpg

- ad appena

- Le

- Lam

- grandi

- superiore, se assunto singolarmente.

- strato

- galline ovaiole

- disposizione

- principale

- apprendimento

- meno

- Livello

- livelli

- Vita

- piace

- probabile

- linea

- Linee

- LITONE

- piccolo

- logica

- più a lungo

- Guarda

- spento

- lotto

- Basso

- macchina

- machine learning

- fatto

- Principale

- mantenere

- make

- Makers

- Fare

- direttore

- manufatto

- Costruttore

- consigliato per la

- molti

- Rappresentanza

- Marketing

- Direttore Marketing

- mask

- materiale

- Materiale

- max-width

- Maggio..

- significare

- si intende

- membro

- Memorie

- metallo

- metalli

- Metrica

- forza

- milione

- milioni

- ordine

- mancante

- modello

- modellismo

- modelli

- modalità di

- MOL

- molecola

- mese

- Scopri di più

- maggior parte

- cambiano

- in movimento

- molti

- multiplo

- quasi

- Bisogno

- di applicazione

- esigenze

- negativo.

- Neutres

- New

- GENERAZIONE

- no

- Nobile

- nodo

- nodi

- adesso

- numero

- ottobre

- of

- di frequente

- on

- una volta

- ONE

- esclusivamente

- operativo

- Operazioni

- ottimizzazione

- OTTIMIZZA

- ottimizzati

- or

- minimo

- Altro

- Altri

- nostro

- su

- ancora

- Oxygen

- imballaggio

- parametri

- particolare

- particolarmente

- Cartamodello

- Persone

- eseguire

- performance

- esecuzione

- Forse

- prospettiva

- fase

- fenomeno

- Philippe

- Fisico

- Fisicamente

- Fisica

- Pilastro

- Intonazione

- centrale

- Plasma

- Platone

- Platone Data Intelligence

- PlatoneDati

- gioca

- PoC

- positivo

- possibilità

- possibile

- forse

- potenziale

- potenzialmente

- energia

- potente

- bisogno

- Precisione

- predire

- Presidente

- pressione

- Problema

- problemi

- processi

- i processi

- lavorazione

- produrre

- Prodotto

- sviluppo del prodotto

- Produzione

- della produttività

- Prodotti

- Profilo

- Profili

- redditività

- Programma

- Programmazione

- promettente

- prova

- prova del concetto

- pubblicazioni

- Spingi

- domanda

- rapidamente

- R&D

- Rampa

- gamma

- tasso

- rapporto

- raggiungere

- Reagire

- reazione

- reazioni

- di rose

- vita reale

- ragione

- recentemente

- Consigli

- raccomandato

- ridurre

- riducendo

- riduzione

- riflettere

- Basic

- rilasciare

- affidabile

- fare affidamento

- rimozione

- rimuovere

- rimosso

- rimozione

- ripetibile

- ripetuto

- sostituire

- rapporto

- richiedere

- necessario

- Requisiti

- richiede

- riparazioni

- colpevole

- Risultati

- Rivela

- destra

- ROBERT

- Ruolo

- rotoli

- approssimativamente

- norme

- Correre

- Suddetto

- stesso

- dire

- Scala

- scala

- schemi

- Scienze

- cerca

- visto

- selettivo

- semiconduttore

- anziano

- senso

- regolazione

- alcuni

- spostamento

- dovrebbero

- Silicio

- Un'espansione

- semplificare

- semplicemente

- simulazione

- singolo

- qualificato

- piccole

- So

- Software

- Soluzioni

- RISOLVERE

- alcuni

- da qualche parte

- Fonte

- lo spazio

- specifico

- Specifiche tecniche

- occhiali

- velocità

- Stabilità

- stabile

- impilato

- Stacks

- STAFF

- tappe

- inizia a

- iniziato

- step

- Passi

- Ancora

- stress

- La struttura

- Successivamente

- sostanziale

- tale

- improvviso

- sufficiente

- suggerisce

- fornitori

- superficie

- sorpresa

- Sostenibilità

- sostenibile

- Sweep

- svizzero

- SISTEMI DI TRATTAMENTO

- Fai

- presa

- Parlare

- mirata

- team

- Consulenza

- Tecnologie

- Tecnologia

- Sviluppo tecnologico

- termine

- test

- Testing

- test

- di

- che

- I

- Il futuro

- loro

- Li

- poi

- Là.

- termico

- Strumenti Bowman per analizzare le seguenti finiture:

- di

- cose

- Terza

- questo

- a fondo

- migliaia

- tre

- Attraverso

- fila

- stretto

- tempo

- sincronizzazione

- a

- insieme

- tonnellata

- TONE

- pure

- top

- toccare

- verso

- trasferito

- Trasformare

- transizione

- Trend

- prova

- seconda

- tipico

- tipicamente

- sottostante

- imprevedibile

- su

- verso l'alto

- us

- uso

- utilizzato

- Utente

- utilizzando

- utilizzare

- verificato

- verticale

- verticalmente

- molto

- via

- vitale

- Vicepresidente

- vincent

- virtuale

- volatile

- volere

- vuole

- Prima

- Modo..

- we

- Settimane

- WELL

- Che

- quando

- se

- quale

- while

- tutto

- perché

- volere

- con

- entro

- senza

- Word

- Lavora

- lavoro

- lavori

- sarebbe

- anno

- anni

- dare la precedenza

- cedevole

- i rendimenti

- Tu

- zefiro

- zero