Lo stress termico è un problema ben noto nel packaging avanzato, insieme alle sfide dello stress meccanico. Entrambi sono esacerbati dall'integrazione eterogenea, che spesso richiede la miscelazione di materiali con coefficienti di dilatazione termica (CTE) incompatibili.

Gli effetti si stanno già manifestando e probabilmente peggioreranno solo con l'aumentare della densità dei pacchetti oltre i 1,000 urti per chip.

“Combina metalli che hanno un CTE relativamente alto, poi hai polimeri che hanno una rigidità CTE ancora maggiore, e poi hai dielettrici che hanno un CTE estremamente basso. Una volta messo tutto insieme, lo stress è inevitabile ", ha affermato Mario Gonzalez, direttore scientifico e responsabile della ricerca e sviluppo per la modellazione e la caratterizzazione meccanica e termica presso imec.

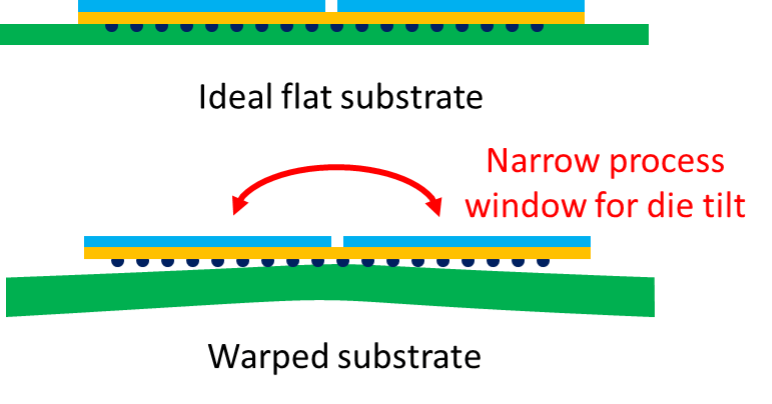

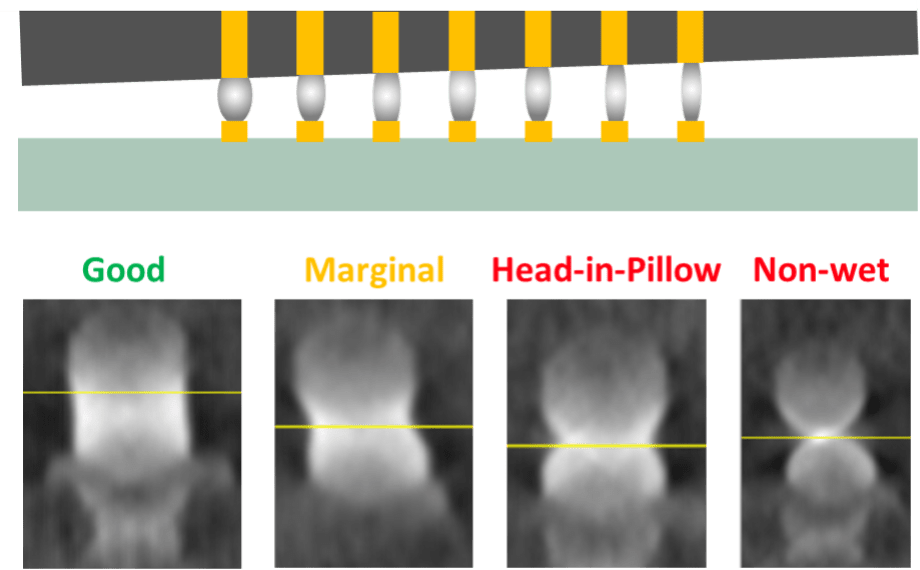

Tale stress si traduce spesso in una significativa deformazione o inclinazione dello stampo, che a sua volta porta a condizioni che diminuiscono l'affidabilità. "Hai a che fare con diverse tecnologie di substrati con più conteggi di strati", ha affermato Chip Greely, vicepresidente dell'ingegneria presso Industrie Promex. “I diversi spessori del nucleo nei substrati, in particolare, iniziano a creare molti problemi meccanici classici, inclusa la deformazione, che è diventata un punto dolente per alcuni dei giocatori più grandi. Chiediamo a molti dei nostri clienti che dispongono di un modulo multi-chip di integrazione eterogenea system-in-package, di fornire i dati del moiré ombra dei loro substrati in modo da poter vedere il modo in cui la sua deformazione cambia rispetto alla temperatura di riflusso e trovare idealmente la sua punto di riflessione”.

Questo ceppo ha vari effetti negativi, sperimentati su molte scale dimensionali, secondo Gilad Barak, vicepresidente delle nuove tecnologie avanzate presso Nova. "Spesso, la flessione e la torsione delle caratteristiche a livello di nanostruttura derivano dallo stress integrato che è stato creato, come si trova in alcuni DRAM e nanosheet logici front-end", ha affermato. “Un altro esempio riguarda le aree su scala micron in cui la deformazione indotta impedisce la fabbricazione di strutture semiconduttrici di fascia alta, come è tipico nelle 'zone di esclusione' intorno alle vie passanti in silicio (TSV). Infine, gli impatti su larga scala della deformazione indotta possono causare l'incurvamento del wafer, complicando notevolmente la manipolazione e la fabbricazione del wafer, con il rischio di fratturare il wafer stesso. L'incurvamento del wafer è particolarmente evidente durante la deposizione di spessi strati dielettrici, come è comune durante la fabbricazione di dispositivi NAND 3D.

La buona notizia è che l'industria è molto consapevole di questi e dei problemi associati. La cattiva notizia è che è ancora a corto di soluzioni, anche se ci sono molti approcci attualmente in fase di esplorazione.

"Esistono varie metodologie per ridurre la deformazione, ma nessuna di esse è completamente efficace e comportano sempre dei compromessi", ha affermato Frank Chen, direttore delle applicazioni e della gestione dei prodotti presso Bruker Nanosuperfici e metrologia. “I problemi non sono isolati da una ristretta selezione di applicazioni. Ogni volta che attacchi una fustella a un altro substrato, avrai questi problemi.”

Tutto ciò significa che l'ispezione e la metrologia devono continuare a svolgere ruoli critici. Anche altri problemi, come i punti caldi, possono essere esacerbati quando più chip vengono combinati in pacchetti eterogenei.

"Durante il test, vari chip si riscaldano in tempi e temperature diverse, creando possibili punti caldi che devono essere opportunamente raffreddati", ha affermato Andrei Berar, senior director per Test Business Development presso Amkor. "Oltre a creare controller termici attivi specifici, corrispondenti all'area di diversi chip, ci sono sforzi significativi per sviluppare controller termici adattivi in grado di 'anticipare' i punti caldi sulla base dei vettori forniti dal programma di test".

Tali combinazioni stanno anche portando a un uso crescente della metrologia ibrida, combinando diverse tecniche per arrivare più rapidamente alla radice dei problemi.

Progettazione, ispezione, soluzioni di test

In effetti, la classica interazione tra progettazione, ispezione e stress termomeccanico è diventata solo più complessa con migliaia di connessioni sempre più piccole e fragili.

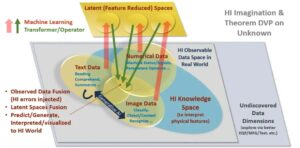

Un risultato è una rinnovata enfasi sullo spostamento a sinistra, per "progettare" si spera i problemi di CTE e i conseguenti effetti a cascata che possono portare a surriscaldamento e stress meccanico. E per aumentare le possibilità di prevenire, oltre a trovare difetti critici, sono necessarie sia la simulazione che l'ispezione, secondo Andras Vass-Varnai, dirigente dello sviluppo del portafoglio con il segmento dell'industria elettronica e dei semiconduttori di Siemens Digital Industries Software.

"La co-simulazione termica e strutturale utilizzando la dinamica del flusso computazionale (CFD), la modellazione a elementi finiti (FEA), ecc., nella fase iniziale di progettazione del pacchetto, aiuta sia a comprendere le prestazioni previste dell'assieme sia a fornire una buona base per ' Ottimizzazione guidata dall'intelligenza artificiale poiché molte delle scelte di progettazione possono essere parametrizzate", ha spiegato Vass-Varnai. “Una volta costruito il primo prototipo, i test sui transitori termici possono aiutare a mappare le prestazioni termiche del componente. Se c'è una discrepanza tra il comportamento termico previsto e quello reale, i dati del test possono essere utilizzati per "calibrare" le proprietà del materiale del gemello digitale della confezione e aggiornare le librerie dei materiali per una maggiore precisione iniziale dei progetti futuri".

Trovare il modo migliore per testare i bump array e progettare per i test è una sfida crescente. "E se c'è un segnale che va su e giù?" ha chiesto Rob Aitken, a Synopsys compagno. “Questo crea un problema di test, perché ora hai un segnale che non va da nessuna parte e un altro segnale che arriva da nessuna parte, e devi capire come testare queste cose. Li sonda? Ma in quel caso ci sono dimensioni fisiche che devi mantenere, e poi corri il rischio di danni meccanici. O trovi una sorta di struttura simile a JTAG? Ma questo poi riduce l'efficienza di questi punti connettivi. Siamo nella vasta fase di sperimentazione in cui tutti dicono: "Forse funzionerà, forse funzionerà". In questo momento, non vorrei necessariamente scommettere su cosa sia "quello".

Esistono opzioni di test sia indirette che dirette per l'indagine sui difetti, secondo JCET. Ad esempio, CSAM (Computed Scanning Acoustic Tomography) e 3D X-ray sono indiretti, mentre l'analisi trasversale meccanica è uno strumento per la prova diretta. JCET dispone di avanzate apparecchiature di caratterizzazione termica per caratterizzare anche i problemi di materiale/struttura derivanti da difetti meccanici.

L'ispezione ottica è, come sempre, l'approccio più rapido per l'ispezione in linea, ma la migliore pratica è un approccio ibrido. "Il metodo migliore per rilevare cortocircuiti/aperture e difetti marginali sarebbe SPI (ispezione della pasta saldante) per pre-rifusione AOI (ispezione ottica automatizzata) per post-rifusione AOI per raggi X in linea", ha consigliato Timothy Skunes, vicepresidente della ricerca e sviluppo in Nordson Test & Inspection CyberOttica portafoglio.

Inoltre, possono essere utili altre modalità, specialmente nei nodi avanzati. Ad esempio, un approccio recente per caratterizzare la deformazione nei dispositivi a semiconduttore è la spettroscopia Raman (RS). "RS è altamente applicabile per le misurazioni sulla struttura, offrendo misurazioni rapide dell'ordine di secondi e piccole dimensioni di spot di pochi micron per consentire misurazioni dettagliate", ha affermato Barak di Nova. "La difficoltà di misurare direttamente la deformazione sulle strutture prima dell'introduzione della spettroscopia Raman come strumenti di metrologia in linea nella fabbrica ha portato a test in fasi molto successive del processo di fabbricazione".

In definitiva, per un'ispezione approfondita, non ci sono scorciatoie. I calcoli del budget possono richiedere metriche comparative, come il costo iniziale di un nuovo strumento rispetto al costo continuo di RMA eccessivi. E c'è un'altra cosa da considerare: come assicurarti di poterti fidare dei tuoi dati.

“Hai intenzione di buttare via quello che probabilmente era un buon materiale per assicurarti di non avere alcun materiale problematico in quello che trasmetti all'utente finale? Chi ne sopporterà il costo?" ha avvertito Mike McIntyre, direttore della gestione dei prodotti software presso Sull'innovazione, che raccomanda un database statistico per un'accurata valutazione comparativa durante la classificazione automatizzata dei difetti.

warpage

Uno dei peggiori risultati dello stress è la deformazione. Potrebbe sorprendere che la deformazione possa essere difficile da rilevare, ma l'effetto non è sempre così ovvio come sembrerebbe. La deformazione provoca lievi differenze di complanarità tra chip e substrato, causando una connessione insufficiente di alcuni microbump con i pad sottostanti, un errore chiamato non bagnato.

"Prendete ad esempio un processore avanzato da 50 a 60 mm", ha affermato Chen. “A causa delle sue grandi dimensioni, è difficile elaborare senza deformazioni. Tuttavia, se lo strumento di fissaggio dello stampo è regolato al centro della sua finestra di processo, può superare l'ispezione ed essere prodotto con rese elevate. Il problema è che la tolleranza può essere molto ristretta. Non appena hai un po' di inclinazione della matrice sopra la deformazione, hai problemi di non bagnato.

Peggio ancora, se ciò accade a passi di rigonfiamento nell'intervallo di 50 µm (dimensione del rigonfiamento ̴35 µm), immagina i problemi quando le dimensioni del rigonfiamento si riducono ulteriormente. È già una preoccupazione per l'industria automobilistica, mentre si muove verso la sua prossima generazione nel 2023-2024. La transizione critica sarà intorno al nodo 28nm, ha affermato Chen.

Fig. 1 Gli utensili per l'attacco dello stampo hanno una finestra di processo molto ristretta per l'inclinazione dello stampo in caso di deformazione. Fonte: Brucker

Non bagna

"Non bagnato" è un termine ampio che copre diversi problemi che possono verificarsi con i dossi di saldatura, la maggior parte dei quali sono frustranti e sottili. Poiché la saldatura è spesso allo stato liquido, il processo di applicazione è stato soprannominato "bagnatura". I collegamenti tenui sono chiamati "non bagnati", che stanno diventando sempre più una sfida in nodi più piccoli con connessioni più sottili.

I non bagnati spesso sfuggono ai tipici processi di screening, solo per presentarsi successivamente come chip restituiti (RMA). Le cause alla radice possono essere termiche, meccaniche o una combinazione, come il ciclo termico in un'auto che percorre anche un terreno accidentato. L'effetto cumulativo può fornire una sollecitazione termomeccanica sufficiente per interrompere il contatto.

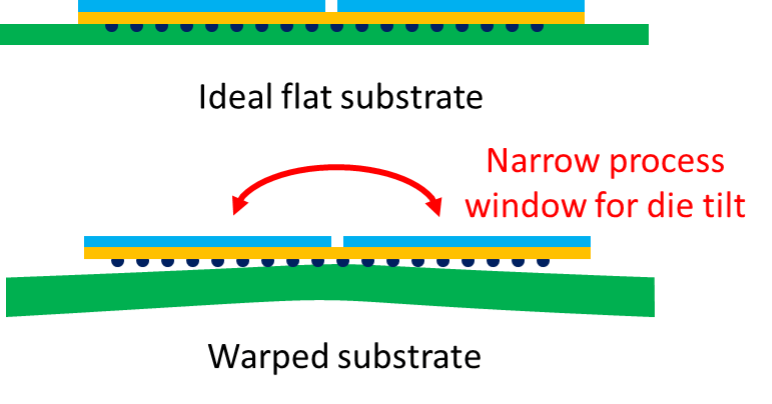

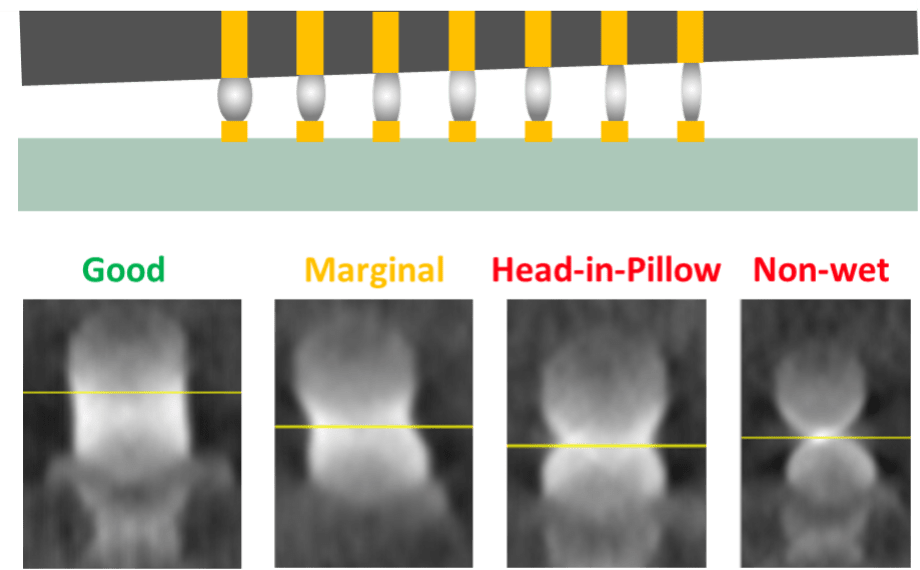

Esistono soprannomi aggiuntivi che descrivono tipi specifici di problemi. Invece della forma liscia e colonnare di una buona connessione, in un difetto "head-in-pillow", una palla sembra affondare nell'altra, come una testa su un cuscino.

"Sta ancora facendo contatto, quindi il test elettrico può essere buono, ma puoi vedere che è molto fragile", ha detto Chen, indicando la radiografia di una testa nel cuscino. “Non appena hai uno stress termico o uno stress meccanico, potrebbe rompersi completamente. Anche se si tratta di un contatto non bagnato, la connessione sottile porta a prestazioni ad alta resistenza, non ottimali e probabilmente non durerà a lungo. Un aperto non bagnato non funzionerà affatto. In uno scenario tipico con l'inclinazione dello stampo, c'è una transizione visibile da protuberanze ben formate a non bagnate".

Il problema critico sono i difetti latenti: connessioni sufficientemente funzionali da superare i test elettrici ma fallire sul campo.

Fig. 2 Transizione graduale da buone protuberanze a non bagnate in presenza di inclinazione dello stampo. Fonte: Brucker

"È un grosso problema in questo momento con molti tipi di dispositivi a causa degli effetti dello stress termico", ha affermato Chen. “Un cliente aveva un prodotto che ha superato lo screening dell'e-test ed è stato spedito. Sfortunatamente, hanno avuto molti RMA a causa di guasti non bagnati che si sono sviluppati in seguito.

Alcune aziende stanno affrontando questo problema attraverso ispezioni manuali dolorosamente noiose. Sfortunatamente, qualsiasi esame umano è soggetto all'affaticamento dell'operatore, soprattutto quando gli esaminatori cercano di individuare errori impercettibili durante un turno di più ore.

Sul lato positivo, ora ci sono approcci automatizzati all'ispezione, come strumenti a raggi X che possono essere utilizzati in linea. "C'è un grande fattore trainante verso l'ispezione ad alta velocità e completamente automatizzata per raggiungere <100 dppb, in particolare per l'industria automobilistica", ha affermato Chen.

Diventa più complicato da lì. "In particolare, anche la saldatura, responsabile di molti non bagnati, è soggetta all'elettromigrazione", ha affermato Tom Marinis, uno dei membri principali dello staff tecnico di laboratorio di Draper. "Se la densità di corrente in una connessione tra un chip e il substrato è troppo alta per una particolare saldatura per un periodo di tempo, poiché la temperatura di fusione della saldatura può essere relativamente bassa rispetto alla temperatura operativa del dispositivo, è possibile ottenere la migrazione degli atomi e in realtà formano dei vuoti e alla fine aprono una connessione”.

Marinis ha avvertito che gli strumenti di modellazione commerciale a livello di dispositivo-PCB non sono abbastanza maturi per avvisare in modo coerente di potenziali problemi di elettromigrazione, quindi è importante eseguire comunque un test di invecchiamento accelerato.

Conclusione

In definitiva, il rilevamento di problemi di affidabilità dovuti a difetti latenti richiederà una metrologia di campionamento più elevata, sensibile a spostamento, rotazione, altezza, inclinazione e altri parametri dello stampo. Sarà inoltre necessario fare maggiore affidamento sulla modellazione multifisica per cercare di anticipare e risolvere potenziali problemi prima della produzione. E poiché l'industria dei semiconduttori e quella automobilistica continuano a mescolarsi, c'è molto di più in gioco oltre alle sole RMA.

"Il costo del fallimento cresce in modo esponenziale man mano che i difetti latenti passano dai dispositivi ai moduli alle auto che potrebbero mettere in pericolo la vita delle persone", ha affermato Chen. Questo è il motivo per cui i produttori di chip stanno creando soluzioni olistiche che combinano progettazione, ispezione e test per rilevare meglio i guasti latenti.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Fonte: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- accelerata

- Secondo

- precisione

- preciso

- Raggiungere

- attivo

- effettivamente

- aggiunta

- aggiuntivo

- indirizzamento

- Avanzate

- INVECCHIAMENTO

- Mettere in guardia

- Tutti

- consente

- già

- Sebbene il

- sempre

- .

- ed

- Un altro

- anticipare

- applicabile

- applicazioni

- AMMISSIONE

- approccio

- approcci

- RISERVATA

- aree

- in giro

- montaggio

- valutazione

- associato

- allegare

- Automatizzata

- settore automobilistico

- industria automobilistica

- Vasca

- palla

- basato

- base

- Orso

- perché

- diventare

- diventando

- prima

- dietro

- essendo

- sotto

- MIGLIORE

- Scommettere

- Meglio

- fra

- Al di là di

- Big

- maggiore

- Po

- Rompere

- ampio

- budget limitato.

- costruito

- incassato

- affari

- sviluppo commerciale

- detto

- Può ottenere

- auto

- auto

- Custodie

- lotta

- Causare

- cause

- causando

- centro

- CFD

- Challenge

- sfidato

- sfide

- impegnativo

- probabilità

- Modifiche

- caratterizzare

- chen

- patata fritta

- Chips

- scelte

- classico

- classificazione

- combinazione

- combinazioni

- combinare

- combinato

- combinando

- Venire

- Uncommon

- Aziende

- rispetto

- completamente

- complesso

- complicato

- componente

- Problemi della Pelle

- condizioni

- Connettiti

- veloce

- Connessioni

- Prendere in considerazione

- contatti

- continua

- Nucleo

- angoli

- Costo

- potuto

- copertura

- creare

- creato

- crea

- Creazione

- critico

- Corrente

- Attualmente

- cliente

- Clienti

- taglio

- dati

- Banca Dati

- trattare

- densità

- descrivere

- Design

- disegni

- dettagliati

- sviluppare

- sviluppato

- Mercato

- dispositivo

- dispositivi

- *

- differenze

- diverso

- Livello di difficoltà

- digitale

- gemello digitale

- dimensioni

- dirette

- direttamente

- Direttore

- fare

- Dont

- giù

- negoziante di tessuti

- autista

- soprannominato

- durante

- dinamica

- Presto

- effetto

- effetti

- efficienza

- sforzi

- Elettronica

- enfasi

- Ingegneria

- abbastanza

- garantire

- usate

- errori

- particolarmente

- eccetera

- Etere (ETH)

- Anche

- alla fine

- qualunque cosa

- esempio

- esecutivo

- espansione

- previsto

- esperto

- ha spiegato

- Esplorazione

- in modo esponenziale

- estremamente

- FAIL

- Fallimento

- più veloce

- fatica

- Caratteristiche

- compagno

- pochi

- campo

- Fico

- figura

- Infine

- Trovare

- ricerca

- Nome

- flusso

- modulo

- essere trovato

- da

- frustrante

- funzionale

- ulteriormente

- ELETTRICA

- ottenere

- va

- andando

- buono

- graduale

- Crescita

- cresce

- Manovrabilità

- Hard

- capo

- altezza

- Aiuto

- aiuta

- Alta

- superiore

- vivamente

- olistica

- Fiduciosamente

- HOT

- Come

- Tutorial

- HTTPS

- umano

- IBRIDO

- impatti

- importante

- in

- Compreso

- Aumento

- crescente

- industrie

- industria

- inizialmente

- invece

- strumento

- integrazione

- Introduzione

- indagine

- isolato

- problema

- sicurezza

- IT

- stessa

- Genere

- di laboratorio

- grandi

- larga scala

- superiore, se assunto singolarmente.

- Cognome

- strato

- galline ovaiole

- portare

- principale

- Leads

- Guidato

- Livello

- biblioteche

- probabile

- Collegamento

- Liquido

- Lives

- Lunghi

- lotto

- Basso

- mantenere

- make

- Fare

- gestione

- direttore

- Manuale

- manufatto

- molti

- carta geografica

- Mario

- corrispondenza

- materiale

- Materiale

- alunni

- max-width

- si intende

- misurazioni

- di misura

- meccanico

- membro

- metalli

- metodo

- metodologie

- Metrica

- metrologia

- forza

- migrazione

- commistione

- modellismo

- modulo

- moduli

- Scopri di più

- maggior parte

- si muove

- multiplo

- nano

- necessariamente

- di applicazione

- negativo.

- tuttavia

- New

- Nuove tecnologie

- notizie

- GENERAZIONE

- nodo

- nodi

- ovvio

- offerta

- ONE

- in corso

- aprire

- operativo

- operatore

- ottimizzazione

- Opzioni

- minimo

- Altro

- pacchetto

- Packages

- imballaggio

- Dolore

- parametri

- particolare

- particolarmente

- Passato

- persone

- eseguire

- performance

- periodo

- fase

- Fisico

- piazzole

- Platone

- Platone Data Intelligence

- PlatoneDati

- Giocare

- giocatori

- punto

- punti

- Polimeri

- lavori

- positivo

- possibile

- potenziale

- pratica

- presenza

- Presidente

- prevenzione

- Direttore

- Precedente

- probabilmente

- sonda

- Problema

- problemi

- processi

- i processi

- Processore

- Prodotto

- gestione del prodotto

- Produzione

- Programma

- prova

- propriamente

- proprietà

- prototipo

- fornire

- purché

- metti

- R&D

- gamma

- veloce

- di rose

- recente

- raccomanda

- ridurre

- riduce

- riflessione

- relativamente

- problemi di

- fiducia

- rinnovato

- richiedere

- richiede

- riparazioni

- ricerca e sviluppo

- colpevole

- risultante

- Risultati

- Rischio

- rischi

- ruoli

- radice

- Correre

- Suddetto

- dice

- bilancia

- scansione

- scenario

- screening

- secondo

- sembra

- segmento

- prodotti

- semiconduttore

- anziano

- delicata

- alcuni

- Shadow

- Forma

- spostamento

- MUTEVOLE

- spediti

- Corti

- mostrare attraverso le sue creazioni

- Signal

- significativa

- significativamente

- simulazione

- Taglia

- Dimensioni

- piccole

- inferiore

- So

- Software

- Soluzioni

- alcuni

- Arrivo

- Fonte

- specifico

- Spettroscopia

- Spot

- STAFF

- Stage

- tappe

- palo

- inizia a

- Regione / Stato

- statistiche

- Ancora

- stress

- strutturale

- La struttura

- soggetto

- di successo

- tale

- sorprendente

- Consulenza

- tecniche

- Tecnologie

- test

- Testing

- I

- L'area

- loro

- Là.

- termico

- cosa

- cose

- migliaia

- Attraverso

- Lancio

- tempo

- volte

- a

- insieme

- tolleranza

- pure

- strumenti

- top

- verso

- transizione

- Affidati ad

- TURNO

- Tipi di

- tipico

- capire

- imminenti

- Aggiornanento

- uso

- Utente

- vario

- Fisso

- Vicepresidente

- visibile

- noto

- Che

- quale

- while

- OMS

- volere

- senza

- Lavora

- Salsiccia di assorbimento

- sarebbe

- raggi X

- i rendimenti

- Trasferimento da aeroporto a Sharm

- zefiro