Nella terminologia dei circuiti integrati, un abbassamento è la caduta di tensione che si verifica in un circuito. Questo è un fenomeno ben noto e può accadere a causa dei seguenti motivi. L'alimentatore scende al di sotto dell'intervallo operativo per il quale è stato progettato un chip, provocando un abbassamento. Gli elementi conduttivi assorbono più corrente di quella per cui sono stati progettati, determinando un abbassamento. A volte, l'interferenza del segnale o il rumore sull'alimentatore possono anche causare fluttuazioni di tensione, con conseguente abbassamento.

Le cadute possono influire sulle operazioni di un circuito. La riduzione delle prestazioni del chip, che porta a tempi di elaborazione più lunghi, è uno di questi effetti. Ma i seguenti sono alcuni degli impatti più gravi e/o catastrofici. Il chip potrebbe assorbire più corrente per mantenere il livello di prestazioni, portando a un aumento del consumo energetico e della dissipazione del calore. Ciò può portare a una durata ridotta del chip e, nei casi più gravi, a un guasto completo del chip a causa di variazioni di configurazione e tenuta. Le cadute possono anche causare il danneggiamento dei dati o errori nell'output. Questo è un problema molto serio per le applicazioni che dipendono dalla precisione e dall'affidabilità del chip.

Naturalmente, il fenomeno dei droop viene preso in seria considerazione quando si progettano chip e sistemi. I metodi più comuni per mitigare i droop sono il disaccoppiamento dell'alimentazione, la regolazione della tensione, l'ottimizzazione del circuito e la gestione dell'alimentazione a livello di sistema. Le condizioni e l'ambiente operativo in cui il chip funzionerà sono attentamente considerati durante la progettazione di soluzioni di attenuazione della caduta.

Problemi dei giorni nostri

Man mano che i SoC diventano più complessi, anche i problemi di droop possono diventare piuttosto complessi. Il design di un SoC deve essere ottimizzato per prestazioni, potenza, costo, fattore di forma, ecc. Oltre all'ottimizzazione per la mitigazione del droop. A volte questi obiettivi di ottimizzazione possono competere tra loro e andare controcorrente e devono essere fatti dei compromessi. Ad esempio, gli architetti SoC possono aumentare la tensione operativa, aggiungendo margine, per aggirare la caduta locale e globale, ma questo aumento aumenta la potenza in modo quadratico. In alternativa, i progettisti possono adattare la propria generazione di clock allo droop, il che rende le prestazioni una funzione del tempo di commutazione della generazione di clock.

Di conseguenza, i SoC di grandi dimensioni nell'elaborazione del data center e nello spazio AI sono particolarmente soggetti a droop. I carichi di lavoro dei clienti sono molto diversi e dinamici, il che porta a fluttuazioni significative nell'attività di commutazione e nell'assorbimento di corrente. Naturalmente, i sistemi non possono permettersi di lasciare che i problemi di droop non vengano affrontati. La potenziale responsabilità derivante da un output impreciso o da un guasto catastrofico di un chip è troppo elevata per i sistemi e le applicazioni odierne.

Problemi di caduta localizzati

Gli acceleratori specifici per le applicazioni sono ampiamente utilizzati insieme ai processori per uso generico per fornire le prestazioni e l'efficienza energetica richieste negli ambienti informatici esigenti di oggi. Ma questi acceleratori, insieme al crescente numero di core e alla natura asimmetrica dei carichi di lavoro, aumentano il rischio di cali di tensione localizzati. Queste cadute di tensione localizzate sono il risultato di un improvviso aumento dell'attività di commutazione e possono causare anomalie transitorie e potenziali guasti in modalità missione.

Quando si verifica un abbassamento localizzato, l'impatto può essere mitigato attraverso il ridimensionamento dinamico della frequenza. Ciò si ottiene regolando la temporizzazione di un circuito utilizzando un orologio programmabile. Un orologio programmabile consente di regolare dinamicamente la frequenza e la temporizzazione dell'orologio in base alle condizioni operative correnti del circuito.

Movellus rende facile affrontare le cadute localizzate

Movellus, uno dei principali fornitori di IP di sistemi digitali, ha sviluppato la famiglia di prodotti Aeonic Generate per affrontare i droop localizzati. Il portafoglio Movellus Aeonic offre soluzioni di clock adattivo che forniscono una rapida risposta alla caduta. Il portfolio include il sistema di clock adattivo. Gli elementi costitutivi sono costruiti con Verilog sintetizzabile, rendendoli intrinsecamente flessibili. Le soluzioni sono configurabili, scansionabili e process-portable per un'ampia gamma di applicazioni SoC avanzate.

La famiglia di prodotti Aeonic Generate è anche significativamente più piccola rispetto alle tradizionali soluzioni analogiche. Di conseguenza, i progettisti possono istanziare l'IP con la granularità richiesta senza alcun impatto significativo sull'area. Inoltre, man mano che i progetti si spostano verso geometrie di processo più fini, l'area Aeonic Generate continua a crescere, rendendola una soluzione ideale per i progetti futuri.

Un paio di casi d'uso

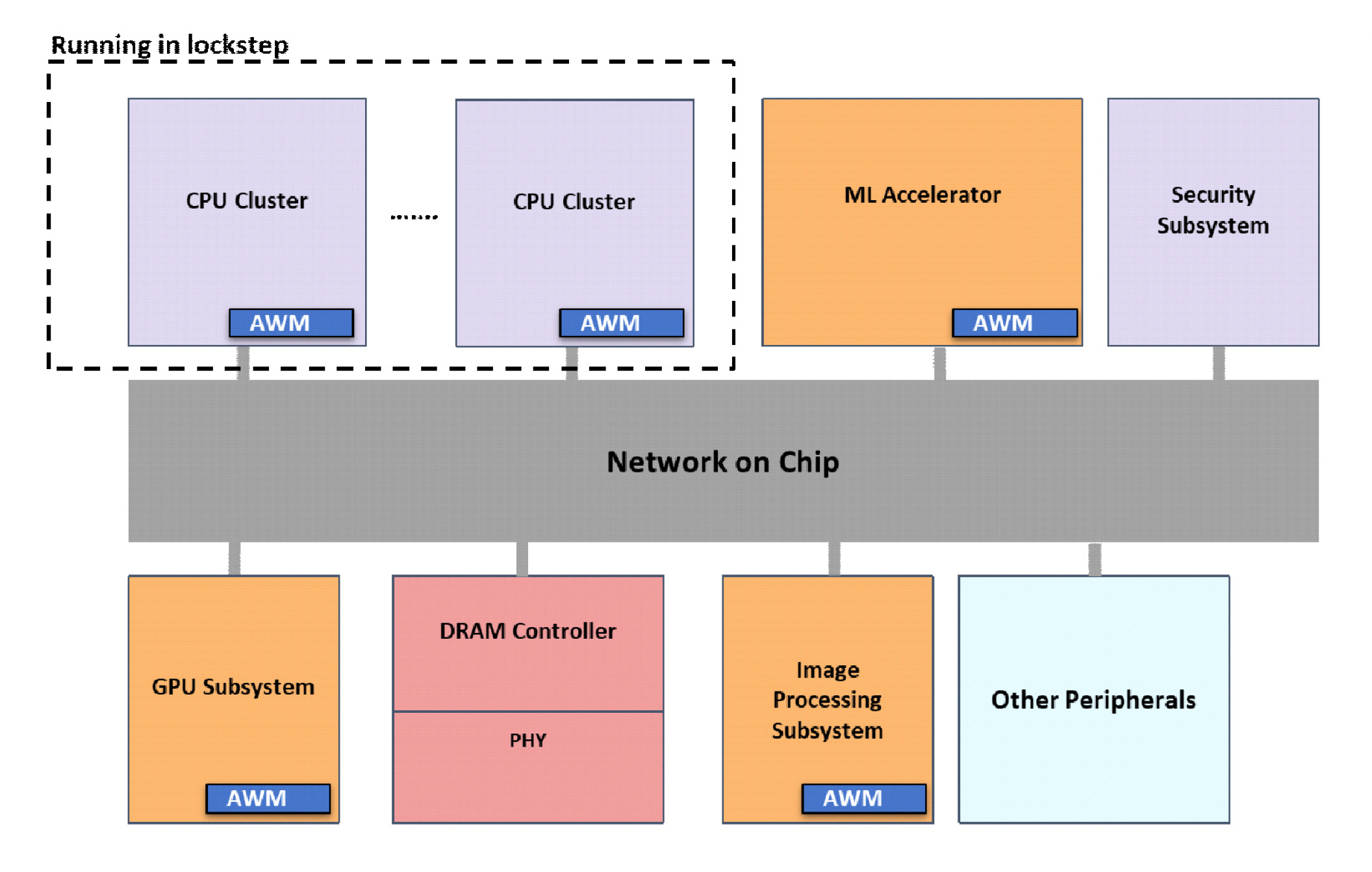

La figura seguente di Movellus mostra un'architettura di esempio di un processore ADAS con la piattaforma Aeonic Generate AWM per il supporto dello droop localizzato. Un architetto assocerebbe un modulo AWM a un sottoblocco o acceleratore specifico dell'applicazione per rispondere a droop localizzati guidati dal carico di lavoro entro cinque cicli di clock con spostamenti di frequenza rapidi e privi di glitch. Questo approccio fornisce una soluzione affidabile ed efficiente per affrontare le sfide dei droop localizzati nei mercati ADAS, 5G e delle reti di data center.

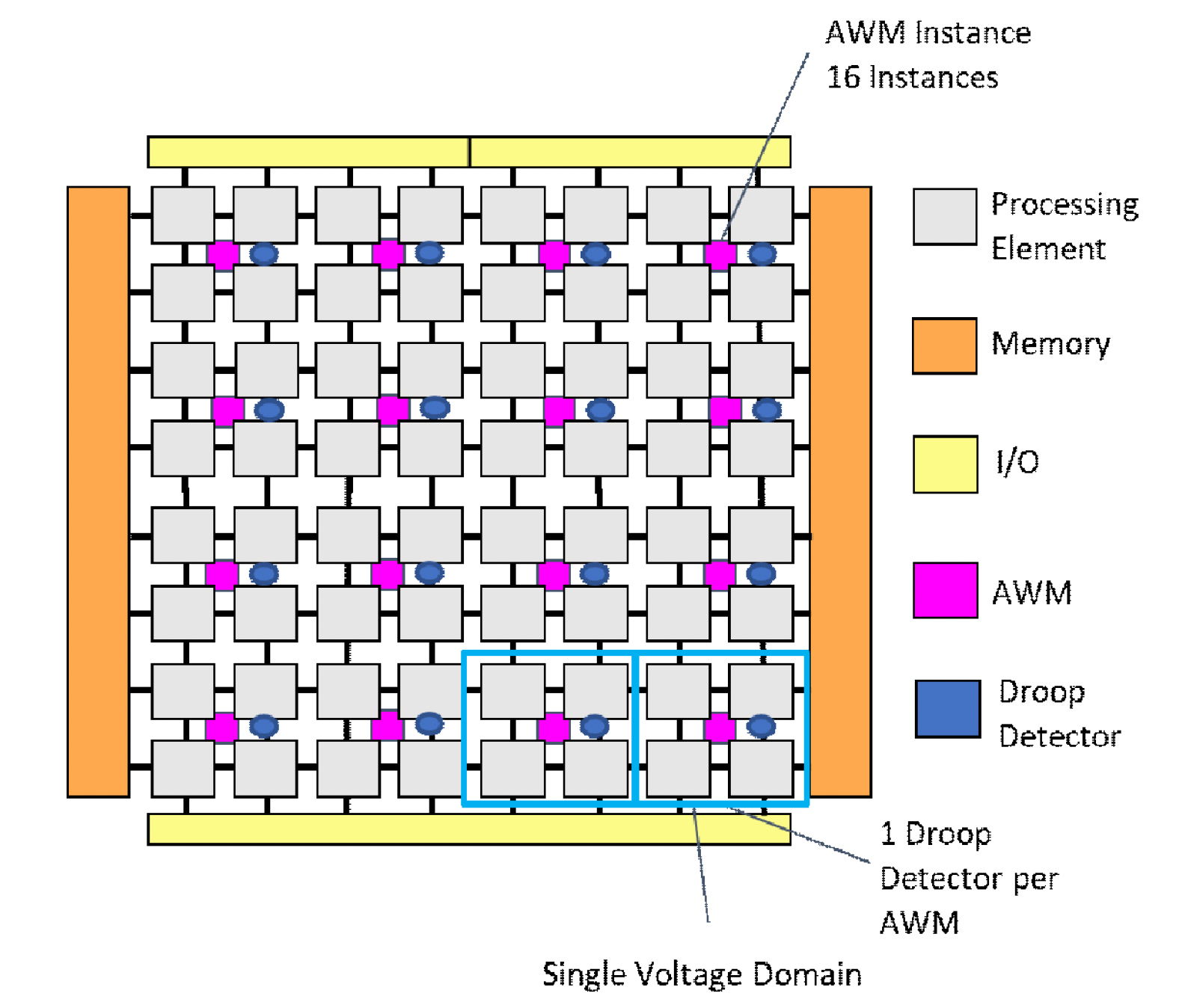

La figura seguente di Movellus mostra un'architettura di esempio di un mare di SoC per processori con Aeonic Generate per il supporto del droop localizzato. Un architetto accoppierebbe un modulo Aeonic Generate AWM con un rilevatore di caduta per il cluster di processori e il dominio di tensione associato per rispondere rapidamente alle cadute localizzate guidate dal carico di lavoro. Ciò consente ai progettisti di fornire una risposta di droop localizzata e indipendente senza alterare le prestazioni dei cluster di processori vicini.

Sommario

Cadute di tensione localizzate possono verificarsi in SoC eterogenei contenenti acceleratori specifici dell'applicazione. Questi droop possono portare a problemi di temporizzazione, problemi transitori e guasti in modalità missione in ADAS, reti di data center e applicazioni 5G. Gli architetti di sistema possono implementare il clock adattivo per rispondere a questi droop e mitigare l'impatto.

La famiglia Movellus™ Aeonic Generate Adaptive Workload Module (AWM) di prodotti IP per la generazione di clock ad alte prestazioni fa parte dell'architettura Aeonic Intelligent Clock Network™. Per ulteriori informazioni, fare riferimento a Movellus' Pagina Aeonic Generate™ AWM.

Leggi anche:

Vantaggi dei domini di clock sincroni su larga scala nei progetti di chip AI

È giunto il momento delle reti di orologi intelligenti

Vantaggi in termini di prestazioni, potenza e area (PPA) grazie alle reti di clock intelligenti

Condividi questo post tramite:- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- Platoblockchain. Web3 Metaverse Intelligence. Conoscenza amplificata. Accedi qui.

- Fonte: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :È

- 5G

- a

- acceleratore

- acceleratori

- precisione

- raggiunto

- attività

- adattare

- ADA

- aggiunta

- Inoltre

- indirizzo

- indirizzamento

- Rettificato

- Avanzate

- AI

- consente

- ed

- applicazioni

- approccio

- architettura

- SONO

- RISERVATA

- AS

- associato

- At

- basato

- BE

- diventare

- sotto

- vantaggi

- Bloccare

- Blocchi

- Costruzione

- costruito

- by

- Materiale

- Può ottenere

- non può

- attentamente

- casi

- catastrofico

- Causare

- centro

- sfide

- patata fritta

- Chips

- Orologio

- Cluster

- Uncommon

- competere

- completamento di una

- complesso

- Calcolare

- informatica

- condizioni

- considerazione

- considerato

- consumo

- continua

- Corruzione

- Costo

- potuto

- contatore

- Coppia

- corso

- Corrente

- cliente

- cicli

- dati

- Banca dati

- Datacenter

- giorno

- consegnare

- esigente

- Design

- progettato

- designer e gli illustratori veneziani,

- progettazione

- disegni

- sviluppato

- digitale

- distribuito

- paesaggio differenziato

- dominio

- domini

- disegnato

- Cadere

- Gocce

- dinamico

- dinamicamente

- ogni

- efficienza

- efficiente

- elementi

- Ambiente

- ambienti

- errori

- eccetera

- esempio

- Fallimento

- cadute

- famiglia

- figura

- flessibile

- fluttuazioni

- i seguenti

- Nel

- modulo

- Frequenza

- da

- function

- futuro

- scopo generale

- generare

- ELETTRICA

- ottenere

- globali

- Go

- Obiettivi

- accadere

- accade

- Avere

- Alta

- Alte prestazioni

- tenere

- HTTPS

- ideale

- Impact

- impatti

- realizzare

- in

- impreciso

- inclusi

- Aumento

- è aumentato

- Aumenta

- crescente

- studente indipendente

- informazioni

- integrato

- integrazione

- Intelligente

- intrinsecamente

- IP

- problema

- sicurezza

- IT

- grandi

- larga scala

- portare

- principale

- Livello

- responsabilità

- Vita

- locale

- più a lungo

- fatto

- mantenere

- FA

- Fare

- gestione

- Margine

- Mercati

- max-width

- metodi

- Ridurre la perdita dienergia con una

- attenuante

- attenuazione

- modulo

- moduli

- Scopri di più

- maggior parte

- cambiano

- Natura

- esigenze

- Rete

- internazionale

- Rumore

- segnatamente

- numero

- of

- Offerte

- on

- ONE

- operativo

- Operazioni

- ottimizzazione

- ottimizzati

- ottimizzazione

- Altro

- produzione

- parte

- performance

- esecuzione

- fenomeno

- piattaforma

- Platone

- Platone Data Intelligence

- PlatoneDati

- lavori

- Post

- potenziale

- energia

- Alimentazione di laboratorio

- processi

- lavorazione

- Processore

- processori

- Prodotti

- fornitore

- fornisce

- aumentare

- gamma

- veloce

- rapidamente

- Leggi

- tempo reale

- motivi

- Ridotto

- Regolamento

- problemi di

- affidabile

- necessario

- Rispondere

- risposta

- colpevole

- risultante

- Aumento

- Rischio

- Correre

- Scala

- scala

- MARE

- grave

- flessibile.

- grave

- Turni

- Spettacoli

- Signal

- significativa

- significativamente

- inferiore

- smart

- soluzione

- Soluzioni

- alcuni

- lo spazio

- tale

- improvviso

- fornire

- supporto

- adatto

- sistema

- SISTEMI DI TRATTAMENTO

- Tandem

- Tecnologia

- terminologia

- che

- I

- L'area

- loro

- Li

- Strumenti Bowman per analizzare le seguenti finiture:

- Attraverso

- tempo

- volte

- sincronizzazione

- a

- di oggi

- pure

- tradizionale

- uso

- molto diversificato

- via

- Tensione

- WELL

- noto

- quale

- largo

- Vasta gamma

- ampiamente

- volere

- con

- entro

- senza

- sarebbe

- zefiro