Itu sudah masuk kembali 1991 bahwa Cadence pertama kali mengumumkan nama produk Virtuoso, dan di sinilah kita 32 tahun kemudian dan produk tersebut masih hidup dan bekerja dengan cukup baik. Steven Lewis dari Cadence memberi saya kabar terbaru tentang sesuatu yang baru yang mereka sebut Studio Virtuoso, dan ini semua tentang desain IC khusus untuk dunia nyata. Dalam 32 tahun tersebut kita telah melihat proses semikonduktor berjalan mengikuti Hukum Moore dari 600nm menggunakan CMOS planar, turun ke era FinFET di bawah 22 nm, mencapai GAA pada node 3nm. Jelas sekali bahwa tuntutan alat EDA telah berubah karena node yang lebih kecil membawa efek fisik baru yang perlu dimodelkan dan disimulasikan untuk memastikan keberhasilan silikon pertama.

Fokus Cadence Virtuoso Studio adalah membantu desainer IC menghadapi tantangan masa kini melalui enam bidang:

- Peningkatan kompleksitas proses

- Menangani 10,000 detik simulasi sirkuit

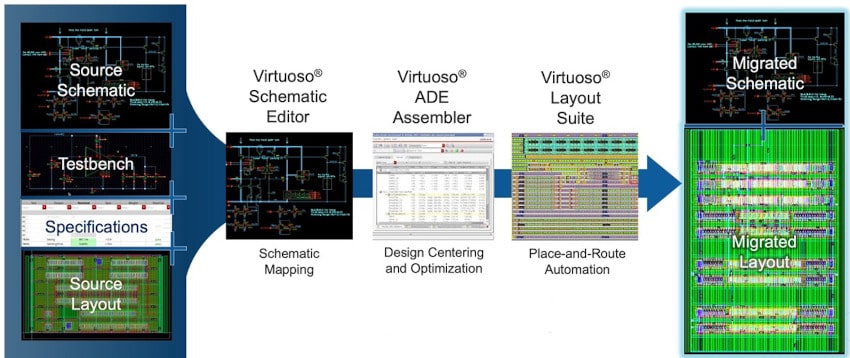

- Otomatisasi desain dan migrasi sirkuit

- Integrasi heterogen

- AI

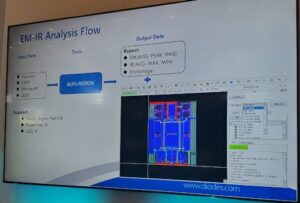

- Sign-off, verifikasi dan analisis dalam desain

Grafik Ahli ADE (Lingkungan Desain Analog) memungkinkan insinyur sirkuit untuk mengeksplorasi desain analog, sinyal campuran, dan RFIC melalui pengambilan skema dan simulasi sirkuit. Arsitektur Virtuoso ADE telah diubah untuk kontrol pekerjaan yang lebih baik, mengurangi penggunaan RAM, dan mempercepat simulasi dengan menggunakan cloud. Sebagai contoh, RAM yang dibutuhkan untuk menjalankan Spectre pada 10,000 simulasi dikurangi dari 420MB menjadi hanya 18MB untuk pemantauan simulasi, sementara evaluasi ekspresi menurun dari 420MB RAM menjadi hanya 280MB.

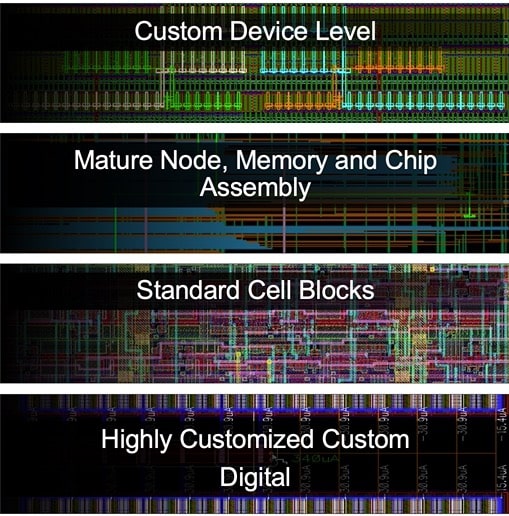

Pembaruan untuk Suite Tata Letak Virtuoso mencakup empat pilihan teknologi tempat dan rute, masing-masing disesuaikan dengan tugas unik yang ada di lingkungan Virtuoso:

Empat Teknologi P&R

Proses DRC dan LVS adalah bagian dari verifikasi fisik, dan menjalankannya dalam mode batch, memperbaiki dan mengulangi, menyebabkan jadwal pengembangan yang panjang. Verifikasi dalam desain memungkinkan penggunaan DRC dan LVS secara interaktif saat mengerjakan tata letak IC, sehingga umpan balik tentang apa yang harus diubah dengan cepat disorot, sehingga mempercepat produktivitas. Perancang tata letak yang menggunakan Virtuoso Layout Suite mendapat manfaat dari verifikasi dalam desain menggunakan Pegasus Teknologi DRC dan LVS.

Chiplet, kemasan 2.5D, dan 3D mencakup bidang desain PCB, paket, dan IC yang secara tradisional terpisah. Virtuoso Studio memungkinkan desain bersama dan verifikasi paket, modul, dan IC dengan:

Dalam waktu dekat, Anda akan melihat detail muncul tentang bagaimana AI diterapkan untuk secara otomatis beralih dari skema analog ke tata letak berdasarkan pembelajaran mesin dan spesifikasi. Tata letak uji coba yang dibuat secara otomatis ini akan semakin mempercepat proses yang sangat padat karya. Area pengembangan kedua untuk penerapan AI adalah masalah migrasi IP analog khusus ke node proses baru. Pantau terus.

Pelanggan awal Virtuoso Studio mencakup Perangkat Analog untuk desain bersama IC dan paket, desain konsumen IC terdepan di MediaTek, dan migrasi proses berbasis AI di Renesas.

Kesimpulan

Virtuoso Studio telah meluncurkan beberapa fitur baru yang mengesankan ke dalam rilis 23.1 yang dapat mulai digunakan oleh tim desain IC agar lebih produktif. Infrastruktur Virtuoso telah berubah untuk memenuhi tantangan Hukum Moore, simulasi dengan simulasi sirkuit 10,000 detik bersifat praktis, desain bersama RFIC dan modul 2.5D/3D didukung, verifikasi DRC/LVS dalam desain membutuhkan waktu lebih sedikit, dan AI lebih efisien. diterapkan untuk mengotomatiskan tugas-tugas analog.

Blog terkait

Bagikan postingan ini melalui:- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Sumber: https://semiwiki.com/eda/327556-whats-new-with-cadence-virtuoso/

- :memiliki

- :adalah

- $NAIK

- 1

- 10

- 3d

- a

- Tentang Kami

- mempercepat

- AI

- Semua

- memungkinkan

- sepanjang

- dan

- mengumumkan

- terapan

- arsitektur

- ADALAH

- DAERAH

- daerah

- AS

- At

- mengotomatisasikan

- secara otomatis

- Otomatisasi

- kembali

- berdasarkan

- BE

- menjadi

- makhluk

- di bawah

- Manfaat

- Lebih baik

- Terbawa

- by

- Irama

- panggilan

- CAN

- menangkap

- tantangan

- perubahan

- pilihan

- Jelas

- awan

- konsumen

- kontrol

- adat

- pelanggan

- hari

- tuntutan

- Mendesain

- perancang

- desainer

- desain

- rincian

- Pengembangan

- Devices

- melakukan

- domain

- turun

- setiap

- efek

- memungkinkan

- Insinyur

- memastikan

- Lingkungan Hidup

- Era

- evaluasi

- contoh

- mengharapkan

- menyelidiki

- Fitur

- umpan balik

- Pertama

- Fokus

- Untuk

- empat

- dari

- lebih lanjut

- masa depan

- Go

- tangan

- Memiliki

- membantu

- di sini

- Disorot

- Seterpercayaapakah Olymp Trade? Kesimpulan

- HTML

- HTTPS

- ICS

- impresif

- in

- memasukkan

- Infrastruktur

- interaktif

- IP

- Pekerjaan

- jpg

- tenaga kerja

- Hukum

- tata ruang

- Memimpin

- pengetahuan

- Lewis

- Panjang

- mesin

- Mesin belajar

- March

- max-width

- Pelajari

- migrasi

- mode

- modul

- Modul

- pemantauan

- lebih

- nama

- Dekat

- dibutuhkan

- New

- Fitur Baru

- simpul

- node

- of

- on

- ONE

- paket

- paket

- pengemasan

- bagian

- fisik

- Tempat

- plato

- Kecerdasan Data Plato

- Data Plato

- Pos

- Praktis

- menyajikan

- Masalah

- proses

- Produk

- produktif

- produktifitas

- menempatkan

- segera

- RAM

- mencapai

- nyata

- dunia nyata

- mengurangi

- mengurangi

- melepaskan

- wajib

- Rute

- Run

- berjalan

- skala

- Kedua

- lihat detailnya

- semikonduktor

- terpisah

- Silikon

- simulasi

- ENAM

- lebih kecil

- So

- beberapa

- sesuatu

- merentang

- spesifikasi

- Spectrum

- kecepatan

- awal

- tinggal

- studio

- sukses

- rangkaian

- Didukung

- Mengambil

- Dibutuhkan

- tugas

- tugas

- tim

- Teknologi

- bahwa

- Grafik

- mereka

- Ini

- Melalui

- waktu

- untuk

- alat

- secara tradisional

- percobaan

- unik

- Memperbarui

- penggunaan

- menggunakan

- Verifikasi

- melalui

- BAIK

- Apa

- sementara

- akan

- dengan

- kerja

- dunia

- tahun

- zephyrnet.dll