S2C telah menjadi pemimpin global dalam pembuatan prototipe FPGA selama hampir dua dekade, dan platform pembuatan prototipe FPGA miliknya telah memantau dengan cermat ketersediaan FPGA terbaru – termasuk FPGA terbaru dari Xilinx dan Intel. Dan mereka benar-benar memenuhi janjinya untuk memajukan solusi pembuatan prototipe mereka untuk pembuatan prototipe desain skala besar – peningkatan membuat prototipe kapasitas dan kemampuan platform untuk mendukung desain gerbang bernilai miliaran dolar.

Melihat kembali ke awal kuartal keempat tahun 4, S2020C mengumumkan dukungan untuk Xilinx VU2P UltraScale+ FPGA yang baru, yang menawarkan platform prototipe FPGA tunggal, ganda, dan quad. Kemudian, pada bulan Desember 19, S2020C menindaklanjuti dengan pengumuman keluarga platform prototyping Prodigy Logic Matrix berdensitas tinggi dengan 2 FPGA per Logic Matrix, 8 Logic Matrix per rak server tunggal (8 FPGA), dan koneksi beberapa rak server bersama-sama. Iterasi pertama Logic Matrix dikirimkan dengan FPGA Xilinx VU64 (dijuluki LX1) kepada pelanggan awal yang tidak sabar menunggu versi VU19P (dijuluki LX2).

Sekarang, S2C meningkatkan permainan Logic Matrix-nya dengan LX2, yang meningkatkan kapasitas gerbang prototipe yang dapat digunakan sebesar 60% dibandingkan versi VU440! Semakin banyak gerbang yang dapat digunakan per FPGA berarti lebih sedikit FPGA, lebih sedikit interkoneksi FPGA, dan kinerja lebih tinggi untuk desain prototipe yang sama. Dengan perkiraan kapasitas gerbang sebesar 392 juta gerbang per LX2, rak server standar yang terisi penuh dengan 8 LX2 memungkinkan perkiraan kapasitas pembuatan prototipe lebih dari 3 miliar gerbang ASIC!

Gambar 1: Matriks Logika Prodigy LX2

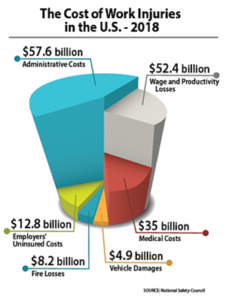

| Keluarga Matriks Logika Prodigy | ||

| LX1 | LX2 | |

| FPGA | XCVU440 | XCVU19P |

| Perkiraan Gerbang ASIC (M) | 240 | 392 |

| Jumlah FPGA | 8 | 8 |

| Sel Logika Sistem (K) | 44,328 | 71,504 |

| Memori FPGA (Mb) | 709 | 1,327.2 |

| Irisan DSP | 23,040 | 30,720 |

| I/O Pengguna Eksternal | 9,216 | 10,368 |

| Transceiver SerDes | 384 GTH | 640 GT |

| Konektor Ajaib | 64 | 72 |

| Konektor PGT | 8 | 0 |

| Konektor Pemancar | 80 MSAS masing-masing dengan 4 GTH + 8 IO | 160 MCIO masing-masing dengan 4 GTY + 8 IO |

| Kinerja SerDes | 16 Gbps | 28 Gbps |

Angka 2: Keluarga Matriks Logika

Interkoneksi yang fleksibel dan berkecepatan tinggi adalah kunci untuk pembuatan prototipe FPGA kepadatan tinggi, dan Logic Matrix mendukung strategi interkoneksi 3 tingkat hierarki: Jembatan Pendek untuk interkoneksi antar FPGA yang bertetangga; Tautan Sys untuk interkoneksi kabel FPGA bandwidth tinggi, dan Tautan Trans untuk interkoneksi FPGA SerDes jarak jauh melalui kabel MCIO. Untuk menyederhanakan interkoneksi FPGA dan memaksimalkan nilai Tautan Trans, aliran partisi S2C mendukung High-Speed Transceiver Pin Multiplexing (HSTPM) Xilinx yang baru diperkenalkan, menyederhanakan transfer sinyal akurat siklus, pin-multiplexing, dan konektivitas SerDes FPGA berlatensi rendah.

Untuk meminimalkan waktu pembuatan prototipe, dan memaksimalkan produktivitas pembuatan prototipe, alat produktivitas pembuatan prototipe S2C lainnya dirancang dengan mempertimbangkan Logic Matrix, termasuk Waktu Proses Pemain Pro perangkat lunak – dan alat pembuatan prototipe S2C tambahan termasuk Jembatan Proto, MDM Pro, dan S2C IP Siap Prototipe.

Waktu Proses Pemain Pro perangkat lunak disertakan dengan LX2, menyediakan fitur-fitur praktis seperti manajemen jam tingkat lanjut, pengujian mandiri terintegrasi, deteksi papan otomatis, pemrograman tegangan I/O, beberapa unduhan FPGA, serta pemantauan dan manajemen sistem jarak jauh. Juga disertakan adalah AXEVision, alat debugging AXI-over-Ethernet bawaan untuk menyederhanakan debugging jarak jauh dari desain terkait AXI.

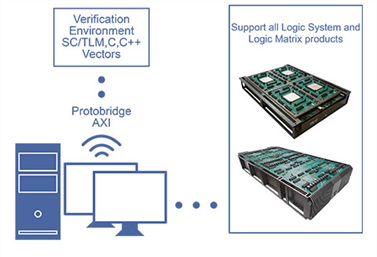

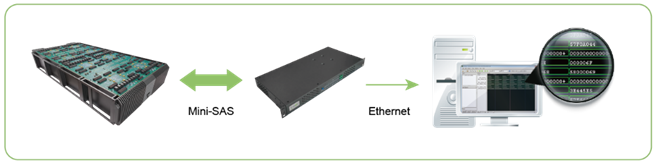

Jembatan Proto mendukung transfer data throughput tinggi (hingga 1 GB/dtk) antara PC host dan LX2 – memungkinkan transfer sejumlah besar transaksi model perangkat lunak, streaming video, atau stimulus pengujian lainnya untuk validasi sistem.

Gambar 3: ProtoBridge

MDM Pro memiliki fitur debugging jejak mendalam dengan pemicu silang hingga delapan FPGA, tampilan jejak sinyal multi-FPGA dari satu jendela tampilan, penyimpanan bentuk gelombang jejak eksternal sebesar 64GB, kecepatan pengambilan sampel jejak hingga 125MHz, dan mendukung bahasa mesin status pemicu untuk penangkapan jejak yang kompleks persyaratan.

Gambar 4: MDM Pro

S2C juga menawarkan perpustakaan yang kaya IP Siap Prototipe untuk LX2 – Daughter Cards plug-and-play – yang mempercepat penciptaan lingkungan pembuatan prototipe di sekitar prototipe FPGA.

Gambar 5: Kartu Anak IP Siap Prototipe

Matriks Logika Ajaib LX2 tersedia sekarang. Untuk informasi lebih lanjut, silakan hubungi perwakilan penjualan S2C setempat Anda, atau kunjungi www.s2ceda.com.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/prototyping/s2c-eda/304634-s2c-delivers-on-plan-to-scale-up-fpga-prototyping-platforms-to-billions-of-gates/- 2020

- Tambahan

- mengumumkan

- Pengumuman

- sekitar

- asic

- tersedianya

- Milyar

- papan

- kabel

- Kapasitas

- koneksi

- Konektivitas

- pelanggan

- data

- mengantarkan

- Mendesain

- Deteksi

- jarak

- Awal

- Lingkungan Hidup

- keluarga

- Fitur

- Ara

- Pertama

- aliran

- FPGA

- permainan

- Gates

- Aksi

- HTTPS

- Termasuk

- informasi

- Intel

- IP

- kunci

- Bahasa

- besar

- Terbaru

- Perpustakaan

- lokal

- pengelolaan

- Matriks

- juta

- pemantauan

- menawarkan

- Penawaran

- Lainnya

- PC

- prestasi

- Platform

- Platform

- per

- produktifitas

- Produktivitas Alat

- Pemrograman

- prototyping

- Tarif

- Persyaratan

- penjualan

- meningkatkan

- Perangkat lunak

- Solusi

- Negara

- rangsangan

- penyimpanan

- Penyelarasan

- stream

- mendukung

- Mendukung

- sistem

- uji

- Transaksi

- nilai

- Video

- menunggu

- SIAPA