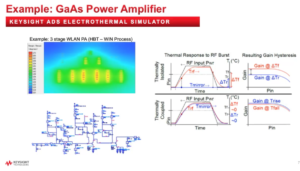

Ungkapan lama bahwa penyembuhannya lebih buruk daripada penyakitnya adalah tepat ketika membahas MBIST untuk SOC besar di mana menjalankan banyak tes MBIST secara paralel dapat melebihi kemampuan jaringan distribusi daya (PDN). Memory Built-In Self-Test (MBIST) biasanya berjalan secara otomatis selama power on event. Karena keinginan untuk mempercepat waktu pengujian dan boot chip, pengujian ini sering kali dijalankan secara paralel. Masalahnya adalah mereka dapat dengan mudah menghasilkan aktivitas switching yang urutan besarnya di atas level yang ditemukan selama operasi chip biasa. Memang, tingkat aktivitas switching yang lebih tinggi ini tidak hanya dapat menyebabkan penurunan pasokan yang memengaruhi hasil pengujian, tetapi juga panas tinggi yang dihasilkan dapat merusak chip. Efek ini dapat menyebabkan binning yang salah atau kegagalan langsung dan laten.

Solusinya adalah dengan mensimulasikan aktivitas MBIST untuk memprediksi beban pada PDN dan efek termal terkait. Dengan hasil simulasi di tangan, desainer dapat memutuskan dengan tepat berapa banyak dan blok memori mana yang dapat diuji secara paralel. Namun, ini tidak selalu layak di SOC besar dengan banyak blok memori karena waktu simulasi mungkin menjadi penghalang. Dengan level gerbang dan simulasi RTL yang kurang akurat, tidak mungkin menjalankan siklus yang cukup untuk mendapatkan informasi yang dibutuhkan.

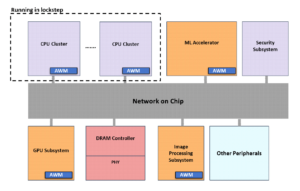

Dalam buku putih berjudul "Menganalisis implikasi kekuatan penggunaan MBIST", Siemens EDA melihat bagaimana desainer dapat menjalankan simulasi yang memadai untuk membuat keputusan yang tepat tentang strategi pengujian sebelum tapeout. Siemens bekerja dengan ARM pada salah satu chip pengujian mereka untuk membuat kasus pengujian di mana mereka dapat menerapkan emulasi perangkat keras dengan aplikasi DFT dan Power untuk emulator perangkat keras Siemens Veloce. Pertama, aplikasi Veloce DFT digunakan untuk menampilkan aktivitas internal selama emulasi MBIST. Aplikasi ini menggunakan Standard Test Interface Language (STIL) dan menghasilkan file output standar industri.

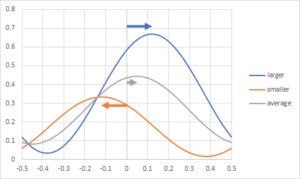

Aplikasi Veloce Power mengambil informasi aktivitas dari proses MBIST untuk menghasilkan bentuk gelombang, profil daya, dan peta panas yang dapat menunjukkan bila ada lonjakan daya di atas batas yang ditentukan. Dengan informasi ini, insinyur uji dapat membuat keputusan berdasarkan informasi tentang urutan MBIST.

Kasus uji ARM yang dijelaskan dalam buku putih Siemens berisi 176 juta gerbang. Siemens menggunakan sistem Veloce dengan 6 papan Veloce Strato untuk kasus uji ini. Proses emulator Veloce hanya membutuhkan waktu 26 jam, 15,600 kali lebih cepat dari simulasi level gerbang. Manfaat lain dari aliran Veloce adalah bahwa informasi aktivitas dialirkan oleh aplikasi Power ke alat-alat listrik dalam aliran, menghemat ruang dan waktu disk. Hasil dari uji kasus menunjukkan beberapa lonjakan daya yang melanggar spesifikasi desain SOC. Keluaran dari aplikasi Veloce Power menunjukkan tingkat daya total melalui simulasi bersama dengan kontribusi daya terpisah untuk jam, logika kombinasional, dan memori. Demikian juga, ada informasi tentang di mana pada dadu daya digunakan. Informasi ini memudahkan untuk menentukan di mana ada masalah.

Menemukan masalah seperti ini membutuhkan jutaan atau miliaran siklus clock. Keterbatasan simulator perangkat lunak membuatnya menjadi penghalang untuk melakukan analisis yang diperlukan. Emulasi menawarkan jalan unik untuk memeriksa secara dekat dampak daya MBIST dan operasi uji lainnya jauh sebelum silikon. Buku putih Siemens menawarkan wawasan tentang metode daya yang digunakan pada kasus uji nyata. Buku putih tersedia untuk diunduh untuk dibaca di situs web Siemens.

Bagikan postingan ini melalui: Sumber: https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Tentang Kami

- analisis

- aplikasi

- aplikasi

- ARM

- tersedia

- makhluk

- Menyebabkan

- keping

- Keripik

- Clock

- mengandung

- bisa

- menyembuhkan

- Mendesain

- Penyakit

- selama

- mudah

- Insinyur

- Acara

- peristiwa

- lebih cepat

- Pertama

- aliran

- ditemukan

- Gates

- menghasilkan

- Perangkat keras

- High

- Seterpercayaapakah Olymp Trade? Kesimpulan

- HTTPS

- industri

- informasi

- IT

- bahasa

- besar

- memimpin

- Tingkat

- adalah ide yang bagus

- memuat

- Panjang

- Peta

- juta

- jutaan

- dibutuhkan

- jaringan

- Penawaran

- Operasi

- urutan

- Lainnya

- kertas

- kekuasaan

- Masalah

- profil

- Bacaan

- Hasil

- Run

- berjalan

- penghematan

- Siemens

- simulasi

- Perangkat lunak

- Space

- kecepatan

- Penyelarasan

- streaming

- menyediakan

- sistem

- uji

- pengujian

- tes

- panas

- Melalui

- waktu

- alat

- unik

- biasanya

- Situs Web

- laporan resmi

- bekerja