Metodologi Verifikasi Universal (UVM) adalah cara populer untuk membantu memverifikasi desain SystemVerilog, dan mencakup a sistem konfigurasi yang sayangnya memiliki beberapa masalah kecepatan dan penggunaan. Rich Edelman dari Siemens EDA menulis makalah terperinci setebal 20 halaman tentang topik cara menghindari masalah ini, dan saya telah membahasnya untuk merangkum hal-hal penting untuk Anda. Insinyur verifikasi menggunakan database konfigurasi UVM untuk menetapkan nilai, kemudian mendapatkan nilai tersebut nanti dalam pengujian UVM mereka. Salah satu contoh pengaturan dan mendapatkan nilai 'T' adalah:

uvm_config#(T)::set(scope, instance_path_name, field_name, value); uvm_config#(T)::get(scope, instance_path_name, field_name, value);

Menghubungkan meja uji UVM ke perangkat yang diuji menggunakan database konfigurasi untuk melewati antarmuka virtual. Ada tiga masalah dalam penggunaan konfigurasi UVM:

- Kode besar, sekitar 2,600 baris kode

- Memerlukan pencocokan tipe yang tepat, jadi 'int' dan 'bit' tidak sama

- Kode lambat

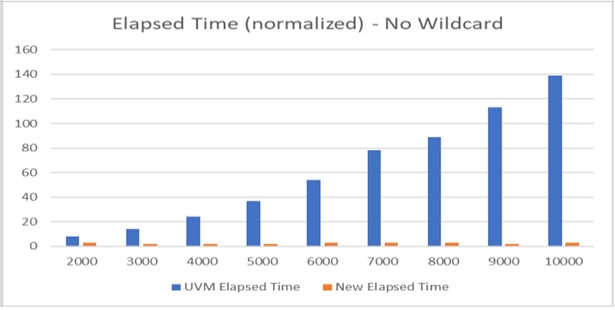

Pertimbangkan kasus kode lambat, karena dengan ribuan panggilan ke set() menggunakan nama dengan wildcard dapat memakan waktu hingga 30 menit untuk menyelesaikan fase 'set' dan 'get'.

Rich mengusulkan solusi baru untuk konfigurasi UVM yang memiliki kecepatan lebih cepat, hanya membutuhkan waktu beberapa detik dibandingkan.

Jika kode UVM Anda menghindari penggunaan wildcard dan memiliki sedikit perintah 'set', maka kode Anda akan berjalan lebih cepat.

Solusi yang mungkin untuk masalah konfigurasi UVM adalah:

- Gunakan variabel global sebagai gantinya

- Gunakan konfigurasi UVM dengan satu set()

- Gunakan konfigurasi UVM dengan beberapa set()

- Gunakan pohon konfigurasi

- Coba sesuatu yang berbeda

Pendekatan terakhir dalam mencoba sesuatu yang berbeda adalah solusi baru, dan pendekatan ini terus menggunakan API set() dan get(), lalu menyederhanakannya dengan menghapus parameterisasi konfigurasi, menghapus prioritas, dan menghapus perubahan algoritma pencarian. Hasil dari pendekatan baru ini adalah kecepatan yang tinggi.

Item konfigurasi baru Anda didefinisikan dalam kelas turunan dari 'config_item', dan contoh di bawah ini menunjukkan 'int value” sebagai properti yang sedang disetel. Untuk tujuan debug, Anda menambahkan fungsi cantik-cetak.

kelas my_special_config_item memperluas config_item; fungsi baru(string nama = "my_special_config_item"); super.baru(nama); nilai int fungsi akhir; string fungsi virtual convert2string(); kembalikan $sformatf("%s - nilai=%0d <%s>", get_name(), nilai, super.convert2string()); kelas akhir fungsi akhir

'config_item' memiliki atribut nama, dan nama ini dicari, ditambah nama instance. Objek konfigurasi juga memiliki fungsi get_name() untuk mengembalikan nama. Untuk menemukan “instance_name.field_name” database konfigurasi menggunakan array asosiatif untuk kecepatan pencarian dan pembuatan yang cepat.

Untuk ketertelusuran Anda dapat mengetahui siapa yang menyetel atau siapa yang memanggil get, karena nama file dan nomor baris adalah bidang dalam pemanggilan fungsi set() dan get().

set(null, "top.ab*", "SPEED", my_speed_config, `__FILE__, `__LINE__) get(null, "top.abcdmonitor1", "SPEED", speedconfig, `__FILE__, `__LINE__)

Antrian pengakses dapat dicetak selama debug untuk melihat siapa yang memanggil set() dan get().

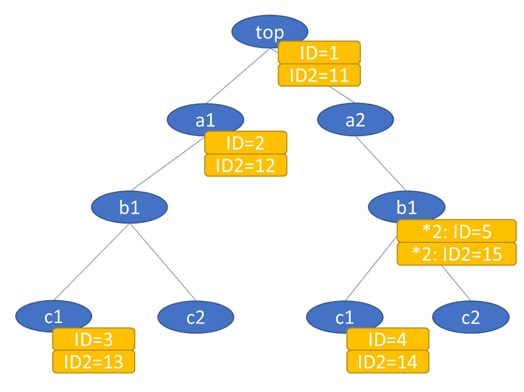

Untuk mendukung wildcard diperlukan penambahan mekanisme pencarian menggunakan container. Pertimbangkan nama instance 'top.abcd*_0'.

Bagian wildcard dari nama instance ditangani dengan menggunakan pohon kontainer, bukan array asosiatif.

Kesimpulan

Berbagi data antara modul/instance dan dunia berbasis kelas di testbench UVM dapat dilakukan menggunakan database konfigurasi UVM, namun waspadai penurunan kecepatannya. Jika metodologi Anda menggunakan banyak konfigurasi, maka pertimbangkan untuk menggunakan pendekatan baru yang diperkenalkan yang memiliki paket yang menggunakan sekitar 300 baris kode, bukan 2,600 baris kode dalam file database konfigurasi UVM.

Baca makalah 20 halaman penuh, Menghindari Kegilaan Konfigurasi Dengan Cara Mudah di Siemens EDA.

Blog terkait

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiwiki.com/eda/339885-making-uvm-faster-through-a-new-configuration-system/

- :memiliki

- :adalah

- :bukan

- $NAIK

- 30

- 300

- 600

- a

- Tentang Kami

- menambahkan

- menambahkan

- algoritma

- juga

- an

- dan

- Apa pun

- api

- pendekatan

- ADALAH

- susunan

- AS

- At

- menghindari

- sadar

- b

- BE

- karena

- makhluk

- di bawah

- antara

- by

- bernama

- Panggilan

- CAN

- kasus

- perubahan

- kelas

- kode

- perbandingan

- lengkap

- konfigurasi

- Mempertimbangkan

- Wadah

- Wadah

- terus

- penciptaan

- data

- Basis Data

- didefinisikan

- Berasal

- desain

- terperinci

- alat

- berbeda

- dilakukan

- selama

- Mudah

- Insinyur

- Eter (ETH)

- contoh

- Meluas

- FAST

- lebih cepat

- beberapa

- Fields

- File

- Menemukan

- Untuk

- dari

- penuh

- fungsi

- mendapatkan

- mendapatkan

- Aksi

- mati

- membantu

- highlight

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HTTPS

- if

- in

- termasuk

- contoh

- sebagai gantinya

- interface

- diperkenalkan

- masalah

- IT

- jpg

- hanya

- Terakhir

- kemudian

- baris

- baris

- tampak

- lookup

- banyak

- Membuat

- sesuai

- max-width

- mekanisme

- Metodologi

- menit

- menit

- banyak

- nama

- nama

- New

- solusi baru

- jumlah

- obyek

- of

- on

- ONE

- hanya

- or

- di luar

- paket

- kertas

- bagian

- lulus

- tahap

- plato

- Kecerdasan Data Plato

- Data Plato

- plus

- Populer

- Pos

- hak lebih tinggi

- masalah

- milik

- mengusulkan

- tujuan

- menghapus

- menghapus

- wajib

- Hasil

- kembali

- Kaya

- Run

- cakupan

- detik

- melihat

- set

- pengaturan

- Pertunjukkan

- Siemens

- disederhanakan

- lambat

- perlambatan

- So

- larutan

- Solusi

- beberapa

- sesuatu

- kecepatan

- kecepatan

- Tali

- meringkaskan

- besar

- mendukung

- sistem

- T

- Mengambil

- pengambilan

- uji

- bahwa

- Grafik

- mereka

- kemudian

- Sana.

- Ini

- ini

- ribuan

- tiga

- Melalui

- waktu

- untuk

- puncak

- tema

- Lacak

- pohon

- mencoba

- mengetik

- bawah

- sayangnya

- Universal

- penggunaan

- menggunakan

- kegunaan

- menggunakan

- nilai

- Nilai - Nilai

- variabel

- Verifikasi

- memeriksa

- melalui

- maya

- Cara..

- yang

- SIAPA

- akan

- dengan

- dunia

- menulis

- kamu

- Anda

- zephyrnet.dll