Sistem multi-die terdiri dari beberapa die fungsional khusus (atau chiplet) yang dirangkai dalam paket yang sama untuk membuat sistem yang lengkap. Sistem multi-die baru-baru ini muncul sebagai solusi untuk mengatasi perlambatan hukum Moore dengan menyediakan jalur untuk menskalakan fungsionalitas dalam chip yang dikemas sedemikian rupa sehingga dapat diproduksi dengan hasil yang baik.

Selain itu, sistem multi-die memungkinkan fleksibilitas SKU produk dalam hal penskalaan kinerja agar sesuai dengan kebutuhan segmen pasar yang berbeda, optimalisasi node proses per fungsi dengan memadukan dan mencocokkan berbagai node proses dalam produk yang sama, waktu pemasaran yang lebih cepat, dan risiko yang lebih rendah.

Untuk memungkinkan kepadatan perutean die-to-die yang lebih tinggi dan mendukung lalu lintas bandwidth yang lebih tinggi antar die, teknologi paket telah berevolusi untuk menciptakan paket baru yang canggih, berdasarkan interposer silikon (dengan TSV) atau jembatan silikon dan, yang lebih baru, lapisan redistribusi (RDL) , fanout, dan media HD.

Aspek kunci keberhasilan sistem multi-die adalah kemampuan untuk memastikan sistem dapat diuji dalam berbagai fase manufaktur dan perakitan, serta memastikan pengoperasian yang andal di lapangan. Dengan menggunakan langkah-langkah perakitan ekstra dan teknologi benturan dan pengemasan yang lebih kompleks, sistem multi-die memerlukan prosedur pengujian dan keandalan yang melampaui apa yang canggih untuk desain monolitik.

Cetakan telanjang, dan kemasannya sendiri, harus diuji terlebih dahulu untuk memastikan bahwa semua cetakan atau kemasan yang cacat terdeteksi sebelum dirakit dalam sebuah paket. Jika cetakan yang cacat terdeteksi hanya setelah perakitan, maka sistem multi-die yang lengkap harus dibuang sehingga berdampak serius pada biaya. Proses pengujian cetakan telanjang disebut pengujian Known Good Die (KGD).

Proses perakitannya sendiri bervariasi tergantung teknologi pengemasan yang dipilih. Misalnya, teknologi chip first, yang mana cetakan ditempatkan terlebih dahulu dan interkoneksi dibangun di atasnya, tidak memungkinkan pengujian “paket yang dikenal baik”, yang berpotensi mengakibatkan penghapusan cetakan yang baik jika interkoneksinya rusak. Di sisi lain, dalam teknologi chip-last, di mana interkoneksi dibuat secara terpisah dan cetakan dipasang di atasnya, memungkinkan pengujian awal terhadap paket sebelum perakitan, sehingga mengurangi kemungkinan cetakan yang bagus akan dibuang.

Solusi pengujian sistem multi-die dapat dibagi menjadi beberapa aspek:

- Uji cakupan masing-masing blok di dalam dadu

- Cakupan tes kematian individu (mati telanjang)

- Pengujian sistem rakitan (dengan cakupan die-to-die)

- Akses ke kain uji dalam cetakan telanjang

- Akses hierarki untuk menguji fabric setelah perakitan

Artikel ini menjelaskan manfaat solusi pengujian komprehensif yang memanfaatkan IP UCIe untuk memastikan keandalan sistem multi-die.

DFT untuk antarmuka UCIe

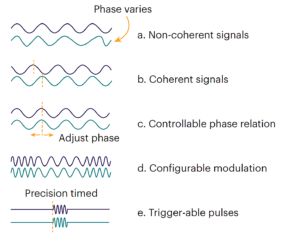

Solusi cakupan pengujian yang tinggi untuk antarmuka UCIe dicapai dengan menerapkan fitur kemampuan pengujian yang luas di IP UCIe untuk menghilangkan cetakan yang rusak pada tahap pengujian cetakan telanjang. Beberapa fiturnya antara lain:

- Pindai rantai yang mencakup semua sirkuit digital yang disintesis

- Fungsionalitas BIST khusus blok khusus

- Fungsionalitas loopback built-in self-test (BIST) yang mencakup rantai sinyal lengkap hingga pin IO

- Urutan biner pseudorandom yang dapat diprogram (PRBS) dan generator serta pemeriksa pola pengujian yang ditentukan pengguna

- Injeksi kesalahan untuk menghilangkan kesalahan lintasan

Selain itu, fungsionalitas untuk memperluas cakupan ke tautan die-to-die, setelah perakitan paket dapat membantu mencapai cakupan pengujian tingkat tinggi, termasuk:

- Fungsionalitas loopback BIST sisi jauh (mati-ke-mati).

- Tautan mati-ke-mati BIST

- Margin mata 2D untuk menganalisis marginalitas

- Uji per jalur dan fungsionalitas perbaikan

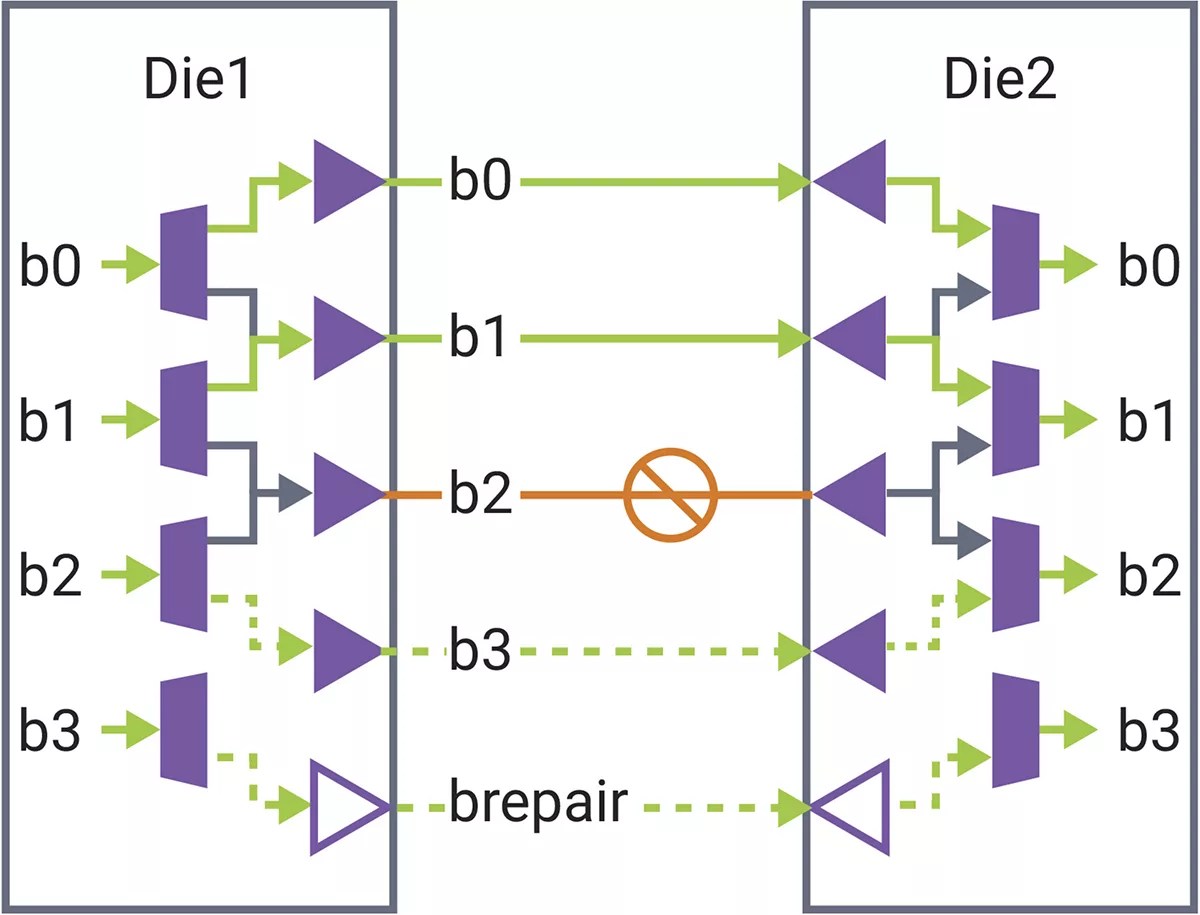

Tes dan perbaikan UCIe

Paket tingkat lanjut memungkinkan perutean kepadatan tinggi dengan micro-bumping nada halus dan perutean pada interposer silikon atau RDL. Selama proses perakitan, beberapa sambungan micro-bump mungkin tidak terbentuk dengan baik dan mungkin rusak. UCIe menawarkan kemampuan untuk menguji dan memperbaiki koneksi ini setelah perakitan dengan cara memulihkan potensi kehilangan hasil.

Pengujian dan perbaikan UCIe dijalankan selama pengujian produksi dan pada inisialisasi tautan. Pada tahap pengujian setiap link diperiksa cacatnya pada kecepatan lambat. Tautan yang rusak diperbaiki dengan merutekan ulang data ke tautan cadangan yang telah ditentukan sebelumnya oleh standar UCIe.

Konfigurasi UCIe yang menargetkan paket tingkat lanjut mencakup hingga 8 pin cadangan per arah (TX dan RX) untuk memungkinkan perbaikan semua tautan fungsional:

- Empat pin cadangan untuk perbaikan pin data, 2 pin untuk setiap kelompok 32 pin data

- Satu pin cadangan untuk jam dan jam serta perbaikan pin track

- Tiga pin cadangan, masing-masing untuk pin valid, pin data sideband, dan perbaikan pin data jam

Eksekusi pengujian dan perbaikan terjadi ketika tidak ada lalu lintas yang valid pada tautan mati-ke-mati. Setelah perbaikan selesai dan link diinisialisasi, diasumsikan dalam keadaan baik dan trafik dapat dilalui tanpa kendala. Konfigurasi PHY yang dihasilkan, disebut tanda tangan perbaikan PHY, disimpan dalam register internal di kedua ujung link.

Degradasi karakteristik microbump karena penuaan atau lainnya selama pengoperasian dapat berdampak pada kinerja link. Hal ini akan terdeteksi pada tingkat protokol dengan peningkatan tingkat kesalahan bit (BER) atau, yang terburuk, dengan hilangnya data. Dalam hal ini, tautan tersebut diperkirakan akan terputus dan langkah pengujian dan perbaikan baru akan dilakukan.

Namun, beberapa aplikasi memiliki persyaratan yang ketat dalam hal kontinuitas lalu lintas pada tautan mati-ke-mati – aplikasi tersebut tidak dapat mentolerir gangguan lalu lintas selama pengoperasian. Untuk kasus ini, solusi pengujian menambahkan Signal Integrity Monitors (SIM) ke setiap pin penerima UCIe.

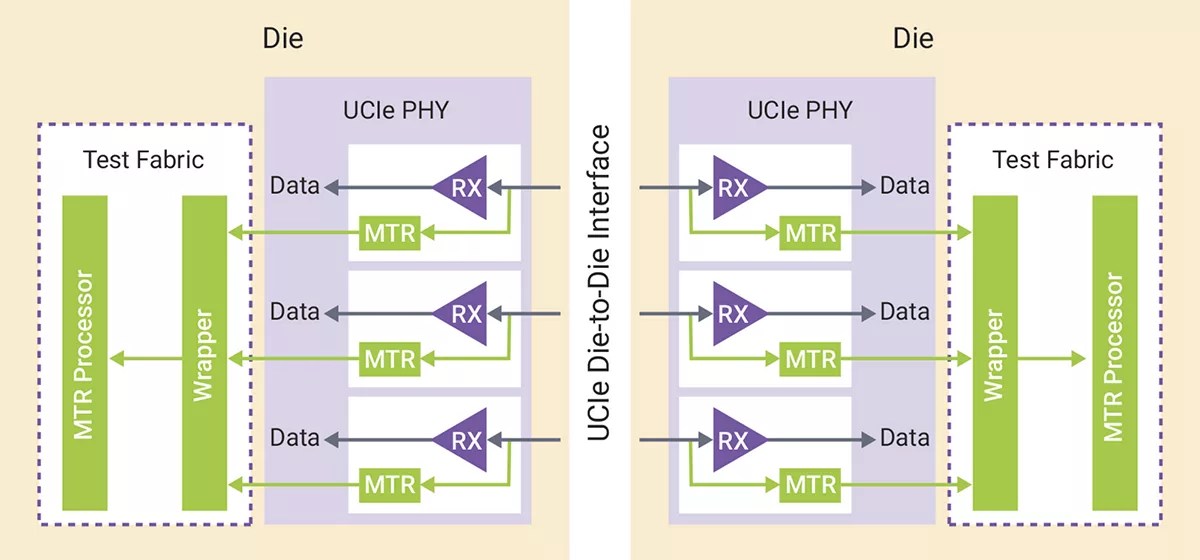

Gambar 1: Perbaikan tautan menggunakan tautan cadangan bawaan.

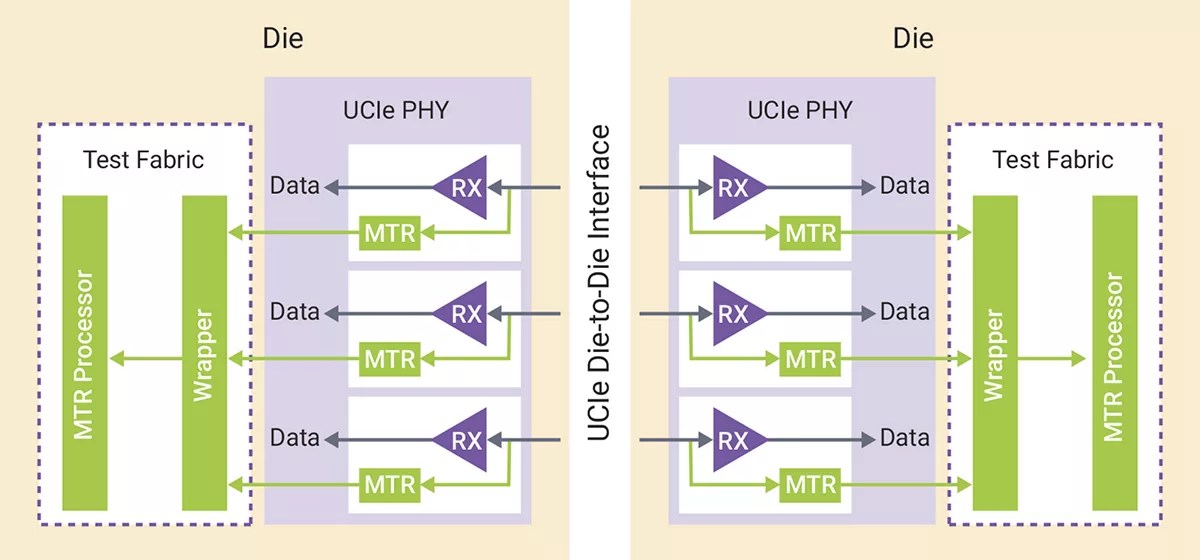

Monitor integritas sinyal

Monitor SIM adalah blok kecil yang tertanam pada receiver. Mereka terus-menerus merasakan sinyal pada pin penerima, selama operasi normal, untuk mengidentifikasi variasi karakteristik sinyal yang dapat mempengaruhi kinerja tautan atau menunjukkan bahwa tautan tersebut tidak lagi sehat dan mungkin putus dalam waktu dekat.

Data yang dikumpulkan oleh masing-masing sensor dikumpulkan dalam pengontrol Pemantauan, Pengujian, dan Perbaikan (MTR), di luar antarmuka, untuk diproses lebih lanjut. Mengumpulkan data dari beberapa tautan UCIe dapat memberikan wawasan instan tentang kesehatan sistem multi-die dan memungkinkan pemeliharaan tautan secara prediktif.

Jika tautan tertentu diperkirakan berisiko mengalami kegagalan fungsi melalui prosedur ini, tautan tersebut dapat dinonaktifkan dan data dirutekan ulang ke salah satu tautan cadangan, memanfaatkan mekanisme perbaikan UCIe PHY, bahkan tanpa gangguan lalu lintas.

Gambar 2: Solusi pemantauan kesehatan untuk tautan UCIe.

Mempercepat waktu bangun

Meskipun pola lalu lintas untuk sebagian besar kasus penggunaan antarmuka mati-ke-mati, misalnya dalam pemisahan atau penskalaan server, diasumsikan stabil selama pengoperasian, dalam beberapa kasus penggunaan lalu lintas mungkin menunjukkan perilaku meledak-ledak. Dalam kasus seperti ini, diinginkan untuk membawa antarmuka ke mode daya rendah untuk menghemat daya saat tidak ada lalu lintas. Inisialisasi ulang tautan dapat dipercepat dengan menghindari proses pengujian dan perbaikan dan mengandalkan tanda tangan perbaikan UCIe PHY yang dibuat selama inisialisasi PHY sebelumnya.

Konsep ini dapat diperluas lebih lanjut pada situasi dimana dadu dimatikan sepenuhnya. Dalam kasus ini, tanda tangan perbaikan PHY diambil dari PHY dan disimpan pada memori permanen on-die (eFuse atau flash). Memori tersebut mungkin dapat menyimpan banyak tanda tangan, mencakup kasus atau kondisi penggunaan yang berbeda, sehingga memungkinkan fleksibilitas pengguna tambahan.

Mempercepat pengujian cetakan dengan UCIe

Waktu ujian adalah komoditas yang mahal. Dimungkinkan untuk mempercepat waktu pengujian dengan mempartisi strategi pengujian secara hierarki untuk menjalankan pengujian berbagai cetakan secara paralel. Hirarki dapat diperluas ke beberapa die dalam sistem multi-die dengan menghubungkan infrastruktur pengujian kedua die secara hierarki. Pendekatan seperti ini memungkinkan akses ke semua die dalam sistem multi-die dari antarmuka pengujian JTAG (atau serupa) tunggal di die utama.

Seringkali batasan waktu pengujian adalah waktu untuk memuat atau membaca vektor pengujian ke dalam cetakan. Antarmuka JTAG dapat menjadi penghambat kecepatan. Untuk mengatasi keterbatasan ini, perancang dapat menggunakan antarmuka berkecepatan tinggi yang ada seperti PCI Express (PCIe) atau USB, dll. sebagai antarmuka ke peralatan pengujian. Vektor dan perintah pengujian dipaketkan untuk antarmuka tersebut dan didepacketisasi pada cetakan selama fase pengujian produksi.

Banyak cetakan yang tidak memiliki antarmuka berkecepatan tinggi, namun antarmuka cetakan-ke-mati UCIe dapat digunakan, selama pengujian, untuk memindahkan vektor pengujian yang besar dan perintah antar cetakan dengan kecepatan tinggi. Antarmuka die-to-die UCI memperluas akses DFT berkecepatan tinggi di seluruh sistem multi-die yang lengkap tanpa menambah jumlah pin, yang sangat penting untuk IO dan die dengan area terbatas.

Kesimpulan

Selain antarmuka die-to-die UCIe, faktor umum yang memungkinkan semua fitur pengujian dan peningkatan keandalan ini adalah struktur pengujian, perbaikan, dan pemantauan yang dapat menghubungkan semua blok internal. Struktur pengujian, perbaikan, dan pemantauan mencakup berbagai cetakan dalam sistem multi-cetakan, menyediakan infrastruktur hierarki terstruktur yang mencapai fungsi-fungsi penting berikut:

- Mengelola pengujian kematian individu dalam sistem multi-mati

- Mengoptimalkan penjadwalan pengujian untuk mengurangi waktu pengujian

- Mendukung akses pengujian berkecepatan tinggi di seluruh cetakan, melalui antarmuka UCIe

- Mengumpulkan informasi dari antarmuka pemantauan kesehatan yang tertanam di antarmuka UCIe dan memungkinkan pemrosesan tingkat sistem lebih lanjut

- Mengelola penyimpanan tanda tangan perbaikan PHY dalam memori non-volatil

- Dan lain-lain

Synopsys menyediakan solusi sistem multi-die yang komprehensif dan terukur, termasuk EDA dan IP, untuk integrasi heterogen yang cepat. Untuk konektivitas mati-ke-mati yang aman dan andal, Synopsys menawarkan solusi Pengontrol UCIe, PHY, dan Verifikasi IP yang lengkap. Sebagai bagian dari Synopsys SLM & Test Family, solusi UCIe Monitoring, Test and Repair (MTR) yang lengkap tersedia bersama dengan solusi STAR Hierarchical System (SHS). Solusi MTR mencakup monitor integritas sinyal untuk mengukur kualitas sinyal pada jalur UCIe, BIST untuk pengujian mandiri, dan logika perbaikan untuk alokasi jalur redundan, sedangkan solusi SHS berfungsi sebagai jaringan konektivitas yang mendukung standar industri IEEE 1687, IEEE 1149.1, dan IEEE 1838 antarmuka. Solusi lengkap ini memungkinkan pemantauan kesehatan UCIe secara efisien dan hemat biaya di seluruh fase siklus hidup silikon, yang sangat penting untuk pengoperasian sistem multi-die yang andal.

Sumber:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoAiStream. Kecerdasan Data Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Beli dan Jual Saham di Perusahaan PRE-IPO dengan PREIPO®. Akses Di Sini.

- Sumber: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 1

- 8

- a

- kemampuan

- mempercepat

- dipercepat

- mengakses

- Mencapai

- dicapai

- Mencapai

- di seluruh

- tambahan

- Tambahan

- Menambahkan

- maju

- Setelah

- Penuaan

- Semua

- alokasi

- mengizinkan

- memungkinkan

- sepanjang

- an

- menganalisa

- dan

- aplikasi

- pendekatan

- ADALAH

- artikel

- AS

- penampilan

- aspek

- dirakit

- Majelis

- diasumsikan

- At

- tersedia

- menghindari

- Bandwidth

- berdasarkan

- BE

- menjadi

- sebelum

- makhluk

- Manfaat

- antara

- Luar

- Memblokir

- Blok

- kedua

- Istirahat

- jembatan

- membawa

- dibangun di

- built-in

- by

- bernama

- CAN

- tidak bisa

- kasus

- kasus

- rantai

- rantai

- karakteristik

- diperiksa

- keping

- Clock

- Jam

- komoditi

- Umum

- lengkap

- sama sekali

- kompleks

- luas

- konsep

- Kondisi

- konfigurasi

- Terhubung

- Menghubungkan

- Koneksi

- Konektivitas

- terus-menerus

- pengawas

- Biaya

- hemat biaya

- bisa

- liputan

- penutup

- membuat

- dibuat

- kritis

- data

- didefinisikan

- kepadatan

- desainer

- desain

- terdeteksi

- Mati

- berbeda

- digital

- arah

- cacat

- Terbagi

- do

- turun

- dua

- selama

- setiap

- efisien

- menghapuskan

- tertanam

- muncul

- aktif

- memungkinkan

- memungkinkan

- berakhir

- peningkatan

- memastikan

- memastikan

- peralatan

- dll

- Eter (ETH)

- Bahkan

- berkembang

- contoh

- eksekusi

- menunjukkan

- ada

- diharapkan

- mahal

- ekspres

- memperpanjang

- luas

- tambahan

- mata

- kain

- palsu

- keluarga

- FAST

- lebih cepat

- salah

- Fitur

- bidang

- akhir

- Pertama

- flash

- keluwesan

- berikut

- Untuk

- dibentuk

- dari

- fungsi

- fungsionil

- fungsi

- fungsi

- lebih lanjut

- masa depan

- dikumpulkan

- generator

- Go

- baik

- Kelompok

- tangan

- Memiliki

- Kesehatan

- sehat

- membantu

- hirarki

- High

- lebih tinggi

- Namun

- HTTPS

- mengenali

- IEEE

- if

- Dampak

- mengimplementasikan

- penting

- in

- memasukkan

- termasuk

- Termasuk

- Meningkatkan

- meningkatkan

- menunjukkan

- sendiri-sendiri

- industri

- informasi

- Infrastruktur

- wawasan

- saat

- integrasi

- integritas

- Antarmuka

- interface

- intern

- terganggu

- ke

- IP

- IT

- Diri

- kunci

- dikenal

- Jalur

- besar

- Hukum

- lapisan

- Tingkat

- memanfaatkan

- leveraging

- siklus hidup

- pembatasan

- LINK

- link

- memuat

- logika

- lagi

- lepas

- kalah

- Rendah

- terbuat

- Utama

- pemeliharaan

- Pasar

- Cocok

- sesuai

- max-width

- Mungkin..

- ukur

- mekanisme

- Memori

- mode

- Memantau

- pemantauan

- monitor

- Monolitis

- lebih

- paling

- MTR

- beberapa

- harus

- Dekat

- kebutuhan

- New

- tidak

- simpul

- node

- normal

- jumlah

- of

- Penawaran

- on

- ONE

- hanya

- operasi

- optimasi

- or

- Lainnya

- di luar

- di luar

- Mengatasi

- paket

- dikemas

- paket

- pengemasan

- Paralel

- bagian

- khususnya

- Lulus

- path

- pola

- pola

- prestasi

- permanen

- tahap

- pin

- Nada

- plato

- Kecerdasan Data Plato

- Data Plato

- mungkin

- mungkin

- potensi

- berpotensi

- kekuasaan

- didukung

- diprediksi

- sebelumnya

- Sebelumnya

- probabilitas

- masalah

- Prosedur

- proses

- pengolahan

- Produk

- Produksi

- protokol

- memberikan

- menyediakan

- menyediakan

- kualitas

- Penilaian

- Baca

- baru-baru ini

- Sembuh

- menurunkan

- mengurangi

- register

- keandalan

- dapat diandalkan

- memperbaiki

- membutuhkan

- Persyaratan

- dihasilkan

- Risiko

- rute

- Run

- RX

- sama

- Save

- terukur

- skala

- penjadwalan

- aman

- segmen

- terpilih

- sensor

- Urutan

- serius

- melayani

- beberapa

- harus

- sisi

- Sinyal

- Tanda tangan

- Silikon

- YA

- mirip

- tunggal

- situasi

- lambat

- Melambat

- kecil

- larutan

- beberapa

- rentang

- khusus

- tertentu

- kecepatan

- stabil

- standar

- Bintang

- state-of-the-art

- Langkah

- Tangga

- penyimpanan

- menyimpan

- tersimpan

- Penyelarasan

- tersusun

- sukses

- seperti itu

- mendukung

- pendukung

- sistem

- sistem

- penargetan

- Teknologi

- Teknologi

- istilah

- uji

- pengujian

- tes

- bahwa

- Grafik

- Mereka

- kemudian

- Sana.

- Ini

- mereka

- ini

- Melalui

- waktu

- untuk

- puncak

- jalur

- lalu lintas

- transportasi

- dua

- TX

- usb

- menggunakan

- bekas

- Pengguna

- menggunakan

- berbagai

- Verifikasi

- melalui

- adalah

- Cara..

- webp

- BAIK

- Apa

- ketika

- yang

- sementara

- akan

- dengan

- dalam

- tanpa

- terburuk

- Menghasilkan

- zephyrnet.dll