Pengetsaan plasma mungkin merupakan proses yang paling penting dalam pembuatan semikonduktor, dan mungkin yang paling kompleks dari semua operasi fabrikasi di samping fotolitografi. Hampir setengah dari semua langkah luar biasa mengandalkan plasma, gas terionisasi energik, untuk melakukan pekerjaannya.

Meskipun transistor dan sel memori terus menyusut, para insinyur terus memberikan proses etsa yang andal.

“Untuk membuat chip secara berkelanjutan dengan presisi tingkat nano dan struktur biaya yang tepat, pembuat peralatan pabrik wafer perlu mendorong batasan fisika plasma, teknik material, dan ilmu data untuk memberikan solusi peralatan yang dibutuhkan,” kata Thomas Bondur, wakil presiden perusahaan untuk Pemasaran Grup Produk Etch di Penelitian Lam. Tidak ada tempat yang lebih jelas daripada etsa plasma, yang bekerja bahu-membahu dengan litografi untuk membuat fitur yang tepat dan berulang pada wafer.

Laporan ini membahas langkah-langkah etsa kunci dalam 3D NAND, DRAM, FET nanosheet, dan interkoneksi, dengan melihat ke depan pada perangkat 2D dan pemrosesan back-end beranggaran rendah. Industri ini juga mengejar bahan kimia etsa yang lebih berkelanjutan untuk mengurangi COXNUMX yang setara2 emisi dari fabs nya.

Bagi banyak pembuat alat, pemodelan proses memainkan peran penting dalam pengembangan proses etsa. Tujuannya adalah mempersingkat waktu pemasaran sambil mengurangi biaya wafer dan masker.

“Pengoptimalan proses etsa pada beberapa langkah tersulit dapat memakan waktu satu tahun atau lebih untuk menyelesaikannya,” kata Barrett Finch, direktur pemasaran senior di Lam Research. “Kami baru saja menyelesaikan beberapa pekerjaan simulasi proses dalam tiga minggu yang diperkirakan akan memakan waktu tiga bulan dengan menggunakan pengujian dan pengembangan berbasis silikon biasa.”

Ini bisa berjumlah ratusan ribu, atau bahkan jutaan dolar, hanya untuk biaya topeng dan wafer untuk produsen perangkat.

Dasar-dasar etsa

Proses etsa bekerja bergandengan tangan dengan litografi. Etsa biasanya didahului dengan pengendapan film (dengan epitaksi, pengendapan uap kimia atau fisik, dll.). Biasanya, a CVD film dilapisi dengan tahan foto dan kemudian diekspos melalui pola reticle (topeng) menggunakan litografi optik (UV 248nm atau 193nm, EUV 13.5nm). Resist development kemudian mengungkap polanya. Dalam ruang etsa plasma wafer tunggal, biasanya bahan kimia etsa dan ion membombardir dan menghapus film CVD di mana photoresist hilang (dalam tahanan nada positif). Setelah pengetsaan, tahan pengabuan, pembersihan bahan kimia basah, dan/atau pengetsaan basah untuk menghilangkan residu.

Proses etsa plasma secara kasar dapat dikelompokkan sebagai etsa dielektrik, silikon atau konduktor. Dielektrik seperti silikon dioksida dan silikon nitrida paling baik tergores menggunakan gas berfluorinasi sementara silikon dan lapisan logam bereaksi paling baik dengan bahan kimia klorin. Pada dasarnya ada tiga mode etsa kering - etsa ion reaktif, etsa plasma, dan etsa sputter (berkas ion). Proses etsa adalah tentang interaksi kompleks antara reaktan kimia, plasma, dan bahan wafer. Ketika bias RF diterapkan pada gas reaktif, elektron dan ion bermuatan positif membombardir wafer untuk menghilangkan (mengetsa) material secara fisik sementara spesies kimia dan radikal bebas bereaksi dengan material yang terpapar untuk membentuk produk sampingan yang mudah menguap. Etsa dapat berupa isotropik (bereaksi sama secara vertikal dan horizontal), anisotropik (hanya vertikal) atau di antara keduanya.

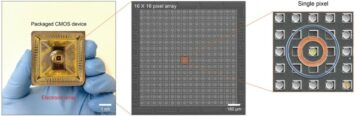

Gambar 1: Transisi dari finFET ke GAA mendorong persyaratan etsa selektif isotropik kritis. Sumber: Penelitian Lam

Yang paling diperhatikan oleh insinyur etsa metrik adalah laju etsa, kontrol profil, keseragaman (di seluruh wafer), dan selektivitas etsa, karena ini memengaruhi hasil dan produktivitas. Selektivitas etsa hanyalah rasio penghilangan bahan yang ingin Anda etsa relatif terhadap lapisan bawahnya – misalnya, SiO2 pada silikon. Selama etsa, juga menguntungkan untuk tidak menghilangkan terlalu banyak photoresist. Namun jika demikian, sering kali pola dipindahkan ke topeng keras (silikon dioksida, silikon nitrida, SiOC, TiN) sebelum dipindahkan ke film yang mendasarinya.

Spesifikasi selektivitas bervariasi dari 2:1 hingga 1,000:1 (pengetsaan sangat selektif). Dengan setiap node baru, spesifikasi ini semakin ketat. “Dengan NA EUV tinggi yang mulai menggantikan EUV biasa dalam empat tahun ke depan, fokusnya jauh lebih rendah, sehingga Anda tidak dapat lagi memaparkan photoresist tebal – dan maksud saya tebal 30 nanometer,” kata Philippe Bézard, insinyur R&D dry etch di imec. “Tapi Anda masih perlu membuat pola dengan ketebalan film yang sama di bawah. Jadi sekarang Anda meminta selektivitas yang jauh lebih tinggi dalam arti bahwa alih-alih 2:1 kita harus menjangkau lebih seperti 10:1, yang merupakan peningkatan selektivitas 4X hingga 5X secara tiba-tiba.”

Dari bukti konsep (POC) hingga produksi volume tinggi (HVM)

Bézard menjelaskan tiga fase pengembangan proses etch:

- Menentukan etsa, gas, lapisan bantu, dll., yang diperlukan untuk melakukan etsa;

- Mendemonstrasikan kinerja dalam menghapus film sepenuhnya dalam spesifikasi dengan keseragaman proses di satu wafer, dan

- Menentukan bagaimana proses dapat diulang di ribuan wafer di HVM dengan hasil tinggi dan penyimpangan kecil.

Biasanya, insinyur etsa dan integrasi yang terampil menangani dua fase pengembangan pertama. Fase ketiga mungkin sekali lagi memanfaatkan keahlian teknik, tetapi pembelajaran mesin dapat membantu.

“Pembelajaran mesin dan analisis data secara umum baru berguna pada fase ketiga,” ujarnya. “Ini sangat kuat karena memiliki akses ke banyak data dan dapat memahami sejuta hal kecil dan sederhana yang semuanya saling berinteraksi. Jadi bagi otak manusia untuk mencoba mencari tahu ini sangat sulit, tetapi lebih mudah diatur untuk program komputer. Tetapi dalam kasus di mana Anda memiliki aplikasi baru, materi baru sedang diukir atau integrasi baru, itu tidak menunjukkan peningkatan apa pun dibandingkan manusia.

Penggunaan ML juga berkaitan dengan biaya pembuatan karena ribuan wafer digunakan dalam fase tiga — setidaknya urutan besarnya lebih besar daripada yang digunakan dalam fase satu dan dua.

Barrett Finch, direktur senior Grup Produk Etch di Lam Research, menjelaskan pencarian jalur proses baru sebagai pengambilan bukti konsep dari aliran dan tata letak proses nominal dan mengembangkan satu atau lebih perangkat kerja pada wafer. POC ini kemudian ditransfer ke tim pengembangan produk di fab untuk meningkatkan proses dan meningkatkan hasil.

“Jumlah pekerjaan yang diperlukan untuk mengubah bukti konsep nominal menjadi produk dengan hasil yang layak sering diremehkan, dan ini menciptakan celah besar untuk profitabilitas,” kata Finch. “Pemodelan jendela proses berusaha untuk menutup celah ini dengan memperkenalkan variasi hebat ke dalam tahap awal pencarian jalan R&D.” Dia menyarankan bahwa DOE virtual dan analisis berbasis Monte Carlo di sejumlah parameter proses menguji POC dengan mensimulasikan variabilitas yang diharapkan.

“Pemodelan jendela proses dapat menjawab pertanyaan, 'CD atau tingkat variabilitas apa yang harus saya pertahankan untuk mencapai kinerja dan hasil perangkat minimum?' Kami telah menyelesaikan uji jendela proses virtual dengan lebih dari 1 juta wafer virtual dalam beberapa hari, yang tidak mungkin dicapai dalam kehidupan nyata,” katanya.

Berbagai parameter memengaruhi laju etsa, profil, dan selektivitas. Salah satu kuncinya adalah suhu. “Dampak efek termal dalam pemrosesan etsa terlihat oleh pelanggan kami saat mereka mengontrol laju etsa, selektivitas, dan profil etsa. Semua parameter ini dapat memengaruhi hasil perangkat dan produktivitas yang luar biasa, ”kata Benjamin Vincent, manajer senior untuk proses semikonduktor dan rekayasa integrasi di Lam Research. Dia berpendapat bahwa simulasi mungkin sangat membantu ketika langkah proses memiliki banyak kemungkinan konfigurasi (ruang proses besar), atau di mana hasil hilir dari langkah tersebut sangat tidak dapat diprediksi.

“Proses etsa bergantung pada suhu permukaan wafer, yang bergantung pada beberapa fluks panas — termasuk konduksi termal, energi tumbukan ion, reaksi permukaan, dan fluks panas radiasi plasma,” kata Alex Guermouche, manajer pemasaran produk di Esgee Technologies, a Perusahaan Riset Lam. “Akibatnya, model plasma perlu menggabungkan semua fitur fisika ini untuk secara akurat menggambarkan perubahan suhu pada permukaan wafer. Perangkat lunak simulasi proses dapat memodelkan berbagai atribut etsa, memungkinkan kami mendapatkan hasil etsa yang lebih baik dengan lebih cepat dan mempercepat kemampuan pelanggan untuk meningkatkan produksi atau mengoptimalkan hasil.”

Pengaturan waktu yang tepat dari proses etch

Dengan geometri yang lebih rapat dan film yang lebih tipis, ada kebutuhan untuk menyeimbangkan laju etsa dengan kontrol yang baik terhadap parameter operasi lainnya.

“Dengan aturan desain penyusutan, banyak proses etsa bergerak ke langkah proses etsa plasma yang sangat cepat yang membutuhkan kontrol yang sangat presisi dari semua input reaksi: daya, tekanan, kimiawi, dan suhu,” kata Finch, mencatat bahwa ada juga kecenderungan ke arah plasma yang dioptimalkan perilaku berdenyut untuk menghasilkan rasio ion-ke-netral tertentu, lalu menyapu produk sampingan. “Pemodelan lanjutan dari kondisi seperti itu akan sangat penting untuk memungkinkan penskalaan perangkat lebih lanjut.”

Produsen sistem etsa telah menggunakan perangkat lunak pemodelan selama beberapa waktu untuk mempercepat pengembangan simpul berikutnya atau hasil ramp. Ini tidak mengherankan, mengingat kompleksitas proses dan semua variabelnya.

“Tidak ada cukup waktu atau wafer yang cukup untuk mengeksekusi semua eksperimen proses yang memungkinkan saat mengembangkan teknologi simpul berikutnya,” kata Finch. “Jumlah kombinasi pengaturan peralatan etsa dapat mencapai jutaan, atau bahkan miliaran, dan pengembangan wafer kasar menggunakan semua kemungkinan proses tidak mungkin dilakukan.”

Tentu saja, semua model bagus diverifikasi pada chip yang sebenarnya. “Model yang akurat harus bersifat prediktif, dan harus memecahkan masalah yang ditargetkan yang ingin dipecahkan oleh pengguna,” kata Finch. “Setiap kali perubahan proses atau desain direkomendasikan berdasarkan pekerjaan simulasi, data fab aktual harus mencerminkan hasil rekomendasi. Dalam kasus kami, kami dapat secara akurat memprediksi efek perubahan proses menggunakan hasil berbasis model, dan dengan cepat menyelesaikan masalah proses dan pengembangan teknologi yang sulit.”

Pemasok alat juga bekerja pada proses etsa lanjutan untuk mengintegrasikan garis lebih dekat dan mengubah apa yang dulunya merupakan proses tingkat dua topeng (dua langkah litografi) menjadi satu untuk penyederhanaan proses dan pengurangan biaya.

“Alih-alih mengadaptasi perangkat keras yang ada untuk membuat pisau Swiss Army lebih lengkap, perusahaan memperkenalkan teknologi yang spesifik untuk aplikasi, seperti sistem baru untuk mengatasi masalah tip-to-tip,” kata Bézard. Tujuannya adalah untuk membuat dua garis saling berhadapan lebih dekat, yang saat ini melibatkan langkah pembuatan pola garis yang diikuti dengan topeng potong. "Apa Bahan Terapan dan lainnya yang diperkenalkan adalah cara etsa langsung ke arah horizontal." Proses semacam itu juga dapat melebar melalui lubang.

Langkah etsa untuk FET nanosheet

Langkah etsa paling kritis di lembar nano alur proses meliputi etsa gerbang dummy, etsa pilar anisotropik, etsa spacer isotropik, dan langkah pelepasan saluran. [1] Etsa profil melalui lapisan bergantian silikon dan SiGe bersifat anisotropik dan menggunakan bahan kimia terfluorinasi. Etsa spacer bagian dalam (lekukan) dan langkah pelepasan saluran dioptimalkan untuk menghilangkan SiGe dengan kehilangan silikon yang sangat rendah.

Langkah rilis saluran sangat penting. “Pelepasan nanosheet membutuhkan selektivitas yang sangat tinggi,” kata Bézard. “Kebanyakan nanosheet adalah silikon, kemudian silikon-germanium dan silikon. Anda memiliki lapisan bergantian, dan Anda perlu menghapus satu tanpa mengubah yang lain sama sekali.” Beberapa publikasi telah membahas melakukan etsa SiGe multi-langkah untuk mengurangi tekanan pada struktur yang disebabkan oleh langkah etsa tunggal.

Proses selanjutnya adalah pembentukan kontak yang selaras sendiri. “Di sini yang kami coba lakukan pada dasarnya adalah mengetsa silikon dioksida dan tidak menyentuh atau menyembunyikan silikon nitrida. Spesifikasi saat ini, katakanlah, reses 3nm, tetapi orang-orang meminta nol kerugian, ”kata Bézard. “Dalam hal ini kami bahkan tidak menggunakan kata selektivitas. Kami hanya berbicara tentang istirahat – dan tidak ada waktu istirahat.”

3D NAND

Untuk 3D NAND flash, jumlah lapisan terus bertambah dan mengharuskan adopsi beberapa tingkatan bertumpuk di masa mendatang, yang pada akhirnya menciptakan rangkaian vertikal perangkat bertumpuk. “Selain itu, ada banyak dorongan untuk menskalakan word line pitch atau vertikal/Z-pitch lapisan seiring bertambahnya jumlah lapisan untuk terus meningkatkan kepadatan bit,” kata Robert Clark, anggota senior staf teknis dan direktur teknologi di TEL. “Dari perspektif proses, proses etsa dan deposisi akan memerlukan peningkatan konstan untuk mengakomodasi rasio aspek yang semakin tinggi pada dimensi kritis yang semakin kecil yang membutuhkan penskalaan berkelanjutan.”

Clark menggambarkan perubahan di masa depan. “Melihat node lanjutan dari perangkat perangkap muatan dengan beberapa tingkatan, rekayasa tumpukan gerbang akan diperlukan untuk mencapai panjang gerbang yang lebih pendek, lebih banyak level per sel, dan meningkatkan efisiensi pemrograman — berpotensi melalui adopsi bahan high-k. Saluran konduktivitas yang lebih tinggi kemungkinan akan diperlukan untuk menggantikan saluran poli-Si di masa depan juga,” katanya.

Salah satu etsa paling kritis dalam 3D NAND melibatkan etsa dalam lubang sekitar 100nm melalui tumpukan oksida-nitrida multilapisan (200+ lapisan), yang dapat mencapai kedalaman 10µm. Bézard dari Imec mengatakan langkah etsa ini sangat mahal.

“Kami memiliki fenomena fisik yang terjadi, yang disebut efek pengisian daya diferensial,” katanya. “Dalam plasma kita memiliki elektron, ion, dan spesies netral untuk banyak menyederhanakan. Elektron bergerak ke segala arah, tetapi ion dipercepat tegak lurus terhadap permukaan. Jadi Anda memiliki muatan positif di bagian bawah lubang dan muatan negatif di bagian atas, dan Anda mendapatkan medan listrik yang mencoba menolak ion yang masuk.”

Akibatnya, diperlukan tingkat daya yang tinggi untuk mengetsa parit sepenuhnya. “Kami mencoba mempertahankan daya 30 hingga 50 gigawatt tanpa busur api, sehingga chuck harus dipoles dengan sangat baik dan diproduksi dengan baik,” katanya.

Etsa yang dalam juga menyebabkan tekanan yang perlu diminimalkan, terutama karena fabrikasi NAND multi-tingkat selanjutnya membutuhkan penipisan wafer, penjajaran yang tepat, dan ikatan hibrid ke tingkat berikutnya.

Proses lainnya

Tidak semua pembuat chip menghasilkan chip terdepan yang membutuhkan litografi EUV. Banyak fab memperluas proses litho dan etch 193nm mereka.

“Kami memiliki bahan SOC suhu tinggi yang baru saja kami mulai perkenalkan, yang memperluas kemampuan pembuatan polanya dan dapat menahan suhu yang lebih tinggi, baik digunakan sebagai lapisan bawah untuk lapisan CVD atau masker,” kata Brian Wilbur, direktur diversifikasi produk semikonduktor di Ilmu Pembuatan Bir.

BEOL untuk garis logam yang paling ketat diharapkan mengalami transisi dramatis dari skema integrasi damaskus ganda ke pengendapan subtraktif dan etsa interkoneksi selain tembaga. Di sini, dua logam — rutenium dan molibdenum — telah dikembangkan paling menyeluruh. Namun, molibdenum lebih cenderung teroksidasi selama etsa, membuatnya lebih kompatibel dengan skema damascene ganda. Ruthenium adalah logam mulia sehingga tidak memiliki masalah korosi yang sama, tetapi harganya lebih mahal.

Struktur perangkat juga menjadi tidak toleran kesalahan penempatan tepi. Skema baru untuk self-alignment dari lapisan ke lapisan dan antara vias dan garis akan dibutuhkan, menurut Clark dari TEL. “Implementasi pertama mungkin untuk hal-hal seperti baris kata yang terkubur dalam DRAM, dan lapisan logam MOL pitch kecil untuk logika di mana diperlukan stabilitas termal yang lebih tinggi serta resistivitas yang lebih rendah atau logam tanpa liner.”

Perkembangan generasi selanjutnya

Jangka panjang, industri idealnya akan beralih ke proses back-end anggaran termal yang lebih rendah (mendekati 300°C dari 400°C) untuk mengintegrasikan perangkat ke dalam lapisan interkoneksi back-end.

“Industri memiliki kebutuhan nyata untuk mulai membuat perangkat menjadi lebih banyak lapisan,” kata Clark dari TEL. “Itu berarti kita membutuhkan perangkat memori dan logika yang dibangun di dalam BEOL dengan anggaran termal BEOL.”

Sejauh ini, perangkat yang dibuat menggunakan oksida semikonduktor tampak menjanjikan, baik untuk mengintegrasikan perangkat memori ke dalam aliran logika BEOL, atau untuk membangun susunan CMOS di atas susunan memori dalam DRAM.

Pergeseran substansial lainnya melibatkan integrasi bahan 2D, yang sudah mulai diuji oleh rumah penelitian dan pembuat chip terkemuka. Proses etsa untuk bahan seperti tungsten disulfida atau molibdenum disulfida sedang dipertimbangkan. Film-film tersebut terdiri dari satu lapisan material sehingga mengembangkan proses yang luar biasa untuk mengintegrasikannya sangatlah menantang.

Keberlanjutan

Pembuat chip dan pemasok bahan sedang mengejar bahan kimia alternatif untuk mengurangi emisi karbon. Dalam etsa, penyebab utamanya adalah gas berfluorinasi dengan potensi pemanasan global yang tinggi.

“Alasan mengapa Anda memiliki PFOS (perfluorooctane sulfonic acid), yang bermasalah, adalah karena molekulnya sangat stabil,” kata Bézard dari imec. “Reaksi cahaya atau kimiawi di atmosfer tidak cukup untuk memecahnya.”

Ia mengatakan sejumlah campuran gas alternatif dengan kandungan oksigen lebih tinggi lebih mudah terdisosiasi dan memiliki GWP lebih rendah. “Namun, setiap kandidat harus memberikan kinerja yang baik atau bahkan lebih tinggi untuk memulai.”

Tapi keberlanjutan bukanlah tantangan etsa atau pengendapan. Ini adalah tantangan industri holistik mulai dari litografi hingga pengemasan, di mana dampak material baru memengaruhi keseluruhan pemrosesan perangkat.

Referensi

1.K.Derbyshire, “Apa yang Berbeda dari Transistor Generasi Berikutnya”, Teknik Semikonduktor, 20 Oktober 2022.

Berita terkait

Etch Sangat Selektif Diluncurkan Untuk Chip Generasi Berikutnya

Manufaktur struktur 3D akan memerlukan kontrol tingkat atom dari apa yang dihapus dan apa yang tetap di wafer.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoAiStream. Kecerdasan Data Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Beli dan Jual Saham di Perusahaan PRE-IPO dengan PREIPO®. Akses Di Sini.

- Sumber: https://semiengineering.com/etch-processes-push-toward-higher-selectivity-cost-control/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 000

- 1

- 10

- 13

- 20

- 2022

- 2D

- Bahan 2D

- 30

- 3d

- 50

- a

- kemampuan

- Sanggup

- Tentang Kami

- mempercepat

- dipercepat

- mengakses

- menampung

- menyelesaikan

- Menurut

- tepat

- akurat

- di seluruh

- sebenarnya

- alamat

- Adopsi

- maju

- menguntungkan

- mempengaruhi

- lagi

- tujuan

- alex

- Semua

- Membiarkan

- sudah

- juga

- alternatif

- jumlah

- an

- analisis

- dan

- Lain

- menjawab

- Apa pun

- muncul

- Aplikasi

- khusus aplikasi

- terapan

- ADALAH

- Tentara

- susunan

- AS

- penampilan

- membantu

- At

- Suasana

- atribut

- jauh

- Back-end

- Saldo

- berdasarkan

- Pada dasarnya

- BE

- Balok

- karena

- menjadi

- menjadi

- sebelum

- Awal

- makhluk

- di bawah

- Benyamin

- TERBAIK

- Lebih baik

- antara

- prasangka

- Besar

- miliaran

- Bit

- kedua

- Bawah

- batas-batas

- Otak

- Istirahat

- Brian

- brute force

- anggaran belanja

- Anggaran

- Bangunan

- dibangun di

- tapi

- by

- bernama

- CAN

- calon

- karbon

- emisi karbon

- yang

- kasus

- kasus

- CD

- Sel

- menantang

- menantang

- Ruang

- perubahan

- Perubahan

- Saluran

- saluran

- biaya

- dibebankan

- beban

- pengisian

- kimia

- bahan kimia

- kimia

- Keripik

- Pembersihan

- Penyelesaian

- rapat

- lebih dekat

- kombinasi

- Perusahaan

- perusahaan

- cocok

- lengkap

- Lengkap

- kompleks

- kompleksitas

- komputer

- konsep

- Kondisi

- daya konduksi

- konduktor

- dianggap

- konstan

- kontak

- Konten

- terus

- terus

- terus

- kontrol

- Tembaga

- Timeline

- korosi

- Biaya

- pengurangan biaya

- Biaya

- bisa

- Tentu saja

- membuat

- menciptakan

- membuat

- kritis

- terbaru

- Sekarang

- pelanggan

- Memotong

- data

- analisis data

- ilmu data

- Hari

- mendalam

- menyampaikan

- kepadatan

- tergantung

- dijelaskan

- Mendesain

- dikembangkan

- berkembang

- Pengembangan

- alat

- Devices

- berbeda

- sulit

- ukuran

- arah

- langsung

- Kepala

- dibahas

- diversifikasi

- do

- tidak

- dolar

- turun

- dramatis

- mendorong

- kering

- selama

- setiap

- Awal

- mudah

- efek

- efek

- efisiensi

- antara

- Listrik

- elektron

- emisi

- memungkinkan

- insinyur

- Teknik

- Insinyur

- cukup

- sama

- peralatan

- lengkap

- Setara

- terutama

- penting

- dasarnya

- dll

- Bahkan

- akhirnya

- Setiap

- rewel

- Memeriksa

- menjalankan

- ada

- diharapkan

- mahal

- eksperimen

- keahlian

- terkena

- memperpanjang

- sangat

- menghadapi

- jauh

- FAST

- lebih cepat

- Fitur

- beberapa

- bidang

- Angka

- Film

- bioskop

- Pertama

- flash

- aliran

- Mengalir

- Fokus

- diikuti

- berikut

- Untuk

- kekuatan

- bentuk

- pembentukan

- Depan

- empat

- Gratis

- dari

- sepenuhnya

- lebih lanjut

- masa depan

- celah

- GAS

- Umum

- menghasilkan

- mendapatkan

- diberikan

- Aksi

- pemanasan global

- tujuan

- baik

- besar

- Kelompok

- Tumbuh

- tumbuh

- Setengah

- menangani

- Sulit

- Perangkat keras

- Memiliki

- he

- bermanfaat

- di sini

- High

- Yield tinggi

- lebih tinggi

- sangat

- Lubang

- Lubang

- holistik

- Horisontal

- rumah

- Seterpercayaapakah Olymp Trade? Kesimpulan

- Namun

- HTTPS

- manusia

- Manusia

- Ratusan

- Hibrida

- i

- Dampak

- mustahil

- memperbaiki

- ditingkatkan

- perbaikan

- in

- memasukkan

- Termasuk

- masuk

- menggabungkan

- meningkatkan

- industri

- input

- contoh

- sebagai gantinya

- mengintegrasikan

- Mengintegrasikan

- integrasi

- berinteraksi

- interaksi

- interkoneksi

- ke

- memperkenalkan

- masalah

- IT

- NYA

- jpg

- hanya

- kunci

- Melarikan diri

- besar

- lebih besar

- lapisan

- lapisan

- tata ruang

- terkemuka

- pengetahuan

- paling sedikit

- Tingkat

- adalah ide yang bagus

- Hidup

- 'like'

- Mungkin

- baris

- baris

- LITO

- sedikit

- logika

- lagi

- melihat

- lepas

- Lot

- Rendah

- mesin

- Mesin belajar

- terbuat

- Utama

- memelihara

- membuat

- Pembuat

- Membuat

- manajer

- diproduksi

- Pabrikan

- pabrik

- banyak

- Pasar

- Marketing

- Direktur Pemasaran

- masker

- bahan

- bahan

- max-width

- Mungkin..

- berarti

- cara

- anggota

- Memori

- logam

- Logam

- Metrik

- mungkin

- juta

- jutaan

- minimum

- hilang

- model

- pemodelan

- model

- mode

- MOL

- molekul

- bulan

- lebih

- paling

- pindah

- bergerak

- banyak

- beberapa

- hampir

- Perlu

- dibutuhkan

- kebutuhan

- negatif

- Netral

- New

- berikutnya

- tidak

- mulia

- simpul

- node

- sekarang

- jumlah

- Oktober

- of

- sering

- on

- sekali

- ONE

- hanya

- operasi

- Operasi

- optimasi

- Optimize

- dioptimalkan

- or

- urutan

- Lainnya

- Lainnya

- kami

- di luar

- lebih

- Oksigen

- pengemasan

- parameter

- tertentu

- khususnya

- pola

- Konsultan Ahli

- melakukan

- prestasi

- melakukan

- mungkin

- perspektif

- tahap

- gejala

- Philippe

- fisik

- Secara fisik

- Fisika

- Pilar

- Nada

- sangat penting

- Plasma

- plato

- Kecerdasan Data Plato

- Data Plato

- memainkan

- PoC

- positif

- kemungkinan

- mungkin

- mungkin

- potensi

- berpotensi

- kekuasaan

- kuat

- perlu

- Ketelitian

- meramalkan

- presiden

- tekanan

- Masalah

- masalah

- proses

- proses

- pengolahan

- menghasilkan

- Produk

- pengembangan produk

- Produksi

- produktifitas

- Produk

- Profil

- profil

- profitabilitas

- program

- Pemrograman

- menjanjikan

- bukti

- bukti konsep

- publikasi

- Dorong

- pertanyaan

- segera

- R & D

- Lereng

- jarak

- Penilaian

- Tarif

- perbandingan

- mencapai

- Bereaksi

- reaksi

- Reaksi

- nyata

- kehidupan nyata

- alasan

- baru-baru ini

- Rekomendasi

- direkomendasikan

- menurunkan

- mengurangi

- pengurangan

- mencerminkan

- reguler

- melepaskan

- dapat diandalkan

- mengandalkan

- pemindahan

- menghapus

- Dihapus

- menghapus

- berulang

- ulang

- menggantikan

- melaporkan

- membutuhkan

- wajib

- Persyaratan

- membutuhkan

- penelitian

- mengakibatkan

- Hasil

- Mengungkapkan

- benar

- ROBERT

- Peran

- gulungan

- kira-kira

- aturan

- Run

- Tersebut

- sama

- mengatakan

- Skala

- skala

- skema

- Ilmu

- Mencari

- terlihat

- selektif

- semikonduktor

- senior

- rasa

- pengaturan

- beberapa

- bergeser

- harus

- Silikon

- Sederhana

- menyederhanakan

- hanya

- simulasi

- tunggal

- terampil

- kecil

- So

- Perangkat lunak

- Solusi

- MEMECAHKAN

- beberapa

- di suatu tempat

- sumber

- Space

- tertentu

- spesifikasi

- spesifikasi

- kecepatan

- Stabilitas

- stabil

- ditumpuk

- Tumpukan

- Staf

- magang

- awal

- mulai

- Langkah

- Tangga

- Masih

- tekanan

- struktur

- Kemudian

- besar

- seperti itu

- tiba-tiba

- cukup

- Menyarankan

- pemasok

- Permukaan

- mengherankan

- Keberlanjutan

- berkelanjutan

- Sapu

- Swiss

- sistem

- Mengambil

- pengambilan

- Berbicara

- ditargetkan

- tim

- Teknis

- Teknologi

- Teknologi

- Pengembangan Teknologi

- istilah

- uji

- pengujian

- tes

- dari

- bahwa

- Grafik

- Masa depan

- mereka

- Mereka

- kemudian

- Sana.

- panas

- Ini

- mereka

- hal

- Ketiga

- ini

- sepenuhnya

- ribuan

- tiga

- Melalui

- tingkat

- lebih ketat

- waktu

- waktu

- untuk

- bersama

- ton

- NADA

- terlalu

- puncak

- menyentuh

- terhadap

- ditransfer

- Mengubah

- transisi

- kecenderungan

- mencoba

- dua

- khas

- khas

- pokok

- tak terduga

- atas

- ke atas

- us

- menggunakan

- bekas

- Pengguna

- menggunakan

- Penggunaan

- diverifikasi

- vertikal

- secara vertikal

- sangat

- melalui

- giat

- Wakil Presiden

- vincent

- maya

- volatil

- ingin

- ingin

- adalah

- Cara..

- we

- minggu

- BAIK

- Apa

- ketika

- apakah

- yang

- sementara

- seluruh

- mengapa

- akan

- dengan

- dalam

- tanpa

- Word

- Kerja

- kerja

- bekerja

- akan

- tahun

- tahun

- Menghasilkan

- penurut

- hasil panen

- kamu

- zephyrnet.dll

- nol