Makalah teknis berjudul “Paralelisme Berpusat Data Besar-besaran di Era Chiplet” diterbitkan oleh para peneliti di Universitas Princeton.

Abstrak:

“Secara tradisional, aplikasi paralel secara masif dijalankan pada sistem terdistribusi, dimana node komputasi berada pada jarak yang cukup jauh sehingga skema paralelisasi harus meminimalkan komunikasi dan sinkronisasi untuk mencapai skalabilitas. Memetakan beban kerja yang intensif komunikasi ke sistem terdistribusi memerlukan partisi masalah yang rumit dan pra-pemrosesan kumpulan data. Dengan tren yang didorong oleh AI saat ini, yaitu memiliki ribuan prosesor yang saling terhubung per chip, terdapat peluang untuk memikirkan kembali beban kerja yang mengalami hambatan komunikasi ini. Kemacetan ini sering kali timbul dari traversal struktur data, yang menyebabkan akses memori tidak teratur dan lokalitas cache yang buruk.

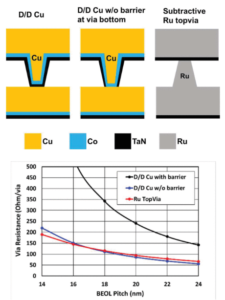

Karya terbaru telah memperkenalkan skema paralelisasi berbasis tugas untuk mempercepat traversal grafik dan beban kerja renggang lainnya. Penjelajahan struktur data dibagi menjadi beberapa tugas dan disalurkan ke seluruh unit pemrosesan (PU). Dalorex mendemonstrasikan skalabilitas tertinggi (hingga ribuan PU dalam satu chip) dengan menempatkan seluruh kumpulan data di dalam chip, tersebar di seluruh PU, dan menjalankan tugas di PU yang datanya bersifat lokal. Namun, hal ini juga menimbulkan pertanyaan tentang bagaimana menskalakan kumpulan data yang lebih besar ketika semua memori ada di dalam chip, dan berapa biayanya.

Untuk mengatasi tantangan ini, kami mengusulkan arsitektur terukur yang terdiri dari grid chiplet Data-Centric Reconfigurable Array (DCRA). Konfigurasi ulang waktu paket memungkinkan pembuatan produk chip yang mengoptimalkan metrik target yang berbeda, seperti waktu penyelesaian, energi, atau biaya, sementara konfigurasi ulang perangkat lunak menghindari kejenuhan jaringan saat menskalakan ke jutaan PU di banyak paket chip. Kami mengevaluasi enam aplikasi dan empat kumpulan data, dengan beberapa konfigurasi dan teknologi memori, untuk memberikan analisis terperinci mengenai kinerja, daya, dan biaya eksekusi data lokal dalam skala besar. Paralelisasi Breadth-First-Search kami dengan RMAT-26 di satu juta PU mencapai 3323 GTEPS.”

Temukan teknisnya kertas di sini. Diterbitkan April 2023 (pracetak).

Orenes-Vera, Marcelo, Esin Tureci, David Wentzlaf, dan Margaret Martonosi. “Paralelisme Berpusat Data Besar-besaran di Era Chiplet.” arXiv preprint arXiv: 2304.09389 (2023).

terkait

Mini-Consortia Membentuk Sekitar Chiplets

Pasar chiplet komersial masih jauh dari jangkauan, namun perusahaan-perusahaan mulai memulai lebih awal dengan kemitraan yang lebih terbatas.

Risiko Keamanan Chiplet Diremehkan

Besarnya tantangan keamanan pada chiplet komersial sangatlah menakutkan.

Perlombaan Menuju Chiplet Pengecoran Campuran

Tantangan dalam merakit chiplet dari pabrik pengecoran logam yang berbeda baru saja mulai muncul.

Pertimbangan Desain Dan Kemajuan Terkini Dalam Chiplet (UC Berkeley/Universitas Peking)

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Sumber: https://semiengineering.com/data-centric-reconfigurable-array-dcra-chiplets-princeton/

- :adalah

- :Di mana

- $NAIK

- 2023

- a

- mempercepat

- Mencapai

- di seluruh

- alamat

- kemajuan

- Semua

- juga

- an

- analisis

- dan

- aplikasi

- April

- arsitektur

- ADALAH

- sekitar

- susunan

- AS

- At

- Awal

- tapi

- by

- Cache

- Menyebabkan

- tantangan

- keping

- komersial

- Komunikasi

- Perusahaan

- rumit

- tersusun

- komputasi

- pertimbangan

- Biaya

- membuat

- terbaru

- data

- kumpulan data

- David

- menunjukkan

- terperinci

- berbeda

- Jauh

- didistribusikan

- sistem terdistribusi

- Awal

- memungkinkan

- energi

- cukup

- Seluruh

- Era

- mengevaluasi

- mengeksekusi

- eksekusi

- Untuk

- empat

- dari

- mendapatkan

- grafik

- kisi

- Memiliki

- memiliki

- paling tinggi

- horison

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- Namun

- HTTPS

- in

- saling berhubungan

- ke

- diperkenalkan

- IT

- hanya

- lebih besar

- Terbatas

- lokal

- banyak

- pemetaan

- pasar

- secara besar-besaran

- Memori

- Metrik

- juta

- jutaan

- lebih

- jaringan

- node

- of

- on

- Kesempatan

- Optimize

- or

- Lainnya

- kami

- paket

- kertas

- Paralel

- kemitraan

- Beijin

- prestasi

- plato

- Kecerdasan Data Plato

- Data Plato

- miskin

- kekuasaan

- pangeran

- Masalah

- pengolahan

- prosesor

- Produk

- mengusulkan

- memberikan

- diterbitkan

- Pertanyaan

- Ras

- menonjol

- Mencapai

- baru

- membutuhkan

- peneliti

- risiko

- Skalabilitas

- terukur

- Skala

- skala

- tersebar

- skema

- keamanan

- risiko keamanan

- beberapa

- tunggal

- ENAM

- Perangkat lunak

- membagi

- awal

- Masih

- struktur

- seperti itu

- sinkronisasi

- sistem

- target

- tugas

- Teknis

- Teknologi

- bahwa

- Grafik

- Sana.

- Ini

- ini

- ribuan

- berjudul

- untuk

- terhadap

- kecenderungan

- unit

- universitas

- adalah

- we

- Apa

- yang

- sementara

- dengan

- bekerja

- zephyrnet.dll