Chiplet mulai mempengaruhi desain chip, meskipun chiplet belum menjadi produk mainstream dan belum ada pasar komersial untuk jenis IP yang diperkeras ini.

Terdapat diskusi yang sedang berlangsung mengenai manajemen siklus hidup silikon, cara terbaik untuk mengkarakterisasi dan menghubungkan perangkat-perangkat ini, dan cara menangani masalah seperti penuaan yang tidak merata dan ketidaksesuaian termal. Selain itu, upaya besar sedang dilakukan untuk meningkatkan kemampuan observasi chiplet seiring waktu, sesuatu yang sangat penting karena perangkat ini digunakan dalam aplikasi yang kritis terhadap keselamatan dan misi-kritis.

Semua masalah ini perlu dipecahkan untuk memungkinkan adopsi secara luas, dan industri chip telah menyadari bahwa perlambatan Hukum Moore dikombinasikan dengan ukuran reticle yang tetap akan memerlukan perubahan dalam cara chip dirancang, diproduksi, dan dikemas. Secara fisik tidak mungkin untuk memasukkan semua fungsi yang diperlukan untuk banyak aplikasi ke dalam satu SoC, dan tujuannya sekarang adalah untuk pendekatan yang teratur, dapat diprediksi, dan berulang untuk memilah banyak komponen ini. Secara teori, hal ini akan memungkinkan perangkat lebih mudah disesuaikan, mempercepat waktu pemasaran, dan menghindari penskalaan mahal pada komponen yang tidak memerlukannya, seperti fungsi analog.

Namun, untuk mencapai tujuan tersebut diperlukan penyelesaian beberapa permasalahan yang rumit dan pelik. Di satu sisi, hal ini memerlukan kemampuan observasi, pemantauan, dan analisis yang jauh lebih baik terhadap apa yang dimasukkan ke dalam sebuah paket. Sedangkan konsep memasukkan banyak chip ke dalam satu paket sudah ada sejak tahun 1990-an modul multi-chip, dengan chiplet, cetakan biasanya lebih kecil dan tipis, dan dinamika cara mengkarakterisasi, menguji, dan mengamatinya telah berubah secara signifikan.

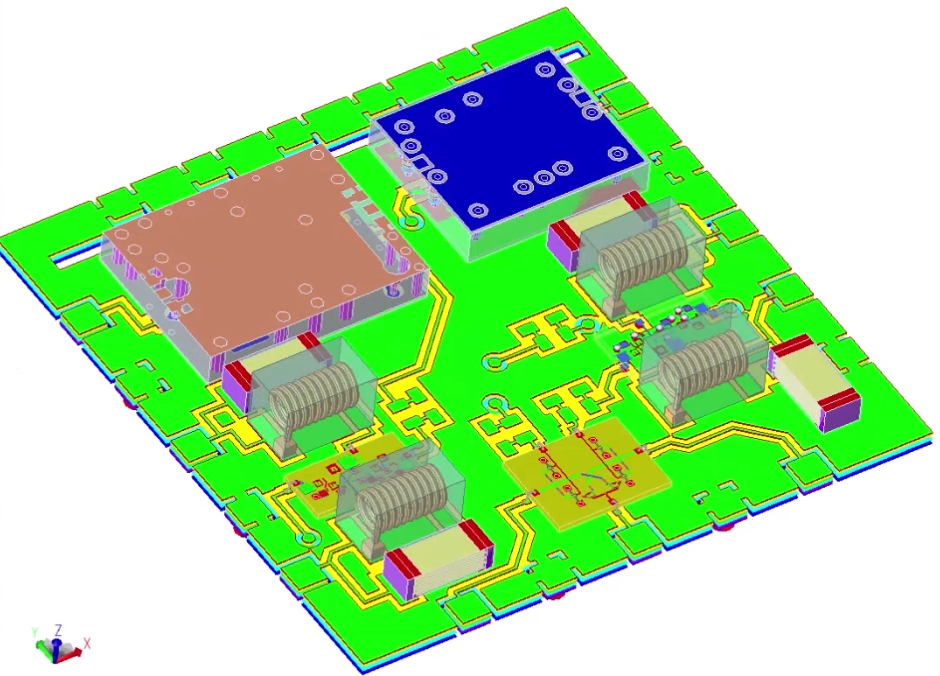

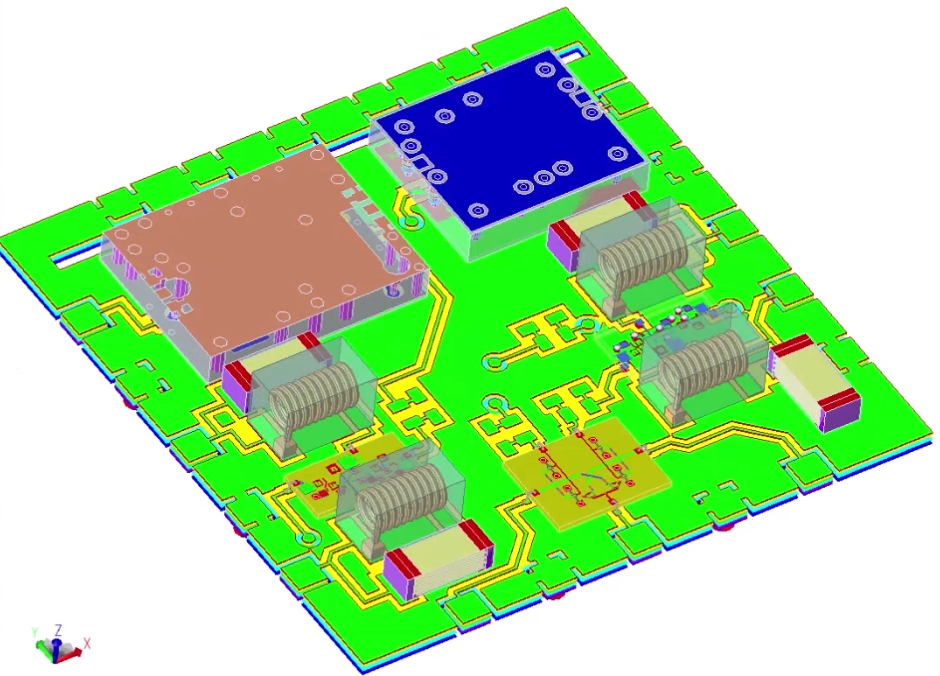

“Secara historis kami menyebut modul multi-chip ini, yang sangat populer di dunia nirkabel saat ini,” kata Nilesh Kamdar, pemimpin portofolio RF/microwave di Penglihatan kunci. “Anda dapat menggunakan smartphone apa pun, dan bagian nirkabel dari smartphone tersebut adalah modul front-end yang terdiri dari 20 hingga 30 chip yang disatukan dalam ruang kecil yang lebih kecil dari kuku. Hal ini telah terjadi di industri ini setidaknya selama satu dekade, atau mungkin lebih lama lagi. Selain itu, beberapa masalah dirgantara dan frekuensi tinggi lainnya memerlukan integrasi semacam ini, jadi kami telah melakukan hal ini di masa lalu.”

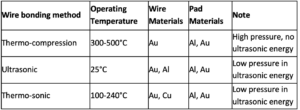

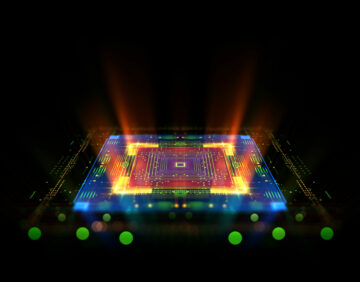

Gambar 1. Tata letak modul RF multi-chip ditunjukkan pada PathWave ADS Keysight. Sumber: Keysight

Pergeseran besar yang kini sedang berlangsung melibatkan penerapan yang lebih luas untuk pendekatan ini, serta perbaikan dalam desain chiplet, dan cara standar untuk menghubungkan, menguji, dan mengukur apa yang terjadi di dalam chiplet itu sendiri, serta paket canggih yang mengelilinginya.

“Otomotif adalah contoh bagus tentang apa yang berubah,” kata Kamdar. “Pada konferensi baru-baru ini, seorang wakil presiden dari OEM besar berbicara tentang tidak adanya kemampuan untuk mengambil pusat data dan meletakkannya di kursi belakang mobil, karena itulah yang diperlukan untuk memiliki kendaraan otonom saat ini. Jika Anda melakukan lebih banyak integrasi — dan jika Anda entah bagaimana membuat papan tersebut menghilang, dan semuanya terjepit — mungkin secara vertikal kita dapat memasukkannya ke kursi belakang mobil. Ada banyak kasus penggunaan serupa. Kebutuhan daya untuk chiplet mungkin lebih rendah jika Anda mempertimbangkan pusat data fisik. Ada banyak manfaatnya, dan itulah yang mendorong chiplet saat ini.”

Namun, perubahan-perubahan ini tampaknya rumit, dan industri mungkin perlu kembali memikirkan hal ini. “Membuat chiplet dalam skala besar adalah model yang berbeda sehingga kita semua perlu menilai kembali keterampilan kita,” katanya. “Kita perlu menilai kembali bagaimana organisasi dibentuk dan bagaimana arsitektur terjadi. Kita perlu menilai kembali peran perancang sistem. Mereka mungkin memandang sesuatu dengan cara yang berbeda, dan mungkin berkata, 'Saya seorang perancang sistem. Saya merancang spesifikasi untuk sistem. Saya memecahnya menjadi komponen tingkat yang lebih kecil, IC individual, dan mendistribusikan spesifikasinya. Saya pergi dan kembali enam bulan kemudian dan melihat bagaimana keadaan semua orang.' Mungkin itu bahkan tidak mungkin. Mungkin ada beberapa perancang sistem yang perlu ada di seluruh rantai. Percakapan seperti itulah yang perlu dilakukan. Di kalangan pemain terbesar di industri ini, pembicaraan mengenai hal tersebut sudah terjadi, namun tidak di semua tempat.”

Jumlah interaksi potensial dalam konteks desain multi-chiplet sangatlah signifikan, dan dalam banyak kasus, bersifat spesifik desain. “Jika Anda percaya pada multi-die, jika Anda percaya pada chiplet, Anda harus percaya bahwa hal itu hanya akan memperburuk masalah [desain dan integrasi] secara keseluruhan,” kata Shekhar Kapoor, direktur senior manajemen lini produk untuk perusahaan tersebut. Grup Synopsys EDA. “Chiplet akan datang dari banyak tempat, banyak sumber. Akan ada banyak pilihan, banyak pilihan untuk semua orang. Masalah terbesar adalah penggunaan saat ini mengenai semua ini. Perusahaan-perusahaan besar melakukan ini dengan cara yang dipesan lebih dahulu dan disesuaikan. Namun jika Anda menerapkan standardisasi secara luas, bagaimana Anda tahu bahwa chiplet yang masuk akan cocok dengan lingkungan, pada produk yang Anda coba buat?”

Meskipun fokus pada standar seperti UCIe dan Bunch of Wires, masih terdapat perbedaan dalam hal bagaimana masing-masing chiplet dikarakterisasi dalam konteks suatu sistem. “Bagaimana kamu tahu profilnya? Di situlah lebih banyak pemantauan akan dilakukan, yang hampir seperti tanda tangan,” kata Kapoor. “Anda dapat membacanya dan mengetahui apakah ini ideal untuk lingkungan Anda. Mengingat industri ini bergerak menuju pemberdayaan chiplet yang lebih banyak, hal ini akan menjadi pertimbangan utama. Semakin banyak persyaratan yang muncul, semakin banyak standar yang muncul, sehingga Anda dapat melihat apakah sesuatu akan sesuai atau tidak.”

Ada juga tantangan lain yang harus diatasi.

“Dengan chiplet, semua sinyal berkecepatan tinggi ada dalam paketnya, sehingga kemampuan observasi menjadi jauh lebih menantang,” kata Sue Hung Fung, manajer pemasaran lini produk untuk UCIe di Irama. “Hal ini dapat dilakukan melalui pemeriksaan link error, scan mata, BiST, dan lain-lain, guna mendapatkan unknown good die (KGD). Semua metode pengujian dibangun berdasarkan hal ini. Selain itu, memiliki monitor yang baik untuk kesehatan tautan akan sangat bermanfaat, dan akan ada proposal baru dan berbeda dari vendor yang berbeda.”

Kuncinya adalah memantau kualitas sinyal dalam konteks komponen lainnya dalam sebuah paket, yang menjadi lebih sulit karena semakin banyak fungsi yang dipilah ke dalam chiplet.

“Bisakah kita memantau sinyal dan kualitasnya selama transfer data? Teknik pelatihan dilakukan sebelum mode misi untuk meningkatkan ketahanan transfer data,” kata Hung Fung. “Pelatihan ulang tidak diinginkan karena dapat menyebabkan gangguan data. Kita harus dapat terus memantau dan melaporkan setiap jalur serta mendeteksi kejadian apa pun yang dapat menyebabkan kegagalan sebelum kegagalan terjadi. Pencegahan kegagalan sistem dan perbaikan kegagalan tersebut mencakup pemetaan ulang jalur yang berlebihan atau metode perbaikan lainnya untuk mendeteksi jalur yang sedikit rusak. Pelatihan dan pemantauan berkelanjutan terhadap sinyal chiplet internal ini merupakan tantangan dalam menganalisis perilaku tautan.”

Kelompok kerja UCIe berupaya untuk menstandardisasi sebagian dari kemampuan observasi ini untuk memiliki ekosistem tautan terbuka. Namun menambahkan kemampuan observasi dan pemantauan juga dapat sangat bervariasi menurut segmen vertikal.

Randy Fish, direktur manajemen lini produk untuk Synopsys EDA Group, menjelaskan bahwa karena tidak ada pendekatan standar dan sedikit pemasok komersial untuk solusi observasi, hampir semua solusi telah dibuat khusus. “Jika Anda masuk ke salah satu semifinal terkemuka, mereka melakukan sesuatu,” katanya. “Pertanyaannya adalah, apakah ada fungsi di sekitar multi-die yang akan memaksa kita untuk melakukan standarisasi agar memiliki infrastruktur yang kohesif atau koheren untuk pemantauan dan debug — pada dasarnya untuk melihat apa yang terjadi terutama jika Anda mendapatkan banyak die dari banyak pemasok. Beberapa solusi multi-die diterapkan pada otomotif, dan mereka sangat peduli dengan hal-hal seperti penuaan dan apa yang terjadi pada die tersebut. Dan seperti yang kita tahu, ini adalah node tingkat lanjut. Ini tidak seperti Anda memiliki 6 teknologi matang berusia 10 tahun. Ini adalah node tingkat lanjut yang tidak memiliki sejarah panjang. Oleh karena itu, ada sejumlah faktor yang menyebabkan hal ini terjadi.”

Chiplets juga memperkenalkan beberapa kontras yang menarik. Kamdar dari Keysight mencatat bahwa dalam panel CEO baru-baru ini, salah satu panelis mengatakan chiplet memiliki dikotomi yang unik. “Di satu sisi, setiap chiplet bisa menjadi IP independen yang dapat Anda peroleh dari vendor IP dan mengintegrasikannya ke dalam sistem Anda dengan biaya yang relatif rendah dan relatif mudah. Namun, seluruh tumpukan yang Anda coba bangun tiba-tiba memaksa Anda untuk mengetahui segalanya. Sebelumnya, Anda bisa saja berkata, 'Saya butuh enam hal. Saya akan membeli lima dari vendor IP dan mereka akan mencari tahu apa yang dibutuhkannya. Saya akan fokus pada satu hal.' Namun sekarang Anda mungkin tidak berhasil melakukan hal itu. Anda mungkin sebenarnya perlu mengetahui cara melakukan keenam hal tersebut, dan mencari tahu bagaimana semua itu terjadi karena kompleksitas masalahnya semakin meningkat. Hal ini mungkin memaksa industri untuk awalnya hanya mengizinkan pemain besar untuk mengetahui hal ini. Mungkin diperlukan waktu lebih lama bagi vendor kecil untuk bisa sukses di lingkungan ini.”

Namun demikian, diperlukan lebih dari satu perusahaan untuk mempercepat integrasi dan adopsi chiplet.

“Keysight menghadiri Simposium TSMC yang merupakan acara yang lebih bersifat publik, dan sebagai tindak lanjutnya ada lokakarya yang hanya dihadiri oleh mitra yang tergabung dalam 3D Fabric Alliance,” kata Kamdar. “TSMC memulai dan mengakhiri sepanjang hari dengan membicarakan tentang bagaimana kita semua perlu bekerja sama dalam hal ini, yang juga diamini oleh peserta lain, termasuk AMD dan Qualcomm. Pembicara dari kedua perusahaan mengatakan tidak ada satu pun perusahaan EDA yang tahu cara mengatasi masalah chiplet sendiri. Seluruh industri harus bekerja sama.”

Tantangan teknis

Masalah utama lainnya dengan chiplet adalah pembuangan panas. Ini adalah bagian dari karakterisasi, namun juga sangat bergantung pada kasus penggunaan, pilihan kemasan, dan keseluruhan arsitektur sistem dalam paket.

“Untuk chiplet, marginalitas dalam desainnya sangat kecil mengingat PPA yang optimal (menargetkan pj/bit yang agresif dan kepadatan tepi pantai), yang sangat penting ketika merancang PHY chiplet,” kata Rishi Chugh, wakil presiden pemasaran produk, IP Group di Cadence. “Keandalan adalah kuncinya, begitu pula kemampuan observasi untuk menyaring KGD, serta mencapai keberhasilan operasional komersial. Skema integritas data seperti CRC (pemeriksaan redundansi siklik), pemindaian mata, BiST, dan sirkuit pemantauan diterapkan dalam desain untuk ketahanan, dan desain tersebut harus dilengkapi dengan mekanisme kegagalan untuk memastikan jalur data tangguh.”

Seluruh bab dalam protokol UCIe didedikasikan untuk inisialisasi dan pelatihan yang terkait dengan protokol UCIe, yang mencakup aspek observabilitas protokol, tambah Chugh.

Selain itu, terdapat perdebatan mengenai apakah dasar sebenarnya untuk menambahkan kemampuan observasi ke dalam suatu sistem adalah bagian tersulit, atau apakah perubahan pemikiran seputar konsep-konsep ini lebih sulit.

“Sebenarnya tidak terlalu rumit dibandingkan dengan hal-hal lain karena 'hanya' blok lain yang harus dihubungkan. Ada observasi, dan kami memiliki kemampuan untuk melacak berbagai hal,” kata Frank Schirrmeister, wakil presiden solusi dan pengembangan bisnis di IP Arteris. “Pengguna sudah meminta hal-hal seperti melihat register dari sudut pandang perangkat lunak. Jadi sekarang tantangannya adalah membuat register tersebut tersedia di NoC. Dari perspektif NoC, ada protokolnya sendiri seperti CHI, ACE, AMBA, OCP atau lainnya, dan itulah mekanisme bahasanya — cara mereka berbicara dan berinteraksi. Di dalam NoC, dengan protokol yang lebih kompleks, ada banyak hal yang terjadi dalam beberapa siklus, jadi Anda perlu menunggu tanggapan, lalu Anda memasukkan segala sesuatunya ke dalam alur.”

Hal ini mirip dengan eksekusi spekulatif pada prosesor. “Kami membicarakan kredit ini, seperti berapa lama saya harus menunggu tanggapan dan lain sebagainya,” jelas Schirrmeister. “Itu semua adalah bagian dari protokol. Di NoC, Anda perlu memahami masalah seperti seberapa dalam buffernya? Kapan sebenarnya saya menunggu data? Ini sebagian karena kinerja. Kemudian, agar dapat diamati, Anda dapat menyambungkan ke data, dan sensor mungkin menggunakan jaringannya sendiri bergantung pada cara Anda ingin mengonfigurasinya. Dalam kasus monitor on-chip, Anda perlu memutuskan apakah akan menempatkannya pada bus observasi khusus, misalnya. Selalu ada diskusi, berapa banyak debug yang sebenarnya saya miliki? Pada akhirnya, ini 'hanya' interkoneksi lain dari komponen-komponen tersebut dan Anda perlu memutuskan bagaimana cara mengekspornya dari chip, dan seterusnya. Berapa banyak yang Anda simpan dalam chip adalah pertanyaan tentang berapa banyak real estat silikon yang bersedia saya keluarkan untuk itu?”

Hal ini menjadi sangat penting ketika menyatukan chiplet. “Bagaimana cara memastikan saya memiliki cukup ruang untuk entitas komputasi yang hanya tampak seperti data, yang sebenarnya tidak menambahkan nilai apa pun ke fungsi langsungnya?” tanya Gajinder Panesar, kepala arsitek di Picocom. “Selain itu, saya mungkin bukan ahli pemantauan, tapi saya tahu saya membutuhkannya. Jadi saya memerlukan sesuatu yang mengatakan, 'Tekan saja tombol itu.' Anda mempunyai lingkungan, kami sedang melakukan perancangan, dan 'ini' terjadi. Idealnya, kita harus mengamati perilaku kinerja CPU dan kemudian secara dinamis menyesuaikan aspek-aspek tertentu dari inti untuk mendapatkan kinerja yang lebih baik.”

Salah satu bagian yang belum dikembangkan adalah kontrol dinamis perangkat, dan penyesuaian yang dapat dilakukan sepanjang masa pakainya.

“Katakanlah kita memiliki semua kemampuan untuk memodelkan segalanya di awal,” kata Lee Harrison, direktur pemasaran produk di grup Tessent di Perangkat Lunak Siemens Digital Industries. “Kami memiliki semua monitor yang terpasang untuk melakukan hal-hal di dalam sistem, namun ini menutup loop tersebut. Untuk geometri yang lebih baru, masih banyak pembelajaran yang harus dilakukan untuk benar-benar mengoptimalkan cara kami menyesuaikan berbagai parameter perangkat untuk meningkatkan keandalannya. Bagian yang menutup putaran sistem dalam kehidupan adalah tempat di mana terdapat nilai yang sangat besar. Namun masih ada pekerjaan yang harus diselesaikan.

Mengubah peran tanggung jawab

Chiplet komersial menambah masalah pelik lainnya, yaitu siapa yang bertanggung jawab jika terjadi sesuatu yang tidak terduga atau terjadi kesalahan.

“Jika saya seorang pembuat chip, saya yang membuat chipnya dan saya mungkin akan melaluinya OSAT untuk pengujian,” kata Paul Karazuba, wakil presiden pemasaran di expedera. “Saya mungkin menggunakan ASE sebagai rumah pengemasan, tapi saya menjualnya dengan nama dan garansi saya. Ini akan menjadi menarik ketika kita memiliki chiplet. Dalam semua pertemuan kami mengenai chiplet, pertanyaan yang selalu muncul adalah siapa yang akan bertanggung jawab atas apa. Katakanlah saya membuat chiplet AI dan saya menjualnya ke dalam sistem dan mengemasnya dengan enam chiplet perusahaan lain. Perusahaan mana yang akan menjadi garansi? Perusahaan mana yang akan melakukan layanannya? Tidak ada konsensus nyata saat ini.”

Ide kerjanya adalah perusahaan yang namanya tertera di luar paket akan bertanggung jawab, kata Karazuba. “Perusahaan tersebut mungkin akan menjadi pihak yang mempunyai tanggung jawab akhir atas layanan kepada pelanggannya, namun perusahaan ini menghadirkan lapisan layanan lain yang perlu disediakan oleh pembuat chiplet, dan itu akan menjadi hal yang menarik. Ketakutannya adalah sekitar tahun 2000, segitiga Intel-Microsoft-Dell semua orang saling tuding. Itu adalah ketakutan yang tidak terucapkan di industri saat ini.”

Dan mungkin itu bukan salah satu chipletnya. Apa yang terjadi jika media atau interkoneksi fisik rusak?

“Dari sudut pandang pengujian, sebuah chiplet mungkin teruji dengan baik,” kata Karazuba. “Tetapi ketika ada masalah interkoneksi fisik, bagaimana pembuat chiplet memahami hal tersebut dibandingkan dengan pembuat modul multichip? Ini akan menjadi menarik. Satu-satunya cara untuk mengatasi masalah ini adalah dengan coba-coba. Kita dapat merancang kontrak legal sebanyak yang kita inginkan sebagai pembuat semikonduktor, tetapi kita berada dalam situasi yang belum dipetakan dan banyak hal harus disesuaikan. Model pendukung harus disesuaikan untuk mencerminkan realitas baru bahwa silikon monolitik tidak menjadi sarana utama penjualan semikonduktor.”

Kapoor dari Synopsys telah melihat refleksi dalam ekosistem. “Ekosistem selalu ada, tetapi ekosistem aktif di mana pun Anda berada mungkin merupakan lingkaran berikutnya di sekitarnya. Jika Anda melakukan desain, Anda hanya akan memperhatikan aturan desain pengecoran dan manual aturan desain. Itu berubah ketika Anda berbicara tentang chiplet. Bahkan dengan desainnya, kini Anda memikirkan pengujian lebih dari sebelumnya. Anda sedang berbicara dengan Keuntungan dan Teradyne. Meskipun Anda hanya seorang desainer, Anda harus memikirkan apa yang perlu Anda masukkan dari sudut pandang ATPG dan bagaimana hal itu akan diuji. Ukuran ekosistem yang relevan semakin meningkat.”

Namun, industri tidak punya pilihan selain menyelesaikan masalah ini. “Kami telah membicarakan tentang pasar chiplet. Anda akan bisa mengeluarkan dadu dan menyiapkannya. Kita masih jauh dari itu, namun langkah-langkahnya menjadi lebih jelas mengenai apa yang perlu kita capai. Konektivitas adalah hal mendasar. Standar UCIe adalah suatu keharusan, dan bersamaan dengan itu muncullah protokol dan aturan dari sudut pandang konektivitas yang harus Anda tetapkan. Berikutnya adalah model yang didefinisikan dengan sangat jelas. Tantangan yang kita bicarakan khususnya dipengaruhi oleh panas dan listrik. Beberapa standar sudah ada mengenai hal tersebut, dan kami akan beralih dari konektivitas ke model yang dikarakterisasi, sehingga kami dapat menggunakannya dengan lebih andal. Kemudian kita memerlukan semacam tanda tangan, yang mana kita dapat melihat dari sudut pandang testabilitas umur hidup dan bagaimana semua orang mati akan berubah secara berbeda.”

Masukan untuk semua ini akan datang dari chip dan monitor sistem, yang juga harus didasarkan pada standar.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoAiStream. Kecerdasan Data Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Mencetak Masa Depan bersama Adryenn Ashley. Akses Di Sini.

- Beli dan Jual Saham di Perusahaan PRE-IPO dengan PREIPO®. Akses Di Sini.

- Sumber: https://semiengineering.com/chiplet-planning-kicks-into-high-gear/

- :memiliki

- :adalah

- :bukan

- :Di mana

- $NAIK

- 1

- 20

- 30

- 3d

- a

- kemampuan

- Sanggup

- Tentang Kami

- mempercepat

- Mencapai

- aktif

- sebenarnya

- sebenarnya

- menambahkan

- menambahkan

- menambahkan

- tambahan

- Disesuaikan

- penyesuaian

- Adopsi

- iklan

- maju

- Aerospace

- agresif

- Penuaan

- AI

- Semua

- Persekutuan

- mengizinkan

- sudah

- juga

- selalu

- am

- AMD

- jumlah

- an

- analisis

- menganalisis

- dan

- Lain

- Apa pun

- Aplikasi

- aplikasi

- pendekatan

- arsitektur

- ADALAH

- sekitar

- AS

- penampilan

- aspek

- terkait

- At

- otomotif

- otonom

- kendaraan otonom

- tersedia

- menghindari

- jauh

- kembali

- berdasarkan

- Pada dasarnya

- BE

- karena

- menjadi

- menjadi

- menjadi

- sebelum

- Awal

- makhluk

- Percaya

- Manfaat

- TERBAIK

- Lebih baik

- Besar

- Terbesar

- Bit

- Memblokir

- papan

- kedua

- Istirahat

- Membawa

- luas

- lebih luas

- membangun

- dibangun di

- ikat

- bis

- bisnis

- pengembangan bisnis

- tapi

- tombol

- membeli

- by

- Irama

- bernama

- CAN

- kemampuan

- mobil

- yang

- kasus

- kasus

- Menyebabkan

- pusat

- Pusat

- ceo

- tertentu

- rantai

- menantang

- tantangan

- menantang

- perubahan

- berubah

- Perubahan

- mengubah

- Bab

- mencirikan

- ditandai

- memeriksa

- Cek

- kepala

- keping

- Keripik

- pilihan

- pilihan

- Lingkaran

- lebih jelas

- Jelas

- Menutup

- penutupan

- KOHEREN

- kompak

- bergabung

- bagaimana

- datang

- kedatangan

- komersial

- Perusahaan

- perusahaan

- kompleks

- kompleksitas

- rumit

- komponen

- konsep

- konsep

- Perhatian

- prihatin

- Konferensi

- Terhubung

- terhubung

- Konektivitas

- Konsensus

- Mempertimbangkan

- pertimbangan

- konteks

- kontinu

- terus menerus

- kontrak

- kontras

- kontras

- kontrol

- percakapan

- Core

- Biaya

- bisa

- meliputi

- CPU

- CRC

- Kredit

- sangat penting

- terbaru

- pelanggan

- disesuaikan

- siklus

- data

- Data Center

- Pusat Data

- Tanggal

- hari

- transaksi

- perdebatan

- dasawarsa

- memutuskan

- dedicated

- mendalam

- didefinisikan

- kepadatan

- tergantung

- Tergantung

- Mendesain

- dirancang

- perancang

- desainer

- merancang

- diinginkan

- dikembangkan

- Pengembangan

- alat

- Devices

- MELAKUKAN

- Mati

- berbeda

- sulit

- digital

- Kepala

- menghilang

- diskusi

- diskusi

- mendistribusikan

- do

- tidak

- melakukan

- dilakukan

- Dont

- turun

- penggerak

- selama

- dinamis

- dinamis

- dinamika

- setiap

- mudah

- ekosistem

- Ekosistem

- usaha

- muncul

- aktif

- pemberdayaan

- akhir

- cukup

- memastikan

- Seluruh

- entitas

- Lingkungan Hidup

- kesalahan

- terutama

- menetapkan

- perkebunan

- dll

- Bahkan

- Acara

- peristiwa

- pERNAH

- semua orang

- segala sesuatu

- contoh

- eksekusi

- ada

- ada

- mahal

- ahli

- menjelaskan

- ekspor

- memperpanjang

- mata

- kain

- faktor

- kegagalan

- Kegagalan

- jauh

- Fashion

- takut

- beberapa

- Ara

- Angka

- Ikan

- cocok

- tetap

- Fokus

- Untuk

- kekuatan

- pasukan

- sebagainya

- Pengecoran

- dari

- depan

- fungsi

- fungsi

- mendasar

- Fundamental

- gigi

- mendapatkan

- mendapatkan

- diberikan

- Go

- tujuan

- Pergi

- akan

- baik

- besar

- sangat

- Kelompok

- Grup

- tangan

- terjadi

- Kejadian

- Terjadi

- Memiliki

- memiliki

- he

- Kesehatan

- di sini

- High

- Frekuensi tinggi

- sangat

- sejarah

- Rumah

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- Namun

- HTTPS

- besar

- i

- ICS

- ide

- ideal

- if

- Segera

- Dampak

- dampak

- diimplementasikan

- penting

- mustahil

- memperbaiki

- perbaikan

- in

- termasuk

- Termasuk

- meningkatkan

- independen

- sendiri-sendiri

- industri

- industri

- Infrastruktur

- mulanya

- input

- mengintegrasikan

- integrasi

- integritas

- berinteraksi

- interaksi

- menarik

- intern

- ke

- memperkenalkan

- IP

- isu

- masalah

- IT

- NYA

- hanya

- Kapoor

- kunci

- Kicks

- Jenis

- Tahu

- dikenal

- Jalur

- bahasa

- besar

- kemudian

- Hukum

- lapisan

- tata ruang

- memimpin

- terkemuka

- pengetahuan

- paling sedikit

- Lee

- Informasi

- Tingkat

- siklus hidup

- masa hidup

- seumur hidup

- 'like'

- baris

- LINK

- Panjang

- lagi

- mencari

- Lot

- Rendah

- terbuat

- Arus utama

- utama

- membuat

- pembuat

- Pembuat

- Membuat

- pengelolaan

- manajer

- panduan

- diproduksi

- banyak

- Pasar

- Marketing

- pasar

- dewasa

- max-width

- Mungkin..

- mengukur

- mekanisme

- pertemuan

- metode

- mungkin

- Misi

- mode

- model

- model

- modul

- Modul

- Memantau

- pemantauan

- monitor

- Monolitis

- bulan

- lebih

- bergerak

- banyak

- beberapa

- harus

- my

- nama

- Perlu

- kebutuhan

- jaringan

- New

- berikutnya

- tidak

- node

- terkenal

- sekarang

- jumlah

- mengamati

- of

- lepas

- on

- ONE

- terus-menerus

- hanya

- Buka

- operasional

- optimal

- Optimize

- Opsi

- or

- urutan

- organisasi

- Lainnya

- Peserta lainnya

- Lainnya

- kami

- di luar

- di luar

- lebih

- secara keseluruhan

- Mengatasi

- sendiri

- paket

- dikemas

- pengemasan

- panel

- parameter

- bagian

- peserta

- tertentu

- khususnya

- rekan

- bagian

- lalu

- paul

- prestasi

- perspektif

- fisik

- Secara fisik

- memilih

- gambar

- bagian

- potongan-potongan

- pipa saluran

- Tempat

- perencanaan

- plato

- Kecerdasan Data Plato

- Data Plato

- pemain

- Titik

- Sudut pandang

- Populer

- portofolio

- mungkin

- potensi

- kekuasaan

- Bisa ditebak

- presiden

- pers

- Pencegahan

- sebelumnya

- primer

- Sebelumnya

- mungkin

- Masalah

- masalah

- prosesor

- Produk

- Profil

- Proposal

- protokol

- protokol

- memberikan

- publik

- menempatkan

- Puting

- Qualcomm

- kualitas

- pertanyaan

- menonjol

- Baca

- siap

- nyata

- real estate

- Kenyataan

- benar-benar

- alasan

- baru

- diakui

- mencerminkan

- Pikiran

- register

- relatif

- relevan

- keandalan

- memperbaiki

- berulang

- melaporkan

- membutuhkan

- wajib

- Persyaratan

- tabah

- tanggapan

- tanggapan

- tanggung jawab

- tanggung jawab

- ISTIRAHAT

- benar

- kesegaran

- Peran

- Aturan

- aturan

- Tersebut

- penjualan

- mengatakan

- mengatakan

- mengatakan

- Skala

- skala

- pemindaian

- skema

- Sekolah

- Layar

- melihat

- terlihat

- ruas

- menjual

- Penjualan

- semikonduktor

- senior

- sensor

- layanan

- set

- beberapa

- Rak

- bergeser

- harus

- ditunjukkan

- sisi

- Sinyal

- sinyal

- penting

- signifikan

- Silikon

- mirip

- tunggal

- ENAM

- Enam bulan

- Ukuran

- ukuran

- keterampilan

- Melambat

- kecil

- lebih kecil

- smartphone

- So

- Perangkat lunak

- Solusi

- MEMECAHKAN

- Memecahkan

- beberapa

- sesuatu

- sumber

- sumber

- Space

- speaker

- khusus

- spesifikasi

- spekulatif

- kecepatan

- menghabiskan

- Meremas

- tumpukan

- standar

- standar

- mulai

- Tangga

- Masih

- menyimpan

- sukses

- sukses

- seperti itu

- menggugat

- pemasok

- mendukung

- Simposium

- sistem

- sistem

- Mengambil

- Dibutuhkan

- Berbicara

- pembicaraan

- penargetan

- teknik

- Teknologi

- istilah

- uji

- pengujian

- dari

- bahwa

- Grafik

- mereka

- Mereka

- diri

- kemudian

- teori

- Sana.

- panas

- Ini

- mereka

- hal

- hal

- Pikir

- ini

- itu

- meskipun?

- Melalui

- waktu

- untuk

- hari ini

- bersama

- terhadap

- jejak

- Pelatihan

- transfer

- percobaan

- coba-coba

- tsmc

- khas

- memahami

- Sedang berlangsung

- Tiba-tiba

- unik

- us

- menggunakan

- bekas

- Berharga

- nilai

- berbagai

- kendaraan

- penjaja

- vendor

- Lawan

- vertikal

- secara vertikal

- sangat

- Wakil Presiden

- View

- menunggu

- Menunggu

- ingin

- adalah

- Waters

- Cara..

- cara

- we

- BAIK

- pergi

- Apa

- Apa itu

- ketika

- apakah

- yang

- sementara

- SIAPA

- seluruh

- yang

- tersebar luas

- akan

- rela

- nirkabel

- dengan

- dalam

- Kerja

- bekerja sama

- kerja

- bengkel

- dunia

- akan

- Salah

- namun

- kamu

- Anda

- zephyrnet.dll