Tekanan termal merupakan masalah umum dalam pengemasan tingkat lanjut, bersamaan dengan tantangan tekanan mekanis. Keduanya diperburuk oleh integrasi heterogen, yang sering kali memerlukan pencampuran bahan dengan koefisien muai panas (CTE) yang tidak sesuai.

Dampaknya sudah terlihat dan kemungkinan akan menjadi lebih buruk ketika kepadatan paket meningkat melebihi 1,000 benjolan per keping.

“Anda menggabungkan logam yang memiliki CTE relatif tinggi, kemudian Anda mendapatkan polimer yang memiliki kekakuan CTE lebih besar, dan kemudian Anda mendapatkan dielektrik yang memiliki CTE sangat rendah. Setelah Anda menyatukan semuanya, stres tidak dapat dihindari,” kata Mario Gonzalez, direktur ilmiah dan manajer R&D untuk pemodelan dan karakterisasi mekanis dan termal di imec.

Tekanan seperti itu sering kali mengakibatkan lengkungan atau kemiringan cetakan yang signifikan, yang pada gilirannya menyebabkan kondisi yang mengurangi keandalan. “Anda berurusan dengan teknologi substrat yang berbeda dengan jumlah lapisan yang banyak,” kata Chip Greely, wakil presiden bidang teknik di Industri Promex. “Ketebalan inti yang berbeda-beda pada substrat, khususnya, mulai menimbulkan banyak masalah mekanis klasik, termasuk lengkungan, yang telah menjadi masalah bagi beberapa pemain besar. Kami meminta banyak pelanggan kami yang memiliki modul multi-chip integrasi heterogen sistem-dalam-paket, untuk menyediakan data shadow moiré pada media mereka sehingga kami dapat melihat perubahan lengkungannya terhadap suhu reflow dan idealnya menemukannya titik refleksi.”

Strain ini memiliki berbagai efek negatif, yang dialami dalam berbagai skala dimensi, menurut Gilad Barak, wakil presiden teknologi baru yang canggih di Nova. “Seringkali, pembengkokan dan puntiran fitur pada tingkat struktur nano diakibatkan oleh tekanan bawaan yang telah tercipta, seperti yang ditemukan di beberapa DRAM dan nanosheet logika front-end,” katanya. “Contoh lain berkaitan dengan area skala mikron di mana regangan yang diinduksi mencegah pembuatan struktur semikonduktor kelas atas, seperti yang biasa terjadi di 'zona pencegahan' di sekitar through-silicon vias (TSVs). Yang terakhir, dampak besar dari regangan yang ditimbulkan dapat menyebabkan wafer membungkuk, yang secara signifikan mempersulit penanganan dan fabrikasi wafer, yang berisiko mematahkan wafer itu sendiri. Pembengkokan wafer terutama terlihat selama pengendapan lapisan dielektrik tebal, seperti yang biasa terjadi selama pembuatan perangkat 3D NAND.”

Kabar baiknya adalah industri ini sangat menyadari hal ini dan masalah-masalah terkait lainnya. Kabar buruknya adalah masih kurangnya solusi, meskipun ada banyak pendekatan yang sedang dijajaki.

“Ada berbagai metodologi untuk mengurangi kelengkungan, namun tidak satupun yang benar-benar berhasil, dan selalu ada pengorbanannya,” kata Frank Chen, direktur aplikasi dan manajemen produk di Permukaan & Metrologi Bruker Nano. “Masalahnya tidak hanya terjadi pada pilihan aplikasi yang sempit. Kapan pun Anda memasang cetakan ke media lain, Anda akan mengalami masalah ini.”

Semua ini berarti bahwa inspeksi dan metrologi harus terus memainkan peranan penting. Masalah lain, seperti hot spot, juga dapat diperburuk ketika beberapa chip digabungkan dalam paket yang heterogen.

“Selama pengujian, berbagai chip akan memanas pada waktu dan suhu berbeda, menciptakan kemungkinan titik panas yang harus didinginkan dengan benar, kata Andrei Berar, direktur senior Pengembangan Bisnis Pengujian di Amkor. “Selain menciptakan pengontrol termal aktif yang spesifik – mencocokkan area chip yang berbeda – ada upaya signifikan untuk mengembangkan pengontrol termal adaptif yang dapat 'mengantisipasi' titik panas berdasarkan vektor yang disediakan oleh program pengujian.”

Kombinasi tersebut juga menyebabkan meningkatnya penggunaan metrologi hibrid – yang menggabungkan berbagai teknik untuk mencapai akar permasalahan dengan cara yang paling cepat.

Desain, inspeksi, solusi pengujian

Memang benar, interaksi klasik antara desain, inspeksi, dan tekanan termo-mekanis menjadi semakin kompleks dengan adanya ribuan sambungan yang semakin kecil dan rapuh.

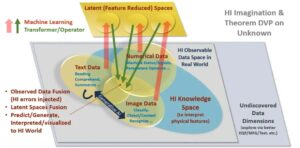

Salah satu hasilnya adalah penekanan baru pada pergeseran ke kiri, yang diharapkan dapat “merancang” masalah CTE dan dampak lanjutannya yang dapat menyebabkan panas berlebih dan tekanan mekanis. Dan untuk meningkatkan peluang pencegahan, serta menemukan cacat kritis, simulasi dan inspeksi diperlukan, menurut Andras Vass-Varnai, eksekutif pengembangan portofolio di segmen Industri Elektronik dan Semikonduktor di Perangkat Lunak Siemens Digital Industries.

“Kosimulasi termal dan struktural menggunakan dinamika aliran komputasi (CFD), pemodelan elemen hingga (FEA), dll., pada tahap desain awal paket membantu memahami kinerja rakitan yang diharapkan dan juga memungkinkan dasar yang baik untuk ' Pengoptimalan yang didorong oleh AI karena banyak pilihan desain dapat diparameterisasi,” jelas Vass-Varnai. “Setelah prototipe pertama dibuat, pengujian transien termal dapat membantu memetakan kinerja termal komponen. Jika terdapat ketidaksesuaian antara perilaku termal yang diharapkan dan perilaku termal sebenarnya, data pengujian dapat digunakan untuk 'mengkalibrasi' sifat material dari paket digital twin dan memperbarui pustaka material untuk akurasi awal yang lebih tinggi pada desain yang akan datang.”

Menemukan cara terbaik untuk menguji susunan bump, dan merancang untuk pengujian, merupakan tantangan yang semakin besar. “Bagaimana kalau ada sinyal yang naik dan turun?” tanya Rob Aitken, a Synopsys rekan. “Hal ini menciptakan masalah pengujian, karena sekarang Anda mendapatkan sinyal yang tidak mengarah ke mana pun dan sinyal lain yang datang entah dari mana, dan Anda harus memikirkan bagaimana Anda akan menguji hal-hal tersebut. Apakah Anda menyelidikinya? Namun dalam hal ini ada dimensi fisik yang harus Anda pertahankan, dan Anda berisiko mengalami kerusakan mekanis. Atau apakah Anda menemukan semacam struktur mirip JTAG? Namun hal ini kemudian mengurangi efisiensi titik-titik penghubung tersebut. Kita berada pada fase eksperimen besar-besaran di mana semua orang berkata, 'Mungkin ini akan berhasil, mungkin itu akan berhasil.' Saat ini, saya belum tentu ingin bertaruh pada apa yang dimaksud dengan 'itu'.

Ada pilihan pengujian tidak langsung dan langsung untuk penyelidikan cacat, menurut JCET. Misalnya CSAM (Computed Scanning Acoustic Tomography) dan sinar-X 3D bersifat tidak langsung, sedangkan analisis penampang mekanis adalah alat untuk pembuktian langsung. JCET juga memiliki peralatan karakterisasi termal yang canggih untuk mengkarakterisasi masalah material/struktur akibat cacat mekanis.

Inspeksi optik, seperti biasa, merupakan pendekatan tercepat untuk inspeksi inline, namun praktik terbaiknya adalah pendekatan hibrid. “Metode terbaik untuk mendeteksi arus pendek/terbuka dan cacat marginal adalah SPI (inspeksi pasta solder) ke AOI pra-reflow (inspeksi optik otomatis) ke AOI pasca-reflow ke sinar-X inline,” saran Timothy Skunes, wakil presiden penelitian dan pengembangan di Nordson Test & Inspection's CyberOptik portofolio.

Selain itu, modalitas lain mungkin berguna, terutama pada node tingkat lanjut. Misalnya, pendekatan terbaru untuk mengkarakterisasi regangan pada perangkat semikonduktor adalah Spektroskopi Raman (RS). “RS sangat dapat diterapkan untuk pengukuran pada struktur, menawarkan pengukuran cepat dalam hitungan detik, dan ukuran titik kecil beberapa mikron untuk memungkinkan pengukuran mendetail,” kata Barak dari Nova. “Kesulitan dalam mengukur regangan pada struktur secara langsung sebelum diperkenalkannya spektroskopi Raman sebagai alat metrologi in-line di pabrik menyebabkan pengujian pada tahap selanjutnya dalam proses fabrikasi.”

Pada akhirnya, untuk pemeriksaan menyeluruh, tidak ada jalan pintas. Penghitungan anggaran mungkin memerlukan metrik komparatif, seperti biaya awal instrumen baru vs. biaya berkelanjutan dari RMA yang berlebihan. Dan ada satu hal lagi yang perlu dipertimbangkan — bagaimana memastikan Anda dapat memercayai data Anda.

“Apakah Anda akan membuang materi yang mungkin bagus untuk memastikan bahwa Anda tidak memiliki materi bermasalah dalam apa yang Anda sampaikan kepada pengguna akhir? Siapa yang akan menanggung biayanya?” memperingatkan Mike McIntyre, direktur manajemen produk perangkat lunak di Ke Inovasi, yang merekomendasikan database statistik untuk penilaian komparatif yang akurat saat melakukan klasifikasi kerusakan otomatis.

halaman melengkung

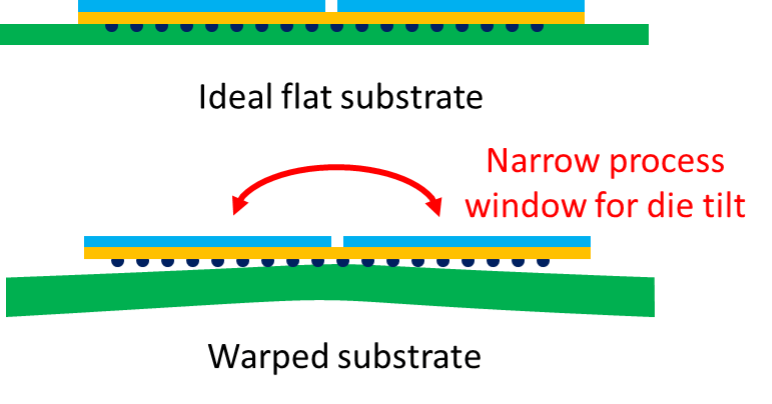

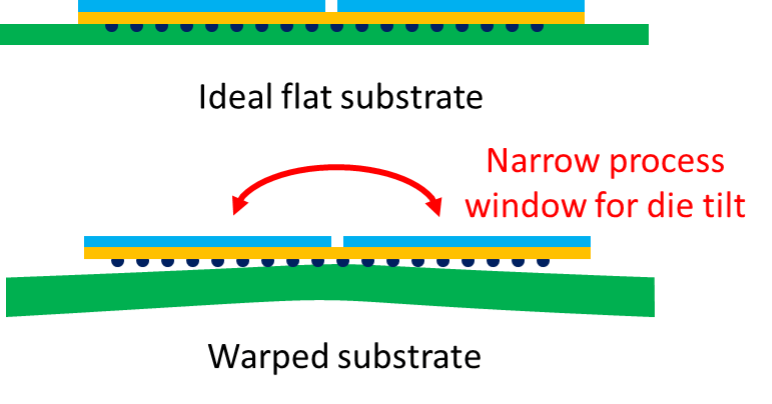

Salah satu akibat terburuk dari stres adalah kelengkungan. Mungkin mengejutkan bahwa warpage sulit dideteksi, namun efeknya tidak selalu sejelas kelihatannya. Warpage menyebabkan sedikit perbedaan koplanaritas antara chip dan substrat, menyebabkan beberapa microbumps tidak cukup terhubung dengan pad di bawahnya, suatu kegagalan yang disebut non-basah.

“Pertimbangkan prosesor canggih berukuran 50 hingga 60mm, sebagai contoh,” kata Chen. “Karena ukurannya yang besar, sulit untuk memprosesnya tanpa adanya lengkungan apa pun. Namun demikian, jika alat die-attach disetel ke bagian tengah jendela prosesnya, alat tersebut dapat lolos pemeriksaan dan diproduksi dengan hasil yang tinggi. Masalahnya adalah toleransinya bisa sangat sempit. Segera setelah Anda memiliki sedikit kemiringan di atas lengkungan, Anda memiliki masalah yang tidak basah.”

Lebih buruk lagi, jika hal ini terjadi pada jarak bump pitch pada kisaran 50µm (ukuran bump ̴35µm), bayangkan masalahnya ketika dimensi bump semakin menyusut. Hal ini sudah menjadi kekhawatiran bagi industri otomotif, karena mereka sedang bergerak menuju generasi berikutnya pada tahun 2023 hingga 2024. Transisi penting akan terjadi di sekitar node 28nm, kata Chen.

Gambar 1 Alat die-attach memiliki jendela proses yang sangat sempit untuk kemiringan die ketika terjadi lengkungan. Sumber: Bruker

Tidak basah

“Tidak basah,” adalah istilah luas yang mencakup beberapa masalah yang dapat terjadi pada tonjolan solder, yang sebagian besar tidak terlalu kentara. Karena solder sering kali berbentuk cair, proses pengaplikasiannya disebut “pembasahan”. Tautan yang lemah disebut “tidak basah”, yang menjadi tantangan lebih besar pada node yang lebih kecil dengan koneksi yang lebih tipis.

Non-basah sering kali lolos dari proses penyaringan biasa, hanya untuk muncul kemudian sebagai chip yang dikembalikan (RMA). Akar penyebabnya bisa bersifat termal, mekanis, atau kombinasinya, seperti siklus termal pada mobil yang juga melewati medan yang berat. Efek kumulatifnya dapat memberikan tekanan termal-mekanis yang cukup untuk memutus kontak.

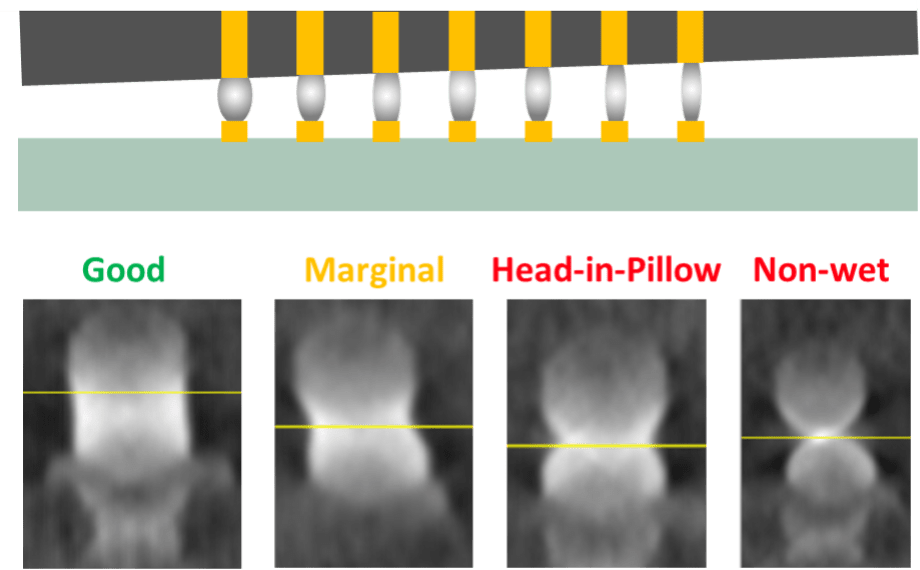

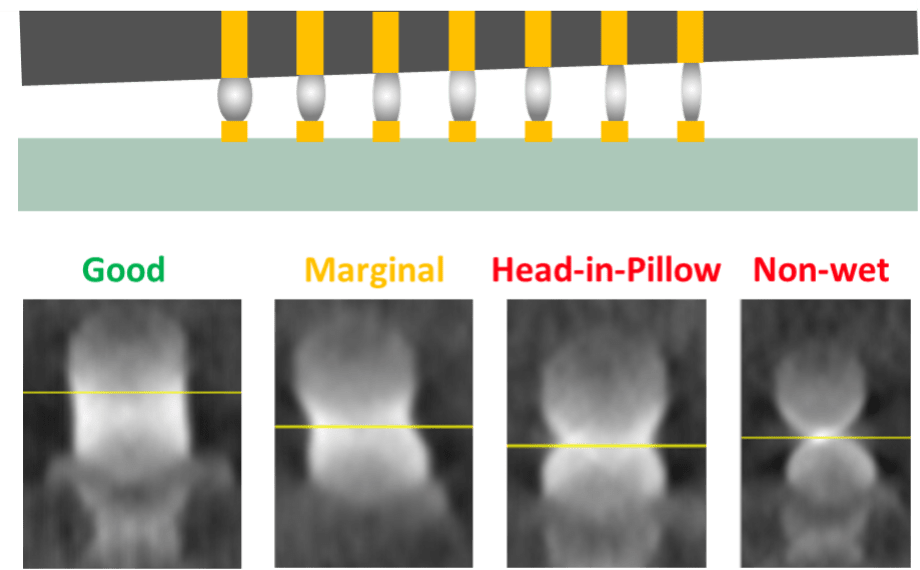

Ada nama panggilan tambahan yang menggambarkan jenis masalah tertentu. Alih-alih sambungan yang baik berbentuk kolom dan halus, pada cacat “kepala-di-bantal”, satu bola tampak tenggelam ke dalam bola lainnya, seperti kepala di atas bantal.

“Ia masih melakukan kontak sehingga uji kelistrikannya bagus, namun Anda dapat melihat bahwa ia sangat rapuh,” kata Chen sambil menunjuk ke arah hasil rontgen dari kepala yang berada di dalam bantal. “Segera setelah Anda mengalami tekanan termal atau tekanan mekanis, itu mungkin akan rusak total. Meskipun kontaknya tidak basah, sambungan yang tipis menghasilkan resistansi tinggi, kinerja kurang optimal, dan kemungkinan besar tidak akan bertahan lama. Terbuka non-basah tidak akan berfungsi sama sekali. Dalam skenario tipikal dengan kemiringan, terdapat transisi yang terlihat dari gundukan yang terbentuk dengan baik ke gundukan yang tidak basah.”

Masalah kritisnya adalah cacat laten — sambungan yang cukup berfungsi untuk lulus uji kelistrikan tetapi gagal di lapangan.

Gambar 2 Transisi bertahap membentuk gundukan yang bagus ke gundukan yang tidak basah dengan adanya kemiringan cetakan. Sumber: Bruker

“Ini adalah masalah besar saat ini pada banyak jenis perangkat karena efek tekanan panas,” kata Chen. “Salah satu pelanggan memiliki produk yang lulus penyaringan e-test dan dikirim keluar. Sayangnya, mereka mengalami banyak RMA karena kegagalan non-basah yang terjadi setelahnya.”

Beberapa perusahaan mengatasi hal ini melalui inspeksi manual yang sangat membosankan. Sayangnya, setiap pemeriksaan pada manusia dapat menyebabkan kelelahan operator, terutama ketika pemeriksa mencoba menemukan kesalahan halus selama shift multi-jam.

Sisi positifnya, kini ada pendekatan otomatis untuk pemeriksaan, seperti alat sinar-X yang dapat digunakan secara inline. “Ada dorongan besar menuju inspeksi berkecepatan tinggi dan otomatis untuk mencapai <100dppb, terutama untuk industri otomotif,” kata Chen.

Ini menjadi lebih rumit dari sana. “Khususnya, solder, yang menjadi penyebab banyak produk tidak basah, juga mengalami migrasi listrik,” kata Tom Marinis, anggota utama Staf Teknis Laboratorium di Draper. “Jika kerapatan arus dalam sambungan antara chip dan substrat terlalu tinggi untuk solder tertentu selama periode waktu tertentu, karena suhu leleh solder mungkin relatif rendah dibandingkan dengan suhu pengoperasian perangkat, Anda bisa mendapatkan migrasi. atom dan benar-benar membentuk rongga dan akhirnya membuka sambungan.”

Marinis memperingatkan bahwa alat pemodelan komersial pada tingkat perangkat-PCB belum cukup matang untuk secara konsisten memperingatkan potensi masalah migrasi listrik, jadi penting untuk tetap melakukan uji penuaan yang dipercepat.

Kesimpulan

Pada akhirnya, mendeteksi masalah keandalan dari cacat laten akan memerlukan metrologi pengambilan sampel yang lebih tinggi dan peka terhadap pergeseran cetakan, rotasi, ketinggian, kemiringan, dan parameter lainnya. Hal ini juga memerlukan lebih banyak ketergantungan pada pemodelan multi-fisika untuk mencoba mengantisipasi dan menyelesaikan potensi masalah sebelum produksi. Dan ketika industri semikonduktor dan otomotif terus berbaur, ada lebih banyak hal yang dipertaruhkan selain RMA.

“Biaya akibat kegagalan meningkat secara eksponensial karena cacat laten berpindah dari perangkat, modul, hingga mobil yang dapat membahayakan nyawa manusia,” kata Chen. Inilah sebabnya mengapa pembuat chip menciptakan solusi holistik yang menggabungkan desain, inspeksi, dan pengujian untuk menangkap kesalahan laten dengan lebih baik.

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Sumber: https://semiengineering.com/bump-reliability-is-challenged-by-latent-defects/

- 000

- 1

- 2023

- 2024

- 3d

- a

- dipercepat

- Menurut

- ketepatan

- tepat

- Mencapai

- aktif

- sebenarnya

- tambahan

- Tambahan

- menangani

- maju

- Penuaan

- Waspada

- Semua

- memungkinkan

- sudah

- Meskipun

- selalu

- analisis

- dan

- Lain

- mengharapkan

- berlaku

- aplikasi

- Menerapkan

- pendekatan

- pendekatan

- DAERAH

- daerah

- sekitar

- Majelis

- penilaian

- terkait

- melampirkan

- Otomatis

- otomotif

- industri otomotif

- Buruk

- bola

- berdasarkan

- dasar

- Beruang

- karena

- menjadi

- menjadi

- sebelum

- di belakang

- makhluk

- di bawah

- TERBAIK

- Bertaruh

- Lebih baik

- antara

- Luar

- Besar

- lebih besar

- Bit

- Istirahat

- luas

- anggaran belanja

- dibangun di

- built-in

- bisnis

- pengembangan bisnis

- bernama

- Bisa Dapatkan

- mobil

- mobil

- kasus

- gulat

- Menyebabkan

- penyebab

- menyebabkan

- pusat

- CFD

- menantang

- tertantang

- tantangan

- menantang

- kesempatan

- Perubahan

- mencirikan

- chen

- keping

- Keripik

- pilihan

- klasik

- klasifikasi

- kombinasi

- kombinasi

- menggabungkan

- bergabung

- menggabungkan

- bagaimana

- komersial

- Umum

- Perusahaan

- dibandingkan

- sama sekali

- kompleks

- rumit

- komponen

- Perhatian

- Kondisi

- Terhubung

- koneksi

- Koneksi

- Mempertimbangkan

- kontak

- terus

- Core

- sudut

- Biaya

- bisa

- penutup

- membuat

- dibuat

- menciptakan

- membuat

- kritis

- terbaru

- Sekarang

- pelanggan

- pelanggan

- pemotongan

- data

- Basis Data

- berurusan

- kepadatan

- menggambarkan

- Mendesain

- desain

- terperinci

- mengembangkan

- dikembangkan

- Pengembangan

- alat

- Devices

- Mati

- perbedaan

- berbeda

- Kesulitan

- digital

- kembar digital

- ukuran

- langsung

- langsung

- Kepala

- melakukan

- Dont

- turun

- pedagang kain

- pengemudi

- dijuluki

- selama

- dinamika

- Awal

- efek

- efek

- efisiensi

- upaya

- Elektronik

- tekanan

- Teknik

- cukup

- memastikan

- peralatan

- kesalahan

- terutama

- dll

- Eter (ETH)

- Bahkan

- akhirnya

- segala sesuatu

- contoh

- eksekutif

- perluasan

- diharapkan

- berpengalaman

- menjelaskan

- Dieksplorasi

- eksponensial

- sangat

- GAGAL

- Kegagalan

- tercepat

- kelelahan

- Fitur

- sesama

- beberapa

- bidang

- Ara

- Angka

- Akhirnya

- Menemukan

- temuan

- Pertama

- aliran

- bentuk

- ditemukan

- dari

- dengan putus asa

- fungsionil

- lebih lanjut

- generasi

- mendapatkan

- Pergi

- akan

- baik

- bertahap

- Pertumbuhan

- tumbuh

- Penanganan

- Sulit

- kepala

- tinggi

- membantu

- membantu

- High

- lebih tinggi

- sangat

- holistik

- Mudah-mudahan

- PANAS

- Seterpercayaapakah Olymp Trade? Kesimpulan

- How To

- HTTPS

- manusia

- Hibrida

- dampak

- penting

- in

- Termasuk

- Meningkatkan

- meningkatkan

- industri

- industri

- mulanya

- sebagai gantinya

- instrumen

- integrasi

- Pengantar

- investigasi

- terpencil

- isu

- masalah

- IT

- Diri

- Jenis

- laboratorium

- besar

- besar-besaran

- lebih besar

- Terakhir

- lapisan

- lapisan

- memimpin

- terkemuka

- Memimpin

- Dipimpin

- Tingkat

- perpustakaan

- Mungkin

- link

- Cair

- hidup

- Panjang

- Lot

- Rendah

- memelihara

- membuat

- Membuat

- pengelolaan

- manajer

- panduan

- diproduksi

- banyak

- peta

- Mario

- sesuai

- bahan

- bahan

- dewasa

- max-width

- cara

- pengukuran

- ukur

- mekanis

- anggota

- Logam

- metode

- metodologi

- Metrik

- Metrologi

- mungkin

- migrasi

- berbaur

- pemodelan

- modul

- Modul

- lebih

- paling

- bergerak

- beberapa

- nano

- perlu

- dibutuhkan

- negatif

- Namun

- New

- Teknologi baru

- berita

- berikutnya

- simpul

- node

- Jelas

- menawarkan

- ONE

- terus-menerus

- Buka

- operasi

- operator

- optimasi

- Opsi

- urutan

- Lainnya

- paket

- paket

- pengemasan

- Sakit

- parameter

- tertentu

- khususnya

- Lulus

- orang

- melakukan

- prestasi

- periode

- tahap

- fisik

- pitches

- plato

- Kecerdasan Data Plato

- Data Plato

- Bermain

- pemain

- Titik

- poin

- polimer

- portofolio

- positif

- mungkin

- potensi

- praktek

- kehadiran

- presiden

- mencegah

- Utama

- Sebelumnya

- mungkin

- penyelidikan

- Masalah

- masalah

- proses

- proses

- Prosesor

- Produk

- manajemen Produk

- Produksi

- program

- bukti

- tepat

- properties

- prototipe

- memberikan

- disediakan

- menempatkan

- R & D

- jarak

- cepat

- nyata

- baru

- merekomendasikan

- menurunkan

- mengurangi

- refleksi

- relatif

- keandalan

- kepercayaan

- diperbaharui

- membutuhkan

- membutuhkan

- penelitian

- penelitian dan pengembangan

- mengakibatkan

- dihasilkan

- Hasil

- Risiko

- risiko

- peran

- akar

- Run

- Tersebut

- mengatakan

- sisik

- pemindaian

- skenario

- penyaringan

- detik

- tampaknya

- ruas

- seleksi

- semikonduktor

- senior

- peka

- beberapa

- bayangan

- Bentuknya

- bergeser

- PERGESERAN

- dikirimkan

- Pendek

- Menunjukkan

- Sinyal

- penting

- signifikan

- simulasi

- Ukuran

- ukuran

- kecil

- lebih kecil

- So

- Perangkat lunak

- Solusi

- beberapa

- Segera

- sumber

- tertentu

- Spektroskopi

- Spot

- Staf

- Tahap

- magang

- taruhan

- awal

- Negara

- statistik

- Masih

- tekanan

- struktural

- struktur

- subyek

- sukses

- seperti itu

- mengherankan

- Teknis

- teknik

- Teknologi

- uji

- pengujian

- Grafik

- Daerah

- mereka

- Sana.

- panas

- hal

- hal

- ribuan

- Melalui

- Pelemparan

- waktu

- kali

- untuk

- bersama

- toleransi

- terlalu

- alat

- alat

- puncak

- terhadap

- transisi

- Kepercayaan

- MENGHIDUPKAN

- jenis

- khas

- memahami

- mendatang

- Memperbarui

- menggunakan

- Pengguna

- berbagai

- Luas

- Wakil Presiden

- terlihat

- terkenal

- Apa

- yang

- sementara

- SIAPA

- akan

- tanpa

- Kerja

- terburuk

- akan

- x-ray

- hasil panen

- Anda

- zephyrnet.dll