Dalam terminologi rangkaian terpadu, droop adalah penurunan tegangan yang terjadi pada suatu rangkaian. Ini adalah fenomena yang umum terjadi dan dapat terjadi karena alasan berikut. Catu daya berada di bawah rentang pengoperasian yang dirancang untuk sebuah chip, sehingga mengakibatkan penurunan. Lebih banyak arus yang ditarik oleh elemen konduktif daripada yang dirancang, sehingga mengakibatkan penurunan. Terkadang, gangguan sinyal atau noise pada catu daya juga dapat menyebabkan fluktuasi tegangan sehingga mengakibatkan drop.

Droops dapat mempengaruhi pengoperasian suatu sirkuit. Berkurangnya kinerja chip, yang menyebabkan waktu pemrosesan lebih lama, adalah salah satu dampaknya. Namun berikut ini adalah beberapa dampak yang lebih serius dan/atau bencana. Chip tersebut dapat menarik lebih banyak arus untuk mempertahankan tingkat kinerja yang menyebabkan peningkatan konsumsi daya dan pembuangan panas. Hal ini dapat menyebabkan berkurangnya masa pakai chip dan dalam kasus yang parah, kegagalan total chip karena variasi pengaturan dan penahanan. Droops juga dapat menyebabkan kerusakan data atau kesalahan pada output. Ini adalah masalah yang sangat serius untuk aplikasi yang bergantung pada keakuratan dan keandalan chip.

Tentu saja, fenomena droop menjadi pertimbangan serius saat merancang chip dan sistem. Metode paling umum untuk mengurangi gangguan adalah pemisahan catu daya, pengaturan voltase, optimalisasi sirkuit, dan manajemen daya tingkat sistem. Kondisi dan lingkungan pengoperasian di mana chip akan bekerja dipertimbangkan dengan cermat saat merancang solusi mitigasi penurunan.

Masalah Zaman Modern

Ketika SoC menjadi lebih kompleks, masalah droop juga bisa menjadi sangat rumit. Desain SoC perlu dioptimalkan untuk kinerja, daya, biaya, faktor bentuk, dll. selain mengoptimalkan mitigasi droop. Terkadang tujuan pengoptimalan ini dapat bersaing satu sama lain dan saling bertentangan dan harus dilakukan pengorbanan. Misalnya, arsitek SoC dapat menaikkan tegangan operasi, menambah margin, untuk menghindari penurunan lokal dan global, namun kenaikan ini secara kuadrat meningkatkan daya. Sebagai alternatif, desainer dapat membuat generasi jam mereka beradaptasi dengan droop, yang menjadikan kinerja sebagai fungsi waktu peralihan generasi jam.

Akibatnya, SoC berukuran besar di komputasi pusat data dan ruang AI sangat rentan terhadap penurunan. Beban kerja pelanggan sangat beragam dan dinamis, menyebabkan fluktuasi signifikan dalam aktivitas peralihan dan penarikan saat ini. Tentu saja, sistem tidak boleh membiarkan permasalahan yang ada tidak terselesaikan. Potensi kerugian akibat keluaran yang tidak akurat atau kegagalan besar sebuah chip terlalu tinggi untuk sistem dan aplikasi saat ini.

Masalah Droop yang Terlokalisasi

Akselerator khusus aplikasi banyak digunakan bersama dengan prosesor tujuan umum untuk memberikan kinerja dan efisiensi daya yang diperlukan dalam lingkungan komputasi yang menuntut saat ini. Namun akselerator ini serta bertambahnya jumlah inti dan sifat beban kerja yang asimetris, meningkatkan risiko penurunan tegangan lokal. Penurunan tegangan lokal ini disebabkan oleh peningkatan aktivitas peralihan secara tiba-tiba dan dapat menyebabkan gangguan sementara dan potensi kegagalan mode misi.

Jika terjadi penurunan lokal, dampaknya dapat dikurangi melalui penskalaan frekuensi dinamis. Hal ini dicapai dengan mengatur waktu suatu rangkaian menggunakan jam yang dapat diprogram. Jam yang dapat diprogram memungkinkan frekuensi dan waktu jam disesuaikan secara dinamis berdasarkan kondisi pengoperasian rangkaian saat ini.

Movellus Memudahkan Mengatasi Droop yang Terlokalisasi

Movellus, penyedia sistem-IP digital terkemuka, telah mengembangkan rangkaian produk Aeonic Generate untuk mengatasi masalah lokal. Portofolio Movellus Aeonic menawarkan solusi pencatatan jam kerja adaptif yang memberikan respons penurunan cepat. Portofolionya mencakup sistem pencatatan jam kerja adaptif. Blok penyusun dibuat dengan Verilog yang dapat disintesis, menjadikannya fleksibel secara intrinsik. Solusinya dapat dikonfigurasi, dipindai, dan portabel proses untuk berbagai aplikasi SoC tingkat lanjut.

Rangkaian produk Aeonic Generate juga jauh lebih kecil dibandingkan solusi analog tradisional. Hasilnya, desainer dapat membuat instance IP sesuai dengan rincian yang diperlukan tanpa dampak signifikan pada area tersebut. Selain itu, seiring perpindahan desain ke geometri proses yang lebih halus, area Aeonic Generate terus berkembang, menjadikannya solusi ideal untuk desain masa depan.

Beberapa Kasus Penggunaan

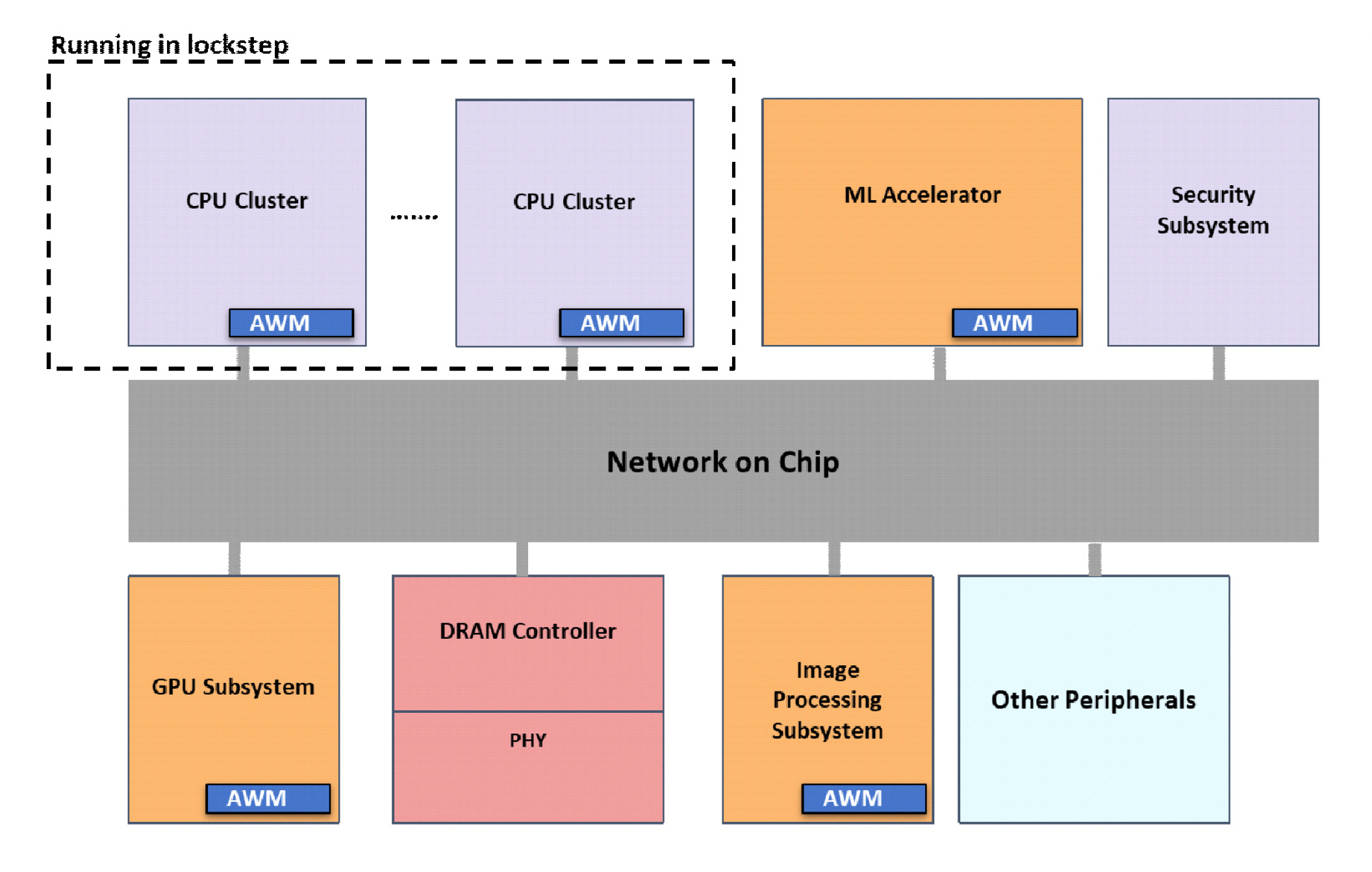

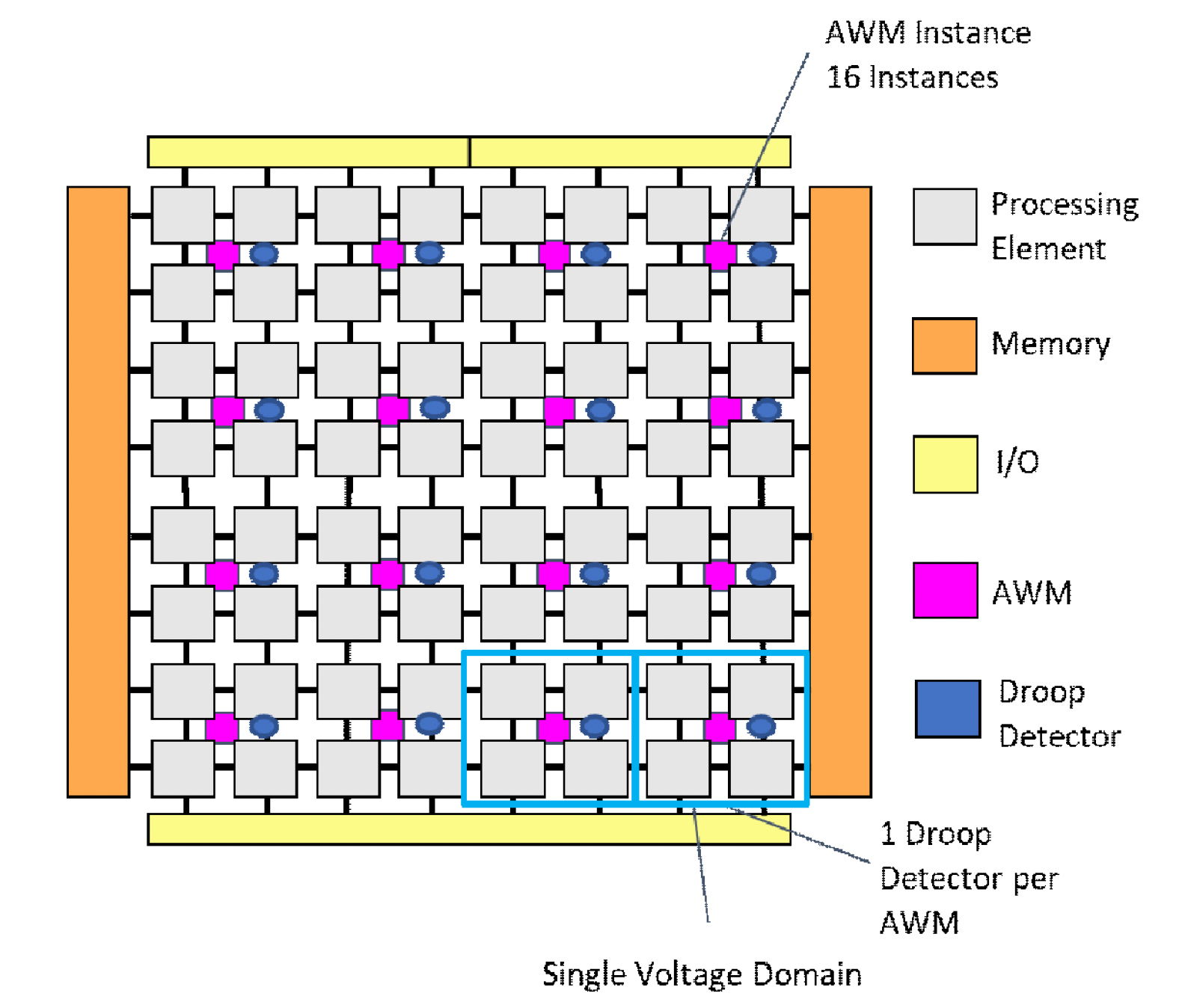

Gambar dari Movellus berikut menunjukkan contoh arsitektur prosesor ADAS dengan Platform Aeonic Generate AWM untuk dukungan droop lokal. Seorang arsitek akan memasangkan modul AWM dengan sub-blok atau akselerator khusus aplikasi untuk merespons penurunan lokal yang disebabkan oleh beban kerja dalam lima siklus jam dengan pergeseran frekuensi yang cepat dan bebas kesalahan. Pendekatan ini memberikan solusi yang andal dan efisien untuk mengatasi tantangan penurunan lokal di pasar jaringan ADAS, 5G, dan pusat data.

Gambar dari Movellus berikut menunjukkan contoh arsitektur lautan prosesor SoC dengan Aeonic Generate untuk dukungan droop lokal. Seorang arsitek akan memasangkan modul Aeonic Generate AWM dengan detektor droop untuk cluster prosesor dan domain voltase terkait untuk merespons dengan cepat terhadap droop lokal yang disebabkan oleh beban kerja. Hal ini memungkinkan desainer untuk memberikan respons droop yang terlokalisasi dan independen tanpa mengubah kinerja cluster prosesor di sekitarnya.

Kesimpulan

Penurunan tegangan lokal dapat terjadi pada SoC heterogen yang berisi akselerator khusus aplikasi. Penurunan ini dapat menyebabkan gangguan waktu, gangguan sementara, dan kegagalan mode misi di ADAS, jaringan pusat data, dan aplikasi 5G. Arsitek sistem dapat menerapkan pencatatan jam kerja adaptif untuk merespons penurunan ini dan mengurangi dampaknya.

Rangkaian produk IP generasi jam berkinerja tinggi Movellus™ Aeonic Generate Adaptive Workload Module (AWM) adalah bagian dari arsitektur Aeonic Intelligent Clock Network™. Untuk informasi lebih lanjut, lihat Movellus' Halaman AWM Aeonic Generate™.

Baca Juga:

Keuntungan Domain Pencatatan Jam Sinkron Skala Besar dalam Desain Chip AI

Sekarang Saatnya untuk Jaringan Jam Cerdas

Manfaat Kinerja, Daya, dan Area (PPA) Melalui Jaringan Jam Cerdas

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- Platoblockchain. Intelijen Metaverse Web3. Pengetahuan Diperkuat. Akses Di Sini.

- Sumber: https://semiwiki.com/ip/326488-adaptive-clock-technology-for-real-time-droop-response/

- :adalah

- 5G

- a

- akselerator

- akselerator

- ketepatan

- dicapai

- kegiatan

- menyesuaikan

- ADA

- tambahan

- Selain itu

- alamat

- menangani

- Disesuaikan

- maju

- AI

- memungkinkan

- dan

- aplikasi

- pendekatan

- arsitektur

- ADALAH

- DAERAH

- AS

- terkait

- At

- berdasarkan

- BE

- menjadi

- di bawah

- Manfaat

- Memblokir

- Blok

- Bangunan

- dibangun di

- by

- CAN

- Bisa Dapatkan

- tidak bisa

- hati-hati

- kasus

- bencana

- Menyebabkan

- pusat

- tantangan

- keping

- Keripik

- Clock

- Kelompok

- Umum

- bersaing

- lengkap

- kompleks

- menghitung

- komputasi

- Kondisi

- pertimbangan

- dianggap

- konsumsi

- terus

- Korupsi

- Biaya

- bisa

- Melawan

- sepasang

- Tentu saja

- terbaru

- pelanggan

- siklus

- data

- Data Center

- Datacenter

- hari

- menyampaikan

- menuntut

- Mendesain

- dirancang

- desainer

- merancang

- desain

- dikembangkan

- digital

- didistribusikan

- beberapa

- domain

- domain

- ditarik

- Menjatuhkan

- Tetes

- dinamis

- dinamis

- setiap

- efisiensi

- efisien

- elemen

- Lingkungan Hidup

- lingkungan

- kesalahan

- dll

- contoh

- Kegagalan

- Air terjun

- keluarga

- Angka

- fleksibel

- fluktuasi

- berikut

- Untuk

- bentuk

- Frekuensi

- dari

- fungsi

- masa depan

- tujuan umum

- menghasilkan

- generasi

- mendapatkan

- Aksi

- Go

- Anda

- terjadi

- Terjadi

- Memiliki

- High

- kinerja tinggi

- memegang

- HTTPS

- ideal

- Dampak

- dampak

- melaksanakan

- in

- tidak akurat

- termasuk

- Meningkatkan

- Pada meningkat

- Meningkatkan

- meningkatkan

- independen

- informasi

- terpadu

- integrasi

- Cerdas

- secara intrinsik

- IP

- isu

- masalah

- IT

- besar

- besar-besaran

- memimpin

- terkemuka

- Tingkat

- kewajiban

- Hidup

- lokal

- lagi

- terbuat

- memelihara

- MEMBUAT

- Membuat

- pengelolaan

- Margin

- pasar

- max-width

- metode

- Mengurangi

- meringankan

- mitigasi

- modul

- Modul

- lebih

- paling

- pindah

- Alam

- kebutuhan

- jaringan

- jaringan

- Kebisingan

- terutama

- jumlah

- of

- Penawaran

- on

- ONE

- operasi

- Operasi

- optimasi

- dioptimalkan

- mengoptimalkan

- Lainnya

- keluaran

- bagian

- prestasi

- melakukan

- gejala

- Platform

- plato

- Kecerdasan Data Plato

- Data Plato

- portofolio

- Pos

- potensi

- kekuasaan

- Sumber Daya listrik

- proses

- pengolahan

- Prosesor

- prosesor

- Produk

- pemberi

- menyediakan

- menaikkan

- jarak

- cepat

- cepat

- Baca

- real-time

- alasan

- mengurangi

- Regulasi

- keandalan

- dapat diandalkan

- wajib

- Menanggapi

- tanggapan

- mengakibatkan

- dihasilkan

- Naik

- Risiko

- Run

- Skala

- skala

- SEA

- serius

- penyiapan

- parah

- Pergeseran

- Pertunjukkan

- Sinyal

- penting

- signifikan

- lebih kecil

- pintar

- larutan

- Solusi

- beberapa

- Space

- seperti itu

- tiba-tiba

- menyediakan

- mendukung

- rentan

- sistem

- sistem

- Berduaan

- Teknologi

- terminologi

- bahwa

- Grafik

- Daerah

- mereka

- Mereka

- Ini

- Melalui

- waktu

- kali

- waktu

- untuk

- hari ini

- terlalu

- tradisional

- menggunakan

- sangat beragam

- melalui

- Tegangan

- BAIK

- terkenal

- yang

- lebar

- Rentang luas

- sangat

- akan

- dengan

- dalam

- tanpa

- akan

- zephyrnet.dll