टेबल पर विशेषज्ञ: सेमीकंडक्टर इंजीनियरिंग, समूह निदेशक, उत्पाद प्रबंधन, फ्रैंक फेरो के साथ तेजी से विषम प्रणालियों में मेमोरी के लिए आगे के रास्ते के बारे में बात करने के लिए बैठे। ताल; स्टीवन वू, साथी और प्रतिष्ठित आविष्कारक Rambus; जोंगसिन युन, मेमोरी टेक्नोलॉजिस्ट सीमेंस ईडीए; रैंडी व्हाइट, मेमोरी सॉल्यूशंस प्रोग्राम मैनेजर कीज़; और फ्रैंक शिरमिस्टर, समाधान और व्यवसाय विकास के उपाध्यक्ष धमनी. उस बातचीत के अंश इस प्रकार हैं। इस चर्चा का पहला भाग पाया जा सकता है यहाँ उत्पन्न करें.

![[एलआर]: फ्रैंक फेरो, कैडेंस; स्टीवन वू, रैम्बस; जोंगसिन युन, सीमेंस ईडीए; रैंडी व्हाइट, कीसाइट; और फ्रैंक शिरमिस्टर, आर्टेरिस।](https://platoaistream.com/wp-content/uploads/2024/01/rethinking-memory.png)

[एलआर]: फ्रैंक फेरो, कैडेंस; स्टीवन वू, रैम्बस; जोंगसिन युन, सीमेंस ईडीए; रैंडी व्हाइट, कीसाइट; और फ्रैंक शिरमिस्टर, आर्टेरिस

एसई: चूँकि हम एआई/एमएल और बिजली की माँगों से जूझ रहे हैं, किन कॉन्फ़िगरेशनों पर पुनर्विचार करने की आवश्यकता है? क्या हम वॉन न्यूमैन वास्तुकला से दूर बदलाव देखेंगे?

वू: सिस्टम आर्किटेक्चर के संदर्भ में, उद्योग में विभाजन चल रहा है। पारंपरिक एप्लिकेशन जो प्रमुख वर्कहॉर्स हैं, जिन्हें हम x86-आधारित सर्वर पर क्लाउड में चलाते हैं, दूर नहीं जा रहे हैं। ऐसे कई सॉफ़्टवेयर हैं जिन्हें बनाया और विकसित किया गया है, और जो अच्छा प्रदर्शन करने के लिए उस आर्किटेक्चर पर निर्भर होंगे। इसके विपरीत, AI/ML एक नया वर्ग है। लोगों ने आर्किटेक्चर पर पुनर्विचार किया है और बहुत ही डोमेन-विशिष्ट प्रोसेसर बनाए हैं। हम देख रहे हैं कि लगभग दो-तिहाई ऊर्जा एक प्रोसेसर और एक एचबीएम डिवाइस के बीच डेटा को स्थानांतरित करने में खर्च होती है, जबकि केवल एक तिहाई वास्तव में डीआरएएम कोर में बिट्स तक पहुंचने में खर्च होती है। डेटा संचलन अब बहुत अधिक चुनौतीपूर्ण और महंगा है। हम स्मृति से छुटकारा नहीं पाने जा रहे हैं। हमें इसकी आवश्यकता है क्योंकि डेटासेट बड़े होते जा रहे हैं। तो सवाल यह है कि, 'आगे बढ़ने का सही तरीका क्या है?' स्टैकिंग के बारे में बहुत चर्चा हुई है। यदि हम उस मेमोरी को लें और उसे सीधे प्रोसेसर के ऊपर रखें, तो यह आपके लिए दो काम करता है। सबसे पहले, बैंडविड्थ आज किनारे या चिप की परिधि तक सीमित है। यहीं पर I/Os जाते हैं। लेकिन यदि आप इसे सीधे प्रोसेसर के शीर्ष पर रखते हैं, तो अब आप वितरित इंटरकनेक्ट के लिए चिप के पूरे क्षेत्र का उपयोग कर सकते हैं, और आप मेमोरी में ही अधिक बैंडविड्थ प्राप्त कर सकते हैं, और इसे सीधे नीचे फीड किया जा सकता है प्रोसेसर. लिंक बहुत छोटे हो जाते हैं, और बिजली दक्षता संभवतः 5X से 6X तक बढ़ जाती है। दूसरा, मेमोरी से अधिक क्षेत्र सरणी इंटरकनेक्ट के कारण आप जो बैंडविड्थ प्राप्त कर सकते हैं, वह भी कई पूर्णांक कारक द्वारा बढ़ जाता है। उन दो चीजों को एक साथ करने से अधिक बैंडविड्थ प्रदान की जा सकती है और इसे अधिक शक्ति-कुशल बनाया जा सकता है। उद्योग किसी भी आवश्यकता के अनुसार विकसित होता है, और यह निश्चित रूप से एक तरीका है जिससे हम भविष्य में मेमोरी सिस्टम को अधिक ऊर्जा कुशल बनने और अधिक बैंडविड्थ प्रदान करने के लिए विकसित होते देखेंगे।

लोहा: जब मैंने पहली बार 2016 के आसपास एचबीएम पर काम करना शुरू किया, तो कुछ अधिक उन्नत ग्राहकों ने पूछा कि क्या इसे स्टैक किया जा सकता है। वे काफी समय से इस पर विचार कर रहे हैं कि DRAM को शीर्ष पर कैसे रखा जाए क्योंकि इसके स्पष्ट फायदे हैं। भौतिक परत से, PHY मूल रूप से नगण्य हो जाता है, जिससे बहुत अधिक शक्ति और दक्षता बचती है। लेकिन अब आपको कई-100W का प्रोसेसर मिल गया है जिसके शीर्ष पर एक मेमोरी है। स्मृति गर्मी सहन नहीं कर सकती. यह संभवतः ताप श्रृंखला की सबसे कमजोर कड़ी है, जो एक और चुनौती पैदा करती है। फ़ायदे हैं, लेकिन उन्हें अभी भी यह पता लगाना होगा कि थर्मल से कैसे निपटना है। उस प्रकार की वास्तुकला को आगे बढ़ाने के लिए अब अधिक प्रोत्साहन है, क्योंकि यह वास्तव में आपको प्रदर्शन और शक्ति के मामले में समग्र रूप से बचाता है, और यह आपकी गणना दक्षता में सुधार करेगा। लेकिन कुछ भौतिक डिज़ाइन चुनौतियाँ हैं जिनसे निपटना होगा। जैसा कि स्टीव कह रहे थे, हम देख रहे हैं कि सभी प्रकार के आर्किटेक्चर सामने आ रहे हैं। मैं इस बात से पूरी तरह सहमत हूं कि जीपीयू/सीपीयू आर्किटेक्चर कहीं नहीं जा रहे हैं, वे अभी भी प्रभावी रहेंगे। साथ ही, ग्रह पर हर कंपनी अपने एआई के लिए बेहतर मूसट्रैप के साथ आने की कोशिश कर रही है। हम ऑन-चिप SRAM और हाई-बैंडविड्थ मेमोरी के संयोजन देखते हैं। बिजली की वजह से डेटा सेंटर में एलपीडीडीआर का लाभ कैसे उठाया जाए, इस मामले में एलपीडीडीआर इन दिनों काफी चर्चा में है। हमने कुछ एआई अनुमान अनुप्रयोगों के साथ-साथ सभी पुराने मेमोरी सिस्टम में भी जीडीडीआर का उपयोग होते देखा है। वे अब एक पदचिह्न पर यथासंभव अधिक से अधिक DDR5s निचोड़ने का प्रयास कर रहे हैं। मैंने हर वह आर्किटेक्चर देखा है जिसके बारे में आप सोच सकते हैं, चाहे वह डीडीआर, एचबीएम, जीडीडीआर, या अन्य हो। यह आपके प्रोसेसर कोर पर निर्भर करता है कि आपका समग्र मूल्य क्या है, और फिर आप अपने विशेष आर्किटेक्चर को कैसे तोड़ सकते हैं। मेमोरी सिस्टम जो इसके साथ जाता है, इसलिए आप जो उपलब्ध है उसके आधार पर अपने सीपीयू और अपनी मेमोरी आर्किटेक्चर को मूर्तिकला कर सकते हैं।

यूं: एक अन्य मुद्दा गैर-अस्थिरता है। उदाहरण के लिए, यदि AI को IoT-आधारित AI चलाने के बीच में पावर अंतराल से निपटना है, तो हमें बहुत अधिक बिजली बंद करने और चालू करने की आवश्यकता होती है, और AI प्रशिक्षण के लिए इस सारी जानकारी को बार-बार घुमाना पड़ता है। यदि हमारे पास कुछ प्रकार के समाधान हैं जहां हम उन वजनों को चिप में संग्रहीत कर सकते हैं ताकि हमें हमेशा एक ही वजन के लिए आगे और पीछे न जाना पड़े, तो यह बहुत अधिक बिजली की बचत होगी, खासकर IoT-आधारित AI के लिए। उन बिजली मांगों को पूरा करने के लिए एक और समाधान होगा।

शिरमिस्टर: एनओसी परिप्रेक्ष्य से, जो मुझे आकर्षक लगता है, वह यह है कि आपको एनओसी से गुजरने वाले प्रोसेसर से इन पथों को अनुकूलित करना होगा, एक नियंत्रक के साथ मेमोरी इंटरफ़ेस तक पहुंचना होगा जो संभावित रूप से यूसीआईई के माध्यम से एक चिपलेट को दूसरे चिपलेट में पास करने के लिए जा रहा है, जिसमें फिर मेमोरी होती है यह। ऐसा नहीं है कि वॉन न्यूमैन आर्किटेक्चर ख़त्म हो गए हैं। लेकिन अब बहुत सारी विविधताएं हैं, यह उस कार्यभार पर निर्भर करता है जिसकी आप गणना करना चाहते हैं। उन्हें स्मृति के संदर्भ में विचार करने की आवश्यकता है, और स्मृति केवल एक पहलू है। आपको डेटा इलाके से डेटा कहां से मिलता है, इसे इस DRAM में कैसे व्यवस्थित किया जाता है? हम इन सभी चीजों पर काम कर रहे हैं, जैसे यादों का प्रदर्शन विश्लेषण और फिर उस पर सिस्टम आर्किटेक्चर को अनुकूलित करना। यह नए आर्किटेक्चर के लिए बहुत सारे नवाचारों को प्रेरित कर रहा है, जिसके बारे में मैंने तब कभी नहीं सोचा था जब मैं विश्वविद्यालय में वॉन न्यूमैन के बारे में सीख रहा था। बिल्कुल दूसरे छोर पर, आपके पास जाली जैसी चीजें हैं। अब बीच में बहुत सारे आर्किटेक्चर पर विचार किया जाना बाकी है, और यह मेमोरी बैंडविड्थ, कंप्यूट क्षमताओं आदि द्वारा संचालित है, समान दर से नहीं बढ़ रहा है।

व्हाइट: अलग-अलग गणना या वितरित कंप्यूटिंग को शामिल करने का चलन है, जिसका अर्थ है कि वास्तुकार को अपने निपटान में अधिक उपकरण रखने की आवश्यकता है। मेमोरी पदानुक्रम का विस्तार हुआ है. इसमें शब्दार्थ शामिल हैं, साथ ही सीएक्सएल और विभिन्न हाइब्रिड यादें भी शामिल हैं, जो फ्लैश और डीआरएएम में उपलब्ध हैं। डेटा सेंटर का एक समानांतर अनुप्रयोग ऑटोमोटिव है। ऑटोमोटिव में हमेशा ईसीयू (इलेक्ट्रॉनिक कंट्रोल यूनिट) के साथ यह सेंसर कंप्यूट होता था। मैं इस बात से रोमांचित हूं कि यह डेटा सेंटर में कैसे विकसित हुआ है। तेजी से आगे बढ़ते हुए, और आज हमने कंप्यूट नोड्स वितरित किए हैं, जिन्हें डोमेन नियंत्रक कहा जाता है। एक ही बात है। यह पता लगाने की कोशिश की जा रही है कि शायद बिजली इतनी बड़ी बात नहीं है क्योंकि कंप्यूटर का पैमाना उतना बड़ा नहीं है, लेकिन ऑटोमोटिव के लिए विलंबता निश्चित रूप से एक बड़ी बात है। एडीएएस को सुपर-हाई बैंडविड्थ की आवश्यकता है, और आपके पास अलग-अलग ट्रेडऑफ़ हैं। और फिर आपके पास अधिक यांत्रिक सेंसर हैं, लेकिन डेटा सेंटर में समान बाधाएं हैं। आपके पास कोल्ड स्टोरेज है जिसमें कम विलंबता की आवश्यकता नहीं है, और फिर आपके पास अन्य उच्च बैंडविड्थ एप्लिकेशन हैं। यह देखना दिलचस्प है कि आर्किटेक्ट के लिए उपकरण और विकल्प कितने विकसित हो गए हैं। उद्योग ने प्रतिक्रिया देने में वास्तव में अच्छा काम किया है, और हम सभी विभिन्न समाधान प्रदान करते हैं जो बाजार में आते हैं।

एसई: मेमोरी डिज़ाइन उपकरण कैसे विकसित हुए हैं?

शिरमिस्टर: जब मैंने 90 के दशक में अपने पहले कुछ चिप्स के साथ शुरुआत की, तो सबसे अधिक इस्तेमाल किया जाने वाला सिस्टम टूल एक्सेल था। तब से, मुझे हमेशा आशा रही है कि सिस्टम-स्तर पर हम जो चीजें करते हैं, मेमोरी, बैंडविड्थ विश्लेषण, इत्यादि के लिए यह एक बिंदु पर टूट सकता है। इसका मेरी टीमों पर काफी प्रभाव पड़ा। उस समय, यह बहुत उन्नत चीज़ थी। लेकिन रैंडी की बात पर, अब कुछ जटिल चीजों को निष्ठा के स्तर पर अनुकरण करने की आवश्यकता है जो पहले गणना के बिना संभव नहीं थी। एक उदाहरण देने के लिए, DRAM एक्सेस के लिए एक निश्चित विलंबता मानने से खराब आर्किटेक्चर निर्णय हो सकते हैं और संभावित रूप से चिप पर डेटा ट्रांसपोर्ट आर्किटेक्चर को गलत तरीके से डिजाइन किया जा सकता है। दूसरा पहलू भी सच है. यदि आप हमेशा सबसे खराब स्थिति मानते हैं, तो आप वास्तुकला को अत्यधिक डिज़ाइन करेंगे। उपकरण DRAM और प्रदर्शन विश्लेषण करते हैं, और नियंत्रकों के लिए उचित मॉडल उपलब्ध होने से एक आर्किटेक्ट को यह सब अनुकरण करने की अनुमति मिलती है, यह एक आकर्षक वातावरण है। 90 के दशक से मेरी आशा है कि एक्सेल एक बिंदु पर एक के रूप में टूट सकता है सिस्टम लेवल टूल वास्तव में सच हो सकता है, क्योंकि कुछ गतिशील प्रभाव अब आप एक्सेल में नहीं कर सकते हैं क्योंकि आपको उन्हें अनुकरण करने की आवश्यकता है - खासकर जब आप PHY विशेषताओं के साथ डाई-टू-डाई इंटरफ़ेस में फेंकते हैं, और फिर लिंक परत सभी चीजें सही थीं या नहीं इसकी जांच करना और संभावित रूप से डेटा दोबारा भेजना जैसी विशेषताएं। उन सिमुलेशन के नहीं होने से उप-इष्टतम वास्तुकला का परिणाम होगा।

लोहा: हमारे द्वारा किए जाने वाले अधिकांश मूल्यांकनों में पहला कदम उन्हें DRAM दक्षता को देखना शुरू करने के लिए मेमोरी टेस्टबेंच देना है। यह एक बहुत बड़ा कदम है, यहाँ तक कि DRAM सिमुलेशन करने के लिए स्थानीय उपकरण चलाने जैसी सरल चीजें करना, लेकिन फिर पूर्ण विकसित सिमुलेशन में जाना। हम देखते हैं कि अधिक ग्राहक उस प्रकार के सिमुलेशन की मांग कर रहे हैं। यह सुनिश्चित करना कि आपकी DRAM दक्षता उच्च 90 के दशक में है, किसी भी मूल्यांकन में एक बहुत महत्वपूर्ण पहला कदम है।

वू: आप पूर्ण सिस्टम सिमुलेशन टूल का उदय क्यों देखते हैं इसका एक कारण यह है कि DRAM बहुत अधिक जटिल हो गए हैं। एक्सेल जैसे सरल टूल का उपयोग करके इन जटिल कार्यभारों में से कुछ के लिए बार में रहना अब बहुत मुश्किल है। यदि आप 90 के दशक में DRAM के डेटाशीट को देखें, तो वे डेटाशीट 40 पृष्ठों की तरह थीं। अब वे सैकड़ों पेज के हो गए हैं। यह केवल उच्च बैंडविड्थ को बाहर निकालने के लिए डिवाइस की जटिलता की बात करता है। आप इसे इस तथ्य के साथ जोड़ते हैं कि सिस्टम लागत में मेमोरी एक ऐसा ड्राइवर है, साथ ही प्रोसेसर के प्रदर्शन से संबंधित बैंडविड्थ और विलंबता भी है। यह शक्ति में भी एक बड़ा चालक है, इसलिए आपको अब और अधिक विस्तृत स्तर पर अनुकरण करने की आवश्यकता है। उपकरण प्रवाह के संदर्भ में, सिस्टम आर्किटेक्ट समझते हैं कि मेमोरी एक बहुत बड़ा चालक है। इसलिए उपकरणों को और अधिक परिष्कृत करने की आवश्यकता है, और उन्हें अन्य उपकरणों के साथ बहुत अच्छी तरह से इंटरफ़ेस करने की आवश्यकता है ताकि सिस्टम आर्किटेक्ट को सबसे अच्छा वैश्विक दृश्य मिल सके कि क्या हो रहा है - विशेष रूप से मेमोरी सिस्टम को कैसे प्रभावित कर रही है।

यूं: जैसे-जैसे हम एआई युग में आगे बढ़ते हैं, बहुत सारे मल्टी-कोर सिस्टम का उपयोग किया जाता है, लेकिन हम नहीं जानते कि कौन सा डेटा कहां जाता है। यह चिप के अधिक समानांतर भी चल रहा है। मेमोरी का आकार बहुत बड़ा होता है. यदि हम चैटजीपीटी-प्रकार के एआई का उपयोग करते हैं, तो मॉडलों के लिए डेटा हैंडलिंग के लिए लगभग 350 एमबी डेटा की आवश्यकता होती है, जो कि केवल वजन के लिए बड़ी मात्रा में डेटा है, और वास्तविक इनपुट/आउटपुट बहुत बड़ा है। आवश्यक डेटा की मात्रा में वृद्धि का मतलब है कि बहुत सारे संभाव्य प्रभाव हैं जो हमने पहले नहीं देखे हैं। इतनी बड़ी मात्रा में मेमोरी से संबंधित सभी त्रुटियों को देखना एक बेहद चुनौतीपूर्ण परीक्षण है। और ECC का उपयोग हर जगह किया जाता है, यहां तक कि SRAM में भी, जो परंपरागत रूप से ECC का उपयोग नहीं करता था, लेकिन अब यह सबसे बड़े सिस्टम के लिए बहुत आम है। उन सभी का परीक्षण करना बहुत चुनौतीपूर्ण है और उन सभी विभिन्न स्थितियों का परीक्षण करने के लिए ईडीए समाधानों द्वारा समर्थित होने की आवश्यकता है।

एसई: इंजीनियरिंग टीमों को दिन-प्रतिदिन किन चुनौतियों का सामना करना पड़ता है?

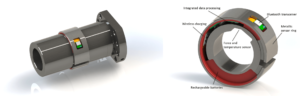

व्हाइट: किसी भी दिन, आप मुझे प्रयोगशाला में पाएंगे। मैं अपनी आस्तीनें चढ़ाता हूँ और मेरे हाथ गंदे हो जाते हैं, तार चुभ जाते हैं, सोल्डरिंग हो जाती है, और भी न जाने क्या-क्या। मैं पोस्ट-सिलिकॉन सत्यापन के बारे में बहुत सोचता हूं। हमने शुरुआती सिमुलेशन और ऑन-डाई टूल - BiST और इस तरह की चीज़ों के बारे में बात की। दिन के अंत में, शिप करने से पहले, हम कुछ प्रकार के सिस्टम सत्यापन या डिवाइस-स्तरीय परीक्षण करना चाहते हैं। हमने स्मृति दीवार पर काबू पाने के बारे में बात की। हम मेमोरी, एचबीएम, जैसी चीजों का सह-पता लगाते हैं। यदि हम पैकेजिंग प्रौद्योगिकी के विकास को देखें, तो हमने लीडेड पैकेजों के साथ शुरुआत की। वे सिग्नल अखंडता के लिए बहुत अच्छे नहीं थे। दशकों बाद, हम बॉल ग्रिड एरेज़ (बीजीए) की तरह अनुकूलित सिग्नल अखंडता की ओर बढ़ गए। हम उस तक नहीं पहुंच सके, जिसका मतलब है कि आप उसका परीक्षण नहीं कर सके। इसलिए हम इस अवधारणा के साथ आए जिसे एक डिवाइस इंटरपोजर कहा जाता है - एक बीजीए इंटरपोजर - और इसने हमें एक विशेष फिक्स्चर को सैंडविच करने की अनुमति दी जो सिग्नल को रूट करता है। तब हम इसे परीक्षण उपकरण से जोड़ सकते थे। आज तक तेजी से आगे बढ़े, और अब हमारे पास एचबीएम और चिपलेट्स हैं। मैं सिलिकॉन इंटरपोजर के बीच में अपने फिक्स्चर को कैसे सैंडविच करूं? हम नहीं कर सकते, और यही संघर्ष है। यह एक चुनौती है जो मुझे रात में जगाए रखती है। हम किसी ओईएम या सिस्टम ग्राहक के साथ क्षेत्र में विफलता विश्लेषण कैसे करते हैं, जहां उन्हें 90% दक्षता नहीं मिल रही है। लिंक में और भी त्रुटियाँ हैं, वे ठीक से आरंभ नहीं हो पा रहे हैं, और प्रशिक्षण काम नहीं कर रहा है। क्या यह सिस्टम अखंडता समस्या है?

शिरमिस्टर: क्या आप लैब तक चलने के बजाय वर्चुअल इंटरफ़ेस के साथ घर से ऐसा करना पसंद नहीं करेंगे? क्या उत्तर आपके द्वारा चिप में निर्मित अधिक विश्लेषणात्मकता नहीं है? चिपलेट्स के साथ, हम हर चीज़ को और भी अधिक एकीकृत करते हैं। वहां अपना सोल्डरिंग आयरन लाना वास्तव में कोई विकल्प नहीं है, इसलिए ऑन-चिप एनालिटिक्स के लिए एक तरीका होना चाहिए। एनओसी के लिए भी हमारी यही समस्या है। लोग एनओसी देखते हैं, और आप डेटा भेजते हैं और फिर वह चला जाता है। हमें वहां एनालिटिक्स डालने की जरूरत है ताकि लोग डिबग कर सकें, और यह विनिर्माण स्तर तक विस्तारित हो, ताकि आप अंततः घर से काम कर सकें और चिप एनालिटिक्स के आधार पर यह सब कर सकें।

लोहा: विशेष रूप से उच्च बैंडविड्थ मेमोरी के साथ, आप भौतिक रूप से वहां अंदर नहीं जा सकते। जब हम PHY को लाइसेंस देते हैं तो हमारे पास एक उत्पाद भी होता है जो उसके साथ जाता है ताकि आप उन 1,024 बिट्स में से हर एक पर नज़र रख सकें। आप टूल से DRAM पढ़ना और लिखना शुरू कर सकते हैं ताकि आपको भौतिक रूप से वहां जाने की जरूरत न पड़े। मुझे इंटरपोज़र विचार पसंद है. हम परीक्षण के दौरान इंटरपोज़र से कुछ पिन निकालते हैं, जो आप सिस्टम में नहीं कर सकते। इन 3डी प्रणालियों में प्रवेश करना वास्तव में एक चुनौती है। यहां तक कि डिज़ाइन टूल प्रवाह के दृष्टिकोण से भी, ऐसा लगता है कि अधिकांश कंपनियां इन 2.5डी टूल में से कई पर अपना व्यक्तिगत प्रवाह करती हैं। हम सिग्नल अखंडता, शक्ति, संपूर्ण प्रवाह से लेकर 2.5डी सिस्टम बनाने के लिए अधिक मानकीकृत तरीका एक साथ रखना शुरू कर रहे हैं।

व्हाइट: जैसे-जैसे चीज़ें धीरे-धीरे आगे बढ़ती हैं, मुझे आशा है कि हम अभी भी सटीकता का वही स्तर बनाए रख सकते हैं। मैं यूसीआईई फॉर्म फैक्टर अनुपालन समूह में हूं। मैं देख रहा हूं कि एक ज्ञात अच्छे पासे, एक सुनहरे पासे को कैसे चित्रित किया जाए। अंततः, इसमें बहुत अधिक समय लगने वाला है, लेकिन हमें परीक्षण के प्रदर्शन और सटीकता, जिसकी हमें आवश्यकता है, और उसमें मौजूद लचीलेपन के बीच एक सुखद माध्यम खोजने जा रहे हैं।

शिरमिस्टर: यदि मैं अधिक खुले उत्पादन वातावरण में चिपलेट्स और उनके अपनाने पर गौर करता हूं, तो इसे सही तरीके से काम करने के रास्ते में परीक्षण बड़ी चुनौतियों में से एक है। यदि मैं एक बड़ी कंपनी हूं और मैं इसके सभी पक्षों को नियंत्रित करता हूं, तो मैं चीजों को उचित रूप से नियंत्रित कर सकता हूं ताकि परीक्षण आदि संभव हो सके। अगर मैं यूसीआईई नारे पर जाना चाहता हूं कि यूसीआई पीसीआई से केवल एक अक्षर दूर है, और मैं एक ऐसे भविष्य की कल्पना करता हूं जहां यूसीआईई असेंबली, विनिर्माण परिप्रेक्ष्य से, आज पीसी में पीसीआई स्लॉट की तरह बन जाएगी, तो उसके लिए परीक्षण पहलू वास्तव में हैं चुनौतीपूर्ण। हमें समाधान ढूंढना होगा. करने को बहुत सारा काम है.

संबंधित आलेख

स्मृति का भविष्य (उपरोक्त गोलांक का भाग 1)

थर्मल और बिजली के मुद्दों को हल करने के प्रयासों से लेकर सीएक्सएल और यूसीआईई की भूमिकाओं तक, भविष्य में स्मृति के लिए कई अवसर हैं।

- एसईओ संचालित सामग्री और पीआर वितरण। आज ही प्रवर्धित हो जाओ।

- प्लेटोडेटा.नेटवर्क वर्टिकल जेनरेटिव एआई। स्वयं को शक्तिवान बनाएं। यहां पहुंचें।

- प्लेटोआईस्ट्रीम। Web3 इंटेलिजेंस। ज्ञान प्रवर्धित। यहां पहुंचें।

- प्लेटोईएसजी. कार्बन, क्लीनटेक, ऊर्जा, पर्यावरण, सौर, कचरा प्रबंधन। यहां पहुंचें।

- प्लेटोहेल्थ। बायोटेक और क्लिनिकल परीक्षण इंटेलिजेंस। यहां पहुंचें।

- स्रोत: https://semiengineering.com/rethinking-memory/

- :हैस

- :है

- :नहीं

- :कहाँ

- $यूपी

- 1

- 2016

- 3d

- 40

- a

- About

- ऊपर

- पहुँच

- तक पहुँचने

- शुद्धता

- वास्तविक

- वास्तव में

- एडीए

- जोड़ना

- पता

- दत्तक ग्रहण

- उन्नत

- लाभ

- फायदे

- फिर

- AI

- एआई प्रशिक्षण

- ऐ / एमएल

- सब

- की अनुमति दी

- की अनुमति देता है

- भी

- हमेशा

- राशि

- an

- विश्लेषण

- विश्लेषिकी

- और

- अन्य

- जवाब

- कोई

- अब

- कहीं भी

- आवेदन

- अनुप्रयोगों

- उचित रूप से

- आर्किटेक्ट

- स्थापत्य

- हैं

- क्षेत्र

- चारों ओर

- व्यवस्था की

- ऐरे

- AS

- पूछ

- पहलू

- पहलुओं

- विधानसभा

- मान लीजिये

- At

- प्रयास

- मोटर वाहन

- उपलब्ध

- दूर

- वापस

- बुरा

- गेंद

- बैंडविड्थ

- बार

- आधारित

- मूल रूप से

- आधार

- BE

- क्योंकि

- बन

- हो जाता है

- किया गया

- से पहले

- जा रहा है

- लाभ

- BEST

- बेहतर

- के बीच

- बड़ा

- बड़ा

- बिट

- टूटना

- लाना

- निर्माण

- बनाया गया

- व्यापार

- व्यापार विकास

- लेकिन

- by

- ताल

- बुलाया

- आया

- कर सकते हैं

- पा सकते हैं

- क्षमताओं

- मामला

- केंद्र

- कुछ

- निश्चित रूप से

- श्रृंखला

- चुनौती

- चुनौतियों

- चुनौतीपूर्ण

- विशेषताएँ

- विशेषताएँ

- जाँच

- टुकड़ा

- चिप्स

- कक्षा

- स्पष्ट

- बादल

- ठंड

- शीतगृह

- संयोजन

- कैसे

- अ रहे है

- सामान्य

- कंपनियों

- कंपनी

- जटिल

- जटिलता

- अनुपालन

- जटिल

- गणना करना

- कंप्यूटर्स

- कंप्यूटिंग

- संकल्पना

- स्थितियां

- जुडिये

- माना

- की कमी

- प्रसंग

- इसके विपरीत

- नियंत्रण

- नियंत्रक

- कन्वर्सेशन (Conversation)

- मूल

- सही

- लागत

- सका

- युगल

- सी पी यू

- बनाता है

- ग्राहक

- ग्राहक

- तिथि

- डाटा केंद्र

- डेटासेट

- दिन

- रोजाना

- दिन

- मृत

- सौदा

- दशकों

- निर्णय

- निश्चित रूप से

- मांग

- निर्भर करता है

- निर्भर करता है

- डिज़ाइन

- डिज़ाइन बनाना

- विस्तृत

- विकास

- युक्ति

- Умереть

- विभिन्न

- मुश्किल

- सीधे

- निदेशक

- चर्चा

- निपटान

- विशिष्ट

- वितरित

- वितरित अभिकलन

- do

- कर देता है

- नहीं करता है

- कर

- डोमेन

- प्रमुख

- किया

- dont

- नीचे

- संचालित

- ड्राइवर

- दौरान

- गतिशील

- शीघ्र

- प्रभाव

- दक्षता

- कुशल

- इलेक्ट्रोनिक

- समाप्त

- ऊर्जा

- अभियांत्रिकी

- संपूर्ण

- वातावरण

- उपकरण

- युग

- त्रुटियाँ

- विशेष रूप से

- ईथर (ईटीएच)

- मूल्यांकन

- मूल्यांकन

- और भी

- अंत में

- प्रत्येक

- सब कुछ

- हर जगह

- विकास

- विकसित करना

- विकसित

- विकसित

- उदाहरण

- एक्सेल

- विस्तारित

- महंगा

- फैली

- चरम

- अत्यंत

- आंखें

- चेहरा

- तथ्य

- कारक

- विफलता

- आकर्षक

- फास्ट

- संभव

- साथी

- निष्ठा

- खेत

- आकृति

- अंत में

- खोज

- प्रथम

- फ़्लैश

- लचीलापन

- फ्लिप

- प्रवाह

- इस प्रकार है

- पदचिह्न

- के लिए

- प्रपत्र

- आगे

- आगे

- पाया

- निष्कपट

- से

- पूर्ण

- आगे

- भविष्य

- मिल

- मिल रहा

- देना

- दी

- वैश्विक

- Go

- चला जाता है

- जा

- सुनहरा

- चला गया

- अच्छा

- अच्छा काम

- मिला

- ग्रिड

- समूह

- बढ़ रहा है

- था

- हैंडलिंग

- हाथ

- खुश

- है

- होने

- सिर

- मदद

- पदक्रम

- हाई

- रखती है

- होम

- आशा

- कैसे

- How To

- एचटीएमएल

- HTTPS

- विशाल

- सैकड़ों

- संकर

- i

- विचार

- if

- कल्पना करना

- असर पड़ा

- प्रभावित

- महत्वपूर्ण

- में सुधार

- in

- प्रोत्साहन

- शामिल

- गलत रूप से

- बढ़ना

- तेजी

- व्यक्ति

- उद्योग

- करें-

- नवोन्मेष

- अंदर

- एकीकृत

- ईमानदारी

- परस्पर

- इंटरफेस

- में

- शामिल

- मुद्दा

- मुद्दों

- IT

- आईटी इस

- खुद

- काम

- केवल

- जानना

- जानने वाला

- प्रयोगशाला

- बड़ा

- बड़ा

- सबसे बड़ा

- विलंब

- बाद में

- परत

- नेतृत्व

- सीख रहा हूँ

- पत्र

- स्तर

- लाइसेंस

- पसंद

- सीमित

- LINK

- लिंक

- स्थानीय

- देखिए

- देख

- लॉट

- बहुत सारे

- निम्न

- बनाए रखना

- बनाना

- निर्माण

- प्रबंध

- प्रबंधक

- विनिर्माण

- बहुत

- बाजार

- अधिकतम-चौड़ाई

- शायद

- me

- साधन

- मतलब

- यांत्रिक

- मध्यम

- -K-on (ITS MY FAVORITE ANIME!)

- याद

- हो सकता है

- मॉडल

- अधिक

- अधिकांश

- चाल

- ले जाया गया

- आंदोलन

- चलती

- बहुत

- my

- आवश्यकता

- की जरूरत है

- कभी नहीँ

- नया

- रात

- नोड्स

- अभी

- संख्या

- of

- बंद

- पुराना

- on

- ONE

- केवल

- खुला

- अवसर

- ऑप्टिमाइज़ करें

- अनुकूलित

- के अनुकूलन के

- विकल्प

- ऑप्शंस

- or

- आदेश

- अन्य

- अन्य

- आउट

- कुल

- काबू

- अपना

- संकुल

- पैकेजिंग

- पृष्ठों

- समानांतर

- भाग

- विशेष

- पास

- पथ

- पथ

- PC

- स्टाफ़

- निष्पादन

- प्रदर्शन

- परिप्रेक्ष्य

- भौतिक

- शारीरिक रूप से

- देवदार

- ग्रह

- प्लेटो

- प्लेटो डेटा इंटेलिजेंस

- प्लेटोडाटा

- बिन्दु

- संभव

- संभावित

- बिजली

- अध्यक्ष

- पहले से

- शायद

- मुसीबत

- प्रोसेसर

- प्रोसेसर

- एस्ट्रो मॉल

- उत्पाद प्रबंधन

- उत्पादन

- कार्यक्रम

- उचित

- अच्छी तरह

- प्रदान करना

- रखना

- प्रश्न

- बिल्कुल

- को ऊपर उठाने

- मूल्यांकन करें

- बल्कि

- पढ़ना

- वास्तव में

- सम्बंधित

- भरोसा करना

- अपेक्षित

- की आवश्यकता होती है

- संकल्प

- जवाब

- परिणाम

- छुटकारा

- सही

- वृद्धि

- भूमिकाओं

- रोल

- रन

- दौड़ना

- वही

- सहेजें

- बचत

- कहावत

- स्केल

- दूसरा

- देखना

- देखकर

- लगता है

- देखा

- अर्थ विज्ञान

- अर्धचालक

- भेजें

- सेंसर

- सेंसर

- सर्वर

- कई

- चादरें

- पाली

- जहाज

- पक्ष

- साइड्स

- सीमेंस

- संकेत

- संकेत

- सिलिकॉन

- समान

- सरल

- अनुकार

- सिमुलेशन

- के बाद से

- एक

- आकार

- स्लॉट्स

- So

- सॉफ्टवेयर

- समाधान

- समाधान ढूंढे

- कुछ

- परिष्कृत

- बोलता हे

- विशेष

- खर्च

- निचोड़

- धुआँरा

- खड़ी

- स्टैकिंग

- मानकीकृत

- दृष्टिकोण

- प्रारंभ

- शुरू

- शुरुआत में

- कदम

- स्टीव

- स्टीवनऊ

- फिर भी

- भंडारण

- की दुकान

- संघर्ष

- ऐसा

- समर्थित

- निश्चित

- प्रणाली

- सिस्टम

- तालिका

- लेना

- बातचीत

- टीमों

- टैकनोलजिस्ट

- टेक्नोलॉजी

- शर्तों

- परीक्षण

- परीक्षण

- परीक्षण

- से

- कि

- RSI

- भविष्य

- लेकिन हाल ही

- उन

- फिर

- वहाँ।

- थर्मल

- इन

- वे

- बात

- चीज़ें

- सोचना

- तीसरा

- इसका

- उन

- विचार

- यहाँ

- पहर

- सेवा मेरे

- आज

- एक साथ

- साधन

- उपकरण

- ऊपर का

- पूरी तरह से

- समझौतों से

- परंपरागत

- पारंपरिक रूप से

- प्रशिक्षण

- परिवहन

- प्रवृत्ति

- <strong>उद्देश्य</strong>

- की कोशिश कर रहा

- दो

- दो तिहाई

- टाइप

- समझना

- इकाइयों

- विश्वविद्यालय

- us

- उपयोग

- प्रयुक्त

- का उपयोग

- सत्यापन

- मूल्य

- विविधताओं

- विभिन्न

- बहुत

- उपाध्यक्ष

- वाइस राष्ट्रपति

- देखें

- वास्तविक

- की

- घूमना

- दीवार

- करना चाहते हैं

- था

- मार्ग..

- we

- भार

- कुंआ

- थे

- क्या

- जो कुछ

- कब

- या

- कौन कौन से

- जब

- सफेद

- पूरा का पूरा

- क्यों

- मर्जी

- साथ में

- बिना

- वू

- काम

- घर से काम

- काम कर रहे

- वर्स्ट

- लिख रहे हैं

- इसलिए आप

- आपका

- जेफिरनेट