1980 के दशक में समाक्षीय केबल पर 10Mbps साझा LAN के साथ शुरुआत के बाद से, ईथरनेट ने लगातार प्रगति देखी है, अब 1.6Tbps तक की गति का समर्थन करने की क्षमता के साथ। इस प्रगति ने ईथरनेट को विश्वसनीय पैकेट स्थानांतरण और सेवा की गुणवत्ता के महत्व पर जोर देते हुए, लाइव स्ट्रीमिंग, रेडियो एक्सेस नेटवर्क और औद्योगिक नियंत्रण जैसे अनुप्रयोगों की एक विस्तृत श्रृंखला की सेवा करने की अनुमति दी है। मौजूदा इंटरनेट बैंडविड्थ ~500 टीबीपीएस पर होने के कारण, बेहतर बैक-एंड इंट्रा डेटासेंटर ट्रैफिक हैंडलिंग की मांग बढ़ रही है। हालाँकि व्यक्तिगत सर्वर अभी तक टेराबिट-प्रति-सेकंड स्तर पर काम नहीं कर रहे हैं, समग्र डेटासेंटर ट्रैफ़िक इस पैमाने के करीब है, जिससे IEEE के 802.3dj समूह को मानकीकरण प्रयास करने के लिए प्रेरित किया जा रहा है और विस्तारित डेटा प्रवाह को प्रबंधित करने के लिए मजबूत ईथरनेट नियंत्रकों और सर्डेस की आवश्यकता हो रही है। बढ़ती मांगों की इस पृष्ठभूमि के बीच, इंटरप्रोसेसर संचार पहले से ही इन गतियों पर जोर दे रहा है।

इंटरप्रोसेसर संचार न्यूनतम विलंबता के साथ 1.6T दरों की आवश्यकता का नेतृत्व कर रहा है। जबकि व्यक्तिगत उपकरण उनकी अंतर्निहित प्रसंस्करण क्षमताओं और चिप आकार द्वारा प्रतिबंधित हैं, चिप्स के संयोजन से इन क्षमताओं में काफी वृद्धि हो सकती है। अनुप्रयोगों की पहली पीढ़ी के बाद इंट्रा डेटासेंटर स्विच-टू-स्विच कनेक्शन होने की उम्मीद है, जो उच्च-प्रदर्शन प्रोसेसर और मेमोरी की पूलिंग को सक्षम करेगा, क्लाउड कंप्यूटिंग के भीतर स्केलेबिलिटी और दक्षता को बढ़ाएगा।

IEEE की 802.3dj पहल: 1.6 Tbps इंटरऑपरेबिलिटी के लिए ईथरनेट मानकों को आगे बढ़ाना

निर्बाध पारिस्थितिकी तंत्र अंतरसंचालनीयता के लिए विकसित मानकीकरण प्रयासों का अनुपालन महत्वपूर्ण है। IEEE का 802.3dj समूह आगामी ईथरनेट मानक तैयार करने की प्रक्रिया में है, जिसमें 200G से 1.6 टेराबिट प्रति सेकंड तक की गति के लिए भौतिक परतें और प्रबंधन पैरामीटर शामिल हैं। समूह का उद्देश्य 1.6 टीबीपीएस ईथरनेट मैक डेटा दर है, जिसका लक्ष्य मैक परत पर अधिकतम बिट त्रुटि दर 10-13 से अधिक नहीं है। आगे के प्रावधानों में वैकल्पिक 16 और 8 लेन अटैचमेंट यूनिट इंटरफेस (एयूआई) शामिल हैं जो विभिन्न चिप अनुप्रयोगों के लिए उपयुक्त हैं, 112जी और 224जी सर्डेस का लाभ उठाते हैं। भौतिक रूप से, 1.6Tbps विनिर्देश में एक मीटर तक के लिए 8 जोड़ी कॉपर ट्विनैक्स केबल और 8 मीटर से 500 किमी के बीच की दूरी के लिए 2 जोड़ी फाइबर के माध्यम से संचरण शामिल है। हालाँकि मानक का पूर्ण अनुसमर्थन वसंत 2026 तक होने की उम्मीद है, सुविधाओं का मुख्य सेट 2024 में पूरा होने का अनुमान है।

1.6T ईथरनेट सबसिस्टम में बैंडविड्थ ओवरहेड और त्रुटि सुधार

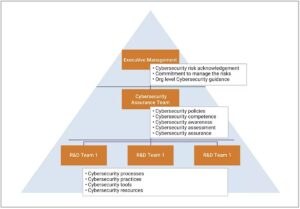

चित्र 1: 1.6टी ईथरनेट सबसिस्टम के घटकों को दर्शाने वाला आरेख।

पहले के ईथरनेट पुनरावृत्तियों में, पीसीएस मुख्य रूप से विश्वसनीय पैकेट पहचान के लिए डेटा एन्कोडिंग पर केंद्रित था। हालाँकि, 1.6T ईथरनेट गति में वृद्धि के साथ, फॉरवर्ड एरर करेक्शन (FEC) की आवश्यकता स्पष्ट हो जाती है, विशेष रूप से छोटे लिंक पर भी सिग्नल गिरावट का प्रतिकार करने के लिए। इस प्रयोजन के लिए, 1.6T ईथरनेट रीड-सोलोमन FEC का उपयोग जारी रखता है। यह दृष्टिकोण एक कोडवर्ड बनाता है जिसमें 514 10-बिट प्रतीकों को 544 प्रतीक ब्लॉक में एन्कोड किया जाता है, जिसके परिणामस्वरूप 6% बैंडविड्थ ओवरहेड होता है। ये FEC कोडवर्ड AUI भौतिक लिंक में वितरित किए जाते हैं ताकि प्रत्येक भौतिक लिंक (8T ईथरनेट के लिए 1.6) में संपूर्ण कोडवर्ड न हो। यह विधि न केवल त्रुटि विस्फोटों के विरुद्ध अतिरिक्त सुरक्षा प्रदान करती है, बल्कि दूर के डिकोडर पर समानांतरीकरण को भी सक्षम बनाती है, जिससे विलंबता कम हो जाती है।

गियरबॉक्स और सर्डेस की विशेषता वाला फिजिकल मीडियम अटैचमेंट (पीएमए), प्रसारित चैनलों पर ईथरनेट सिग्नल लाता है। 1.6T ईथरनेट के लिए, इसमें 8Gbps पर चलने वाले 212 चैनल शामिल हैं, जो 6% FEC ओवरहेड के लिए जिम्मेदार हैं। नियोजित मॉड्यूलेशन तकनीक 4-लेवल पल्स एम्प्लिट्यूड मॉड्यूलेशन (PAM-4) है, जो प्रत्येक ट्रांसमिशन सिंबल के लिए दो डेटा बिट्स को एनकोड करता है, जिससे पारंपरिक नॉन-रिटर्न जीरो (NRZ) दृष्टिकोण के साथ तुलना करने पर बैंडविड्थ प्रभावी रूप से दोगुना हो जाता है। ट्रांसमिशन तंत्र डिजिटल-से-एनालॉग रूपांतरण पर निर्भर करता है, जबकि प्राप्त अंत पर डीएसपी के साथ संयुक्त एनालॉग-टू-डिजिटल रूपांतरण सटीक सिग्नल निष्कर्षण सुनिश्चित करता है।

इसके अलावा, यह ध्यान रखना महत्वपूर्ण है कि ईथरनेट पीसीएस एक "बाहरी एफईसी" पेश करता है जो ईथरनेट लिंक पर शुरू से अंत तक फैला होता है। लंबी पहुंच वाले चैनलों को मजबूत करने के लिए, व्यक्तिगत भौतिक लाइनों के लिए त्रुटि सुधार की एक अतिरिक्त परत पाइपलाइन में है, संभवतः हैमिंग कोड एफईसी को अपनाया जा रहा है। इस सुधार का प्राथमिक अनुप्रयोग ऑप्टिकल ट्रांसीवर मॉड्यूल में होने की उम्मीद है जहां ऐसा सुधार अनिवार्य है।

चित्र 2: विस्तारित पहुंच के लिए संयोजित एफईसी का उपयोग करते समय जोड़े गए अतिरिक्त ओवरहेड को दर्शाने वाला आरेख।

चित्र 2 में दर्शाए गए उदाहरण सिस्टम में, MAC और PCS एक ऑप्टिकल मॉड्यूल और एक फाइबर स्ट्रेच के माध्यम से जुड़े हुए हैं। पीसीएस में बिट त्रुटि दर 10 है-5 ऑप्टिकल मॉड्यूल लिंक पर, साथ ही ऑप्टिकल लिंक से त्रुटियाँ। 10 को प्राप्त करने के लिए एकमात्र आरएस-एफईसी का एंड-टू-एंड उपयोग करना पर्याप्त नहीं होगा-13 ईथरनेट मानक, जो लिंक को अविश्वसनीय बनाता है। एक विकल्प यह होगा कि प्रत्येक हॉप पर अलग-अलग आरएस एफईसी का ट्रिपल कार्यान्वयन किया जाए, जिससे लागत और विलंबता में उल्लेखनीय वृद्धि होगी। एक अधिक प्रभावी समाधान विशेष रूप से ऑप्टिकल लिंक के लिए एक संयोजित हैमिंग कोड एफईसी का एकीकरण है, जो ऑप्टिकल कनेक्शन की विशिष्ट यादृच्छिक त्रुटियों को पूरा करता है। यह आंतरिक FEC परत 212 Gbps से 226 Gbps तक लाइन दर का अतिरिक्त विस्तार करती है, इस प्रकार यह आवश्यक है कि SerDes इस लाइन दर का समर्थन कर सके।

1.6T ईथरनेट सिस्टम में विलंबता चुनौतियाँ

चित्र 3: 1.6T ईथरनेट सबसिस्टम के लिए विलंबता पथ।

विभिन्न घटक ईथरनेट विलंबता में योगदान करते हैं: ट्रांसमिट कतार, ट्रांसमिशन अवधि, मध्यम ट्रैवर्सल समय, और कई प्रसंस्करण और रसीद समय। इसकी कल्पना करने के लिए, चित्र 3 पर विचार करें, जो एक व्यापक 1.6T ईथरनेट सबसिस्टम प्रदर्शित करता है। जबकि विलंबता दूर-अंत एप्लिकेशन के प्रतिक्रिया समय से प्रभावित हो सकती है, यह कारक ईथरनेट के लिए बाहरी है और इसलिए अक्सर विलंबता विश्लेषण के दौरान इसे बाहर रखा जाता है। ईथरनेट इंटरफ़ेस पर विलंबता को कम करने के लिए विशिष्ट परिस्थितियों को समझने की आवश्यकता होती है। उदाहरण के लिए, धीमे क्लाइंट लिंक पर अंतर्निहित देरी के कारण स्विच के बीच ट्रंक कनेक्शन के लिए विलंबता प्राथमिक चिंता नहीं हो सकती है। दूरी भी एक भूमिका निभाती है; अधिक लंबाई अधिक विलंबता लाती है। बेशक, इसका मतलब यह नहीं है कि हमें अन्य परिदृश्यों में विलंबता को नजरअंदाज करना चाहिए, विलंबता को कम करना हमेशा एक उद्देश्य होता है।

ट्रांसमिशन विलंबता स्वाभाविक रूप से ईथरनेट दर और फ़्रेम आकार से जुड़ी होती है। विशेष रूप से, 1.6T ईथरनेट सिस्टम के लिए, न्यूनतम आकार के पैकेट को प्रसारित करने के लिए 0.4ns की आवश्यकता होती है - अनिवार्य रूप से, 2.5 GHz घड़ी की प्रति टिक एक ईथरनेट फ्रेम। दूसरी ओर, एक मानक अधिकतम आकार के फ्रेम को प्रसारित करने में 8ns लगते हैं, जो जंबो फ्रेम्स के लिए 48ns तक बढ़ जाता है। चुना गया माध्यम विलंबता को और निर्धारित करता है। उदाहरण के लिए, ऑप्टिकल फाइबर में आमतौर पर 5ns प्रति मीटर की विलंबता होती है, जबकि कॉपर केबलिंग में 4ns प्रति मीटर की विलंबता थोड़ी तेज होती है।

समग्र विलंबता का एक बड़ा हिस्सा रिसीवर नियंत्रक में निहित है। आरएस एफईसी डिकोडर स्वाभाविक रूप से विलंबता का परिचय देता है। त्रुटि सुधार आरंभ करने के लिए, सिस्टम को 4 कोडवर्ड प्राप्त होने चाहिए, जो 1.6Tbps पर, 12.8ns के बराबर है। त्रुटि सुधार और बफ़रिंग सहित बाद की गतिविधियाँ, इस विलंबता को बढ़ाती हैं। जबकि एफईसी कोडवर्ड भंडारण अवधि सुसंगत रहती है, संदेश प्राप्त करने के दौरान विलंबता विशिष्ट कार्यान्वयन पर निर्भर होती है। फिर भी, सावधानीपूर्वक डिजिटल डिज़ाइन रणनीतियों को नियोजित करके विलंबता को अनुकूलित किया जा सकता है।

संक्षेप में, एफईसी तंत्र और भौतिक दूरी या केबल की लंबाई के कारण एक अंतर्निहित, अपरिहार्य विलंबता है। इन कारकों के अलावा, डिज़ाइन विशेषज्ञता ईथरनेट नियंत्रक विलंबता को कम करने में महत्वपूर्ण भूमिका निभाती है। एक पूर्ण समाधान का लाभ उठाना जो MAC, PCS और PHY को एकीकृत और अनुकूलित करता है, सबसे कुशल, कम विलंबता कार्यान्वयन का मार्ग प्रशस्त करता है।

सारांश

चित्र 4: 224एनएम प्रक्रिया में सिनोप्सिस 3जी ईथरनेट पीएचवाई आईपी के लिए प्रथम-पास सिलिकॉन सफलता, अत्यधिक रैखिक पीएएम-4 आंखों को प्रदर्शित करती है।

1.6 टीबीपीएस ईथरनेट सबसे अधिक बैंडविड्थ की मांग और विलंबता संवेदनशील अनुप्रयोगों के लिए तैयार किया गया है। 224G सर्डेस तकनीक के उद्भव के साथ, MAC और PCS IP में प्रगति के साथ, व्यापक समाधान अब उपलब्ध हैं जो लगातार विकसित हो रहे 1.6T ईथरनेट मानकों के अनुरूप हैं। इसके अतिरिक्त, प्रोटोकॉल और त्रुटि सुधार विधियों में अंतर्निहित विलंबता के कारण, डेटापथ में अनावश्यक विलंबता शुरू करने से बचने के लिए आईपी डिजिटल और एनालॉग डिज़ाइन को विशेषज्ञ डिजाइनरों द्वारा परिश्रमपूर्वक तैयार किया जाना चाहिए।

1.6T SoC डिज़ाइन के लिए शीर्ष प्रदर्शन प्राप्त करने के लिए प्रत्येक चिप घटक के लिए कुशलतापूर्वक अनुकूलित वास्तुकला और सावधानीपूर्वक डिज़ाइन प्रथाओं की आवश्यकता होती है। यह बिजली संरक्षण पर जोर देता है और सिलिकॉन पदचिह्न को कम करता है, जिससे 1.6T डेटा दरें वास्तविकता बन जाती हैं। सिलिकॉन-सिद्ध सिनोप्सिस 224जी ईथरनेट पीएचवाई आईपी ने 1.6T MAC और PCS नियंत्रक के लिए मंच तैयार कर दिया है। अग्रणी डिजाइन, विश्लेषण, सिमुलेशन और माप तकनीकों का उपयोग करते हुए, सिनोप्सिस असाधारण सिग्नल अखंडता और घबराहट प्रदर्शन प्रदान करना जारी रखता है। MAC+PCS+PHY सहित संपूर्ण ईथरनेट समाधान.

- एसईओ संचालित सामग्री और पीआर वितरण। आज ही प्रवर्धित हो जाओ।

- प्लेटोडेटा.नेटवर्क वर्टिकल जेनरेटिव एआई। स्वयं को शक्तिवान बनाएं। यहां पहुंचें।

- प्लेटोआईस्ट्रीम। Web3 इंटेलिजेंस। ज्ञान प्रवर्धित। यहां पहुंचें।

- प्लेटोईएसजी. कार्बन, क्लीनटेक, ऊर्जा, पर्यावरण, सौर, कचरा प्रबंधन। यहां पहुंचें।

- प्लेटोहेल्थ। बायोटेक और क्लिनिकल परीक्षण इंटेलिजेंस। यहां पहुंचें।

- स्रोत: https://semiengineering.com/latency-considerations-for-1-6t-ethernet-designs/

- :हैस

- :है

- :नहीं

- :कहाँ

- $यूपी

- 1

- 12

- 16

- 2024

- 2026

- 212

- 220

- 362

- 500

- 8

- a

- पहुँच

- सुलभ

- लेखांकन

- सही

- पाना

- के पार

- गतिविधियों

- जोड़ा

- अतिरिक्त

- इसके अतिरिक्त

- अपनाने

- प्रगति

- आगे बढ़ने

- के खिलाफ

- एमिंग

- की अनुमति दी

- पहले ही

- भी

- हालांकि

- हमेशा

- बीच में

- राशियाँ

- बढ़ाना

- an

- विश्लेषण

- और

- प्रत्याशित

- आवेदन

- अनुप्रयोगों

- दृष्टिकोण

- स्थापत्य

- हैं

- AS

- At

- से बचने

- बैक-एंड

- पृष्ठभूमि

- बैंडविड्थ

- BE

- हो जाता है

- के बीच

- परे

- बिट

- खंड

- सिलेंडर

- बढ़ाने

- लाता है

- बनाता है

- लेकिन

- by

- केबल

- केबल

- कर सकते हैं

- क्षमता

- ले जाना

- चुनौतियों

- चैनलों

- टुकड़ा

- चिप्स

- करने के लिए चुना

- हालत

- ग्राहक

- घड़ी

- बादल

- बादल कंप्यूटिंग

- कोड

- संयुक्त

- संयोजन

- संचार

- पूरा

- समापन

- अंग

- घटकों

- व्यापक

- शामिल

- कंप्यूटिंग

- चिंता

- संयोजन

- जुड़ा हुआ

- कनेक्शन

- संरक्षण

- विचार करना

- विचार

- संगत

- जारी

- लगातार

- योगदान

- नियंत्रण

- नियंत्रक

- रूपांतरण

- तांबा

- मूल

- लागत

- प्रतिक्रिया

- पाठ्यक्रम

- तैयार

- बनाता है

- वर्तमान

- तिथि

- डेटासेंटर

- प्रथम प्रवेश

- देरी

- उद्धार

- मांग

- मांग

- मांग

- चित्रण

- डिज़ाइन

- डिजाइनरों

- डिजाइन

- खोज

- डिवाइस

- बातें

- विभिन्न

- डिजिटल

- लगन से

- प्रदर्शित करता है

- दूरी

- वितरित

- नहीं करता है

- दोहरीकरण

- दो

- अवधि

- दौरान

- से प्रत्येक

- पूर्व

- पारिस्थितिकी तंत्र

- प्रभावी

- प्रभावी रूप से

- दक्षता

- कुशल

- कुशलता

- प्रयासों

- उद्भव

- पर जोर देती है

- पर बल

- कार्यरत

- रोजगार

- सक्षम बनाता है

- समर्थकारी

- अंतर्गत कई

- समाप्त

- शुरू से अंत तक

- सुनिश्चित

- संपूर्ण

- त्रुटि

- त्रुटियाँ

- गहरा हो जाना

- सार

- आवश्यक

- अनिवार्य

- ईथर (ईटीएच)

- और भी

- प्रत्येक

- स्पष्ट

- उद्विकासी

- उदाहरण

- असाधारण

- अपवर्जित

- का विस्तार

- विस्तार

- अपेक्षित

- विशेषज्ञ

- विशेषज्ञता

- विस्तार

- का विस्तार

- बाहरी

- निष्कर्षण

- आंखें

- कारक

- कारकों

- दूर

- और तेज

- विशेषताएं

- की विशेषता

- आकृति

- खोज

- प्रथम

- पहली पीढ़ी

- प्रवाह

- ध्यान केंद्रित

- पीछा किया

- पदचिह्न

- के लिए

- तैयार करने

- आगे

- फ्रेम

- से

- आगे

- पीढ़ी

- देता है

- अधिक से अधिक

- समूह

- समूह की

- बढ़ रहा है

- हाथ

- हैंडलिंग

- हाई

- उच्च प्रदर्शन

- अत्यधिक

- तथापि

- एचटीएमएल

- HTTPS

- अनिवार्य

- कार्यान्वयन

- महत्व

- महत्वपूर्ण

- उन्नत

- in

- अन्य में

- शामिल

- सहित

- बढ़ती

- व्यक्ति

- औद्योगिक

- प्रभावित

- निहित

- स्वाभाविक

- आरंभ

- पहल

- उदाहरण

- एकीकृत

- एकीकरण

- ईमानदारी

- इंटरफेस

- इंटरफेस

- इंटरनेट

- इंटरोऑपरेबिलिटी

- में

- आंतरिक

- परिचय कराना

- द्वारा प्रस्तुत

- शुरू करने

- शामिल

- IP

- IT

- पुनरावृत्तियों

- आईटी इस

- खुद

- जेपीजी

- लेन

- विलंब

- परत

- परतों

- लंबाई

- स्तर

- लाभ

- संभावित

- लाइन

- पंक्तियां

- LINK

- लिंक

- जीना

- लंबे समय तक

- निम्न

- मैक

- निर्माण

- प्रबंधन

- प्रबंध

- अधिकतम-चौड़ाई

- अधिकतम

- मई..

- मतलब

- माप

- तंत्र

- मध्यम

- याद

- message

- तरीका

- तरीकों

- सूक्ष्म

- कम से कम

- कम से कम

- कम करता है

- कम से कम

- मॉड्यूल

- मॉड्यूल

- अधिक

- अधिकांश

- चाहिए

- होने जा रही

- आवश्यकता

- नेटवर्क

- फिर भी

- नहीं

- नोट

- अभी

- उद्देश्य

- of

- अक्सर

- on

- ONE

- केवल

- परिचालन

- अनुकूलित

- अनुकूलन

- विकल्प

- or

- अन्य

- के ऊपर

- कुल

- जोड़े

- पैरामीटर

- विशेष रूप से

- पथ

- पीसी

- प्रति

- प्रदर्शन

- प्रदर्शन

- भौतिक

- शारीरिक रूप से

- पाइपलाइन

- केंद्रीय

- प्लेटो

- प्लेटो डेटा इंटेलिजेंस

- प्लेटोडाटा

- निभाता

- प्लस

- संभावित

- बिजली

- प्रथाओं

- मुख्यत

- प्राथमिक

- प्रक्रिया

- प्रसंस्करण

- प्रोसेसर

- प्रगति

- प्रक्षेपित

- सुरक्षा

- प्रोटोकॉल

- नाड़ी

- उद्देश्य

- धक्का

- गुणवत्ता

- रेडियो

- बिना सोचे समझे

- रेंज

- मूल्यांकन करें

- दरें

- पहुंच

- तक पहुंच गया

- प्रतिक्रिया

- वास्तविकता

- प्राप्त करना

- प्राप्त

- स्वागत

- को कम करने

- विश्वसनीय

- बाकी है

- प्रतिपादन

- की आवश्यकता होती है

- प्रतिबंधित

- जिसके परिणामस्वरूप

- मजबूत

- भूमिका

- जड़ें

- दौड़ना

- अनुमापकता

- स्केल

- परिदृश्यों

- निर्बाध

- दूसरा

- देखा

- खंड

- संवेदनशील

- अलग

- सेवा

- सेवा

- सेट

- कई

- साझा

- कम

- चाहिए

- को दिखाने

- संकेत

- काफी

- सिलिकॉन

- अनुकार

- आकार

- So

- समाधान

- समाधान ढूंढे

- फैला

- अगुआई

- विशिष्ट

- विशेष रूप से

- विनिर्देश

- गति

- वसंत

- ट्रेनिंग

- मानक

- मानकीकरण

- मानकों

- भंडारण

- रणनीतियों

- स्ट्रीमिंग

- आगामी

- पर्याप्त

- सफलता

- ऐसा

- उपयुक्त

- समर्थन

- प्रतीक

- प्रणाली

- अनुरूप

- लेता है

- तकनीक

- तकनीक

- टेक्नोलॉजी

- से

- कि

- RSI

- लेकिन हाल ही

- वहाँ।

- जिसके चलते

- इसलिये

- इन

- इसका

- यहाँ

- इस प्रकार

- टिकटिक

- बंधा होना

- पहर

- बार

- सेवा मेरे

- ऊपर का

- परंपरागत

- यातायात

- स्थानांतरण

- संचारित करना

- ट्रिपल

- दो

- ठेठ

- आम तौर पर

- अनिवार्य

- समझ

- शुरू

- इकाई

- आगामी

- के ऊपर

- का उपयोग

- उपयोग

- के माध्यम से

- कल्पना

- मार्ग..

- we

- कब

- कौन कौन से

- जब

- व्यापक

- साथ में

- अंदर

- होगा

- अभी तक

- जेफिरनेट

- शून्य