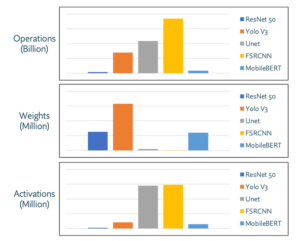

La vérité est que nous ne sommes qu'au début de la révolution de l'intelligence artificielle (IA). Les capacités de l'IA commencent tout juste à montrer des indices sur ce que l'avenir nous réserve. Par exemple, les voitures utilisent de grands modèles de réseaux neuronaux complexes non seulement pour comprendre leur environnement, mais aussi pour se diriger et se contrôler. Pour toute application, il doit y avoir des données de formation pour créer des réseaux utiles. La taille des opérations de formation et d'inférence augmente rapidement à mesure que des données utiles du monde réel sont incorporées dans les modèles. Examinons la croissance des modèles au cours des dernières années pour comprendre comment cela entraîne les besoins en puissance de traitement pour la formation et l'inférence.

Dans une présentation au Ansys 2021 Ideas Digital Forum, le vice-président de l'ingénierie chez Cerebras, Dhiraj Mallik, a donné un aperçu de la croissance des modèles de réseaux neuronaux. Au cours des deux dernières années, la taille du modèle a été multipliée par 1000, passant de BERT Base (110 Mo) à GPT-3 (175 Go). Et en perspective, il y a le modèle MSFT-1T, d'une taille de 1 To. Le modèle GPT-3 - qui est un sujet intéressant en soi - a été formé avec du matériel conventionnel utilisant 1024 GPU pendant 4 mois. Il s'agit d'un modèle de traitement du langage naturel (NLP) qui utilise la plupart des données textuelles sur Internet et d'autres sources. Il a été développé par Open AI et constitue désormais la base du codex OpenAI, qui est une application capable d'écrire du code de programmation utile dans plusieurs langages à partir des instructions en langage clair des utilisateurs. GPT-3 peut être utilisé pour écrire de courts articles dont la majorité des lecteurs ne peuvent pas dire qu'ils ont été écrits par un programme d'IA.

Comme vous pouvez le voir ci-dessus, faire fonctionner 1024 GPU pendant 4 mois n'est pas faisable. Dans son exposé intitulé « Delivering Unprecedented AP Acceleration: Beyond Moore's Law », Dhiraj souligne que les progrès nécessaires pour soutenir ce niveau de croissance des semi-conducteurs vont bien au-delà de ce que nous avons l'habitude de voir avec la loi de Moore. En réponse à ce besoin perçu du marché, Cerebras a lancé son moteur d'IA WSE-1 à l'échelle d'une tranche en 2019 - 56 fois plus grand que n'importe quelle puce jamais produite. Un an et demi plus tard, ils ont annoncé le WSE-2, encore une fois la plus grande puce jamais construite avec :

- 6 XNUMX milliards de transistors

- 850,000 XNUMX cœurs d'IA optimisés

- 40 Go de RAM

- Bande passante mémoire de 20 pétaoctets/s

- Bande passante de structure de 220 pétaoctets

- Construit avec le processus N7 de TSMC

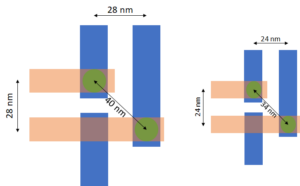

- Une plaquette contient 84 matrices de 550 mm chacune2.

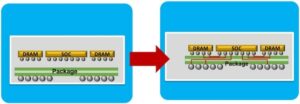

Le système CS-2 qui encapsule le WSE-2 peut s'adapter à des modèles d'IA avec 120 2 milliards de paramètres. Ce qui est encore plus impressionnant, c'est que les systèmes CS-192 peuvent être intégrés dans des clusters de XNUMX unités pour fournir des gains de performances quasi linéaires. Cerebras a développé un sous-système de mémoire qui désagrège la mémoire et le calcul pour fournir une meilleure mise à l'échelle et un débit amélioré pour les modèles extrêmement volumineux. Cerebras a également développé des optimisations pour la parcimonie dans les ensembles d'entraînement, ce qui permet d'économiser du temps et de l'énergie.

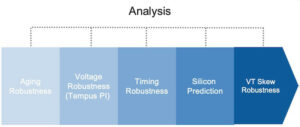

La présentation de Dhiraj détaille leurs capacités, en particulier dans le domaine de la mise à l'échelle efficace avec des modèles plus grands pour maintenir le débit et la capacité. Du point de vue des semi-conducteurs, il est également intéressant de voir comment Cerebras a analysé la baisse IR, l'électromigration et l'approbation ESD sur une conception qui est de 2 ordres de grandeur plus grande que tout ce qui a jamais été tenté par l'industrie des semi-conducteurs. Dhiraj explique comment à chaque niveau de la conception - tuile, bloc et plaquette complète - Cerebras a utilisé Ansys RedHawk-SC sur plusieurs processeurs pour l'approbation de chute IR statique et dynamique. RedHawk-SC a également été utilisé pour les contrôles d'électromigration de puissance et d'électromigration de signal. De même, ils ont utilisé Ansys Pathfinder pour les contrôles de résistance ESD et de densité de courant.

Avec un morceau de silicium de cette taille à 7 nm, les décisions d'outil sont littéralement "ça passe ou ça casse". Construire du silicium aussi perturbateur nécessite de nombreux choix très réfléchis dans le processus de développement, et une capacité inégalée est bien sûr une préoccupation majeure. Pourtant, comme le montre clairement la présentation de Dhiraj, le niveau de puissance de traitement accru de CS-2 est nécessaire pour gérer le taux de croissance que nous observons dans les modèles AI/ML. Sans aucun doute, nous verrons des innovations qui dépassent notre imagination aujourd'hui dans le domaine de l'IA. Tout comme le Web et le cloud ont modifié la technologie et même la société, nous pouvons nous attendre à ce que le développement de nouvelles technologies d'IA change radicalement notre monde. Si vous souhaitez en savoir plus sur le silicium Cerebras, consultez la présentation de Dhiraj sur le forum numérique Ansys IDEAS à l'adresse www.ansys.com/idées.

Partagez cet article via: Source : https://semiwiki.com/eda/303587-neural-network-growth-requires-unprecedented-semiconductor-scaling/

- 000

- 110

- 2019

- 2021

- 84

- AI

- annoncé

- Application

- Réservé

- sur notre blog

- Développement

- Compétences

- voitures

- Change

- Contrôles

- puce

- le cloud

- code

- Courant

- données

- Conception

- détail

- Développement

- numérique

- Goutte

- ENGINEERING

- Environment

- .

- s'adapter

- plein

- avenir

- GPU

- Croissance

- Croissance

- Matériel

- Comment

- HTTPS

- industrie

- Internet

- IT

- langue

- Langues

- gros

- Droit applicable et juridiction compétente

- apprentissage

- Niveau

- Majorité

- Marché

- modèle

- mois

- Langage naturel

- Traitement du langage naturel

- Près

- réseau et

- réseaux

- Neural

- Réseau neuronal

- nlp

- ouvert

- OpenAI

- Opérations

- passer commande

- Autre

- performant

- objectifs

- power

- Produit

- Programme

- Programmation

- lecteurs

- réponse

- pour le running

- Escaliers intérieurs

- échelle ai

- mise à l'échelle

- semi-conducteur

- Shorts

- Taille

- Société

- Support

- combustion propre

- Système

- Talks

- Technologie

- El futuro

- fiable

- Formation

- utilisateurs

- web

- Qu’est ce qu'

- world

- an

- années