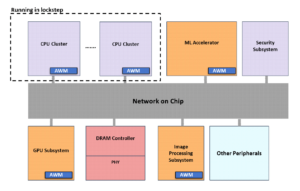

La vieille phrase selon laquelle le remède est pire que le mal est à propos lors de la discussion de MBIST pour les grands SOC où l'exécution de nombreux tests MBIST en parallèle peut dépasser les capacités du réseau de distribution d'énergie (PDN). L'auto-test intégré de la mémoire (MBIST) s'exécute généralement automatiquement lors des événements de mise sous tension. En raison de la volonté d'accélérer les temps de démarrage des tests et des puces, ces tests sont fréquemment exécutés en parallèle. Le problème est qu'ils peuvent facilement produire une activité de commutation qui est d'un ordre de grandeur au-dessus des niveaux trouvés lors du fonctionnement normal de la puce. En effet, ces niveaux d'activité de commutation plus élevés peuvent non seulement provoquer une chute de l'alimentation affectant les résultats des tests, mais également la chaleur élevée générée peut endommager les puces. Ces effets peuvent conduire à un regroupement incorrect ou à des échecs directs et latents.

La solution consiste à simuler l'activité MBIST pour prédire la charge sur le PDN et les effets thermiques associés. Avec les résultats de la simulation en main, les concepteurs peuvent décider correctement combien et quels blocs de mémoire peuvent être testés en parallèle. Cependant, cela n'est pas toujours faisable dans les grands SOC avec de nombreux blocs de mémoire car les temps de simulation peuvent être prohibitifs. Avec un niveau de porte et une simulation RTL encore moins précise, il peut ne pas être possible d'exécuter suffisamment de cycles pour obtenir les informations nécessaires.

Dans un livre blanc intitulé "Analyzing the power implications of MBIST use", Siemens EDA examine comment les concepteurs peuvent exécuter une simulation suffisante pour prendre des décisions éclairées sur la stratégie de test avant le tapeout. Siemens a travaillé avec ARM sur l'une de leurs puces de test pour créer un cas de test où ils pourraient appliquer une émulation matérielle avec les applications DFT et Power pour l'émulateur matériel Siemens Veloce. Tout d'abord, l'application Veloce DFT est utilisée pour générer l'activité interne pendant l'émulation MBIST. L'application utilise le langage d'interface de test standard (STIL) et produit des fichiers de sortie standard de l'industrie.

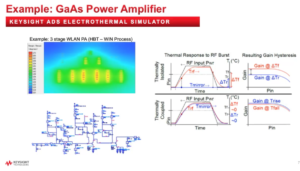

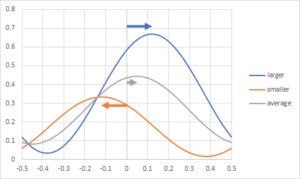

L'application Veloce Power prend les informations d'activité des exécutions MBIST pour générer des formes d'onde, des profils de puissance et des cartes thermiques qui peuvent indiquer quand il y a des pics de puissance au-dessus des limites spécifiées. Avec ces informations, les ingénieurs de test peuvent prendre des décisions éclairées sur le séquençage de MBIST.

Le cas de test ARM décrit dans le livre blanc de Siemens contient 176 millions de portes. Siemens a utilisé un système Veloce avec 6 cartes Veloce Strato pour ce cas de test. L'exécution de l'émulateur Veloce n'a pris que 26 heures, ce qui est 15,600 XNUMX fois plus rapide que la simulation au niveau de la porte. Un autre avantage du flux Veloce est que les informations d'activité sont transmises par l'application Power aux outils électriques du flux, ce qui permet d'économiser de l'espace disque et du temps. Les résultats du cas de test ont montré plusieurs pointes de puissance qui enfreignaient les spécifications de conception du SOC. La sortie de l'application Veloce Power montre les niveaux de puissance totaux à travers la simulation ainsi que les contributions de puissance séparées pour l'horloge, la logique combinatoire et la mémoire. De même, il y a des informations sur l'endroit où le pouvoir est utilisé sur le dé. Ces informations permettent de déterminer facilement où se situent les problèmes.

Trouver de tels problèmes nécessite d'exécuter des millions ou des milliards de cycles d'horloge. Les limites des simulateurs logiciels rendent prohibitif l'exécution de l'analyse nécessaire. L'émulation offre une voie unique pour examiner de près les impacts de puissance de MBIST et d'autres opérations de test bien avant le silicium. Le livre blanc de Siemens offre un aperçu de la méthode de puissance utilisée sur un cas de test réel. Le livre blanc est disponible en téléchargement pour lecture sur le site Web de Siemens.

Partagez cet article via: Source : https://semiwiki.com/eda/306889-mbist-power-creates-lurking-danger-for-socs/

- Qui sommes-nous

- selon une analyse de l’Université de Princeton

- appli

- applications

- BRAS

- disponibles

- va

- Causes

- puce

- chips

- horloge

- contient

- pourriez

- soins

- Conception

- Maladie

- pendant

- même

- Les ingénieurs

- événement

- événements

- plus rapide

- Prénom

- flux

- trouvé

- Portes

- générer

- Matériel

- Haute

- Comment

- HTTPS

- industrie

- d'information

- IT

- langue

- gros

- conduire

- Niveau

- niveaux

- charge

- Location

- Map

- million

- des millions

- nécessaire

- réseau et

- Offres Speciales

- Opérations

- de commander

- Autre

- Papier

- power

- Problème

- Profils

- en cours

- Résultats

- Courir

- pour le running

- économie

- Siemens

- simulation

- Logiciels

- Space

- vitesse

- de Marketing

- streaming

- la quantité

- combustion propre

- tester

- Essais

- tests

- thermique

- Avec

- fiable

- les outils

- unique

- d'habitude

- Site Web

- papier blanc

- travaillé