Les systèmes multi-matrices sont constitués de plusieurs matrices fonctionnelles spécialisées (ou chiplets) assemblées dans le même boîtier pour créer le système complet. Les systèmes multi-puces sont récemment apparus comme une solution pour surmonter le ralentissement de la loi de Moore en fournissant une voie vers la mise à l'échelle des fonctionnalités dans la puce emballée de manière à pouvoir la fabriquer avec un bon rendement.

De plus, les systèmes multi-matrices permettent une flexibilité des SKU de produits en termes d'évolutivité des performances pour répondre aux besoins des différents segments de marché, d'optimisation du nœud de processus par fonction en mélangeant et en faisant correspondre divers nœuds de processus dans le même produit, d'une mise sur le marché plus rapide et d'un risque réduit.

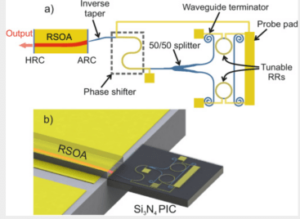

Pour permettre une densité de routage die-to-die plus élevée et prendre en charge un trafic à bande passante plus élevée entre les puces, la technologie des packages a évolué pour créer de nouveaux packages avancés, basés sur des interposeurs de silicium (avec TSV) ou des ponts de silicium et, plus récemment, des couches de redistribution (RDL). , fanouts et substrats HD.

Un aspect clé du succès des systèmes multi-matrices est la capacité à garantir la testabilité du système dans différentes phases de fabrication et d'assemblage, ainsi qu'à garantir un fonctionnement fiable sur le terrain. En utilisant des étapes d'assemblage supplémentaires et des technologies de bumping et d'emballage plus complexes, les systèmes multi-matrices nécessitent des procédures de test et de fiabilité qui vont au-delà de ce qui était l'état de l'art pour les conceptions monolithiques.

Les matrices nues et l'emballage lui-même doivent être pré-testés pour garantir que toutes les matrices ou emballages défectueux sont détectés avant d'être assemblés dans un emballage. Si une puce défectueuse est détectée seulement après l'assemblage, le système multi-matrice complet doit alors être mis au rebut, ce qui a un impact considérable sur les coûts. Le processus de test des matrices nues est appelé test Known Good Die (KGD).

Le processus d'assemblage lui-même varie en fonction de la technologie d'emballage sélectionnée. Par exemple, les technologies de puce d'abord, où les puces sont placées en premier et l'interconnexion est construite par-dessus, ne permettent pas de tester les « boîtiers en bon état », ce qui peut entraîner la mise au rebut des puces en bon état si l'interconnexion est défectueuse. D'autre part, dans les technologies de type puce, où l'interconnexion est construite séparément et les puces sont assemblées dessus, elles permettent de pré-tester le boîtier avant l'assemblage, réduisant ainsi la probabilité que de bonnes puces soient mises au rebut.

La solution de testabilité des systèmes multi-matrices peut être divisée en plusieurs aspects :

- Test de couverture de blocs individuels dans la matrice

- Test de couverture des matrices individuelles (dés nus)

- Test du système assemblé (avec couverture die-to-die)

- Accès au tissu test en matrices nues

- Accès hiérarchique au tissu de test après assemblage

Cet article décrit les avantages d'une solution de testabilité complète qui exploite l'IP UCIe pour garantir la fiabilité du système multi-matrices.

DFT pour l'interface UCIe

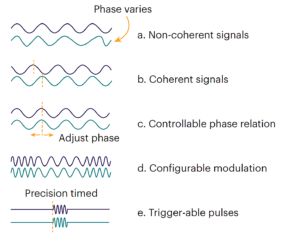

Une solution de couverture de test élevée pour l'interface UCIe est obtenue en implémentant des fonctionnalités de test étendues dans l'IP UCIe pour éliminer les puces défectueuses lors de la phase de test des puces nues. Certaines des fonctionnalités incluent :

- Chaînes de numérisation couvrant tous les circuits numériques synthétisés

- Fonctionnalité BIST spécifique au bloc dédié

- Fonctionnalité d'autotest intégrée (BIST) de bouclage couvrant toute la chaîne de signal jusqu'à la broche IO

- Séquence binaire pseudo-aléatoire programmable (PRBS) et générateurs et vérificateurs de modèles de test définis par l'utilisateur

- Injection d'erreurs pour éliminer les fausses passes

De plus, la fonctionnalité permettant d'étendre la couverture au lien die-to-die, après l'assemblage du boîtier, peut aider à atteindre un niveau élevé de couverture de test, notamment :

- Fonctionnalité de bouclage BIST côté distant (die-to-die)

- Lien die-to-die BIST

- Marge oculaire 2D pour analyser les marginalités

- Fonctionnalité de test et de réparation par voie

Test et réparation UCIe

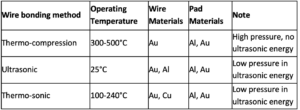

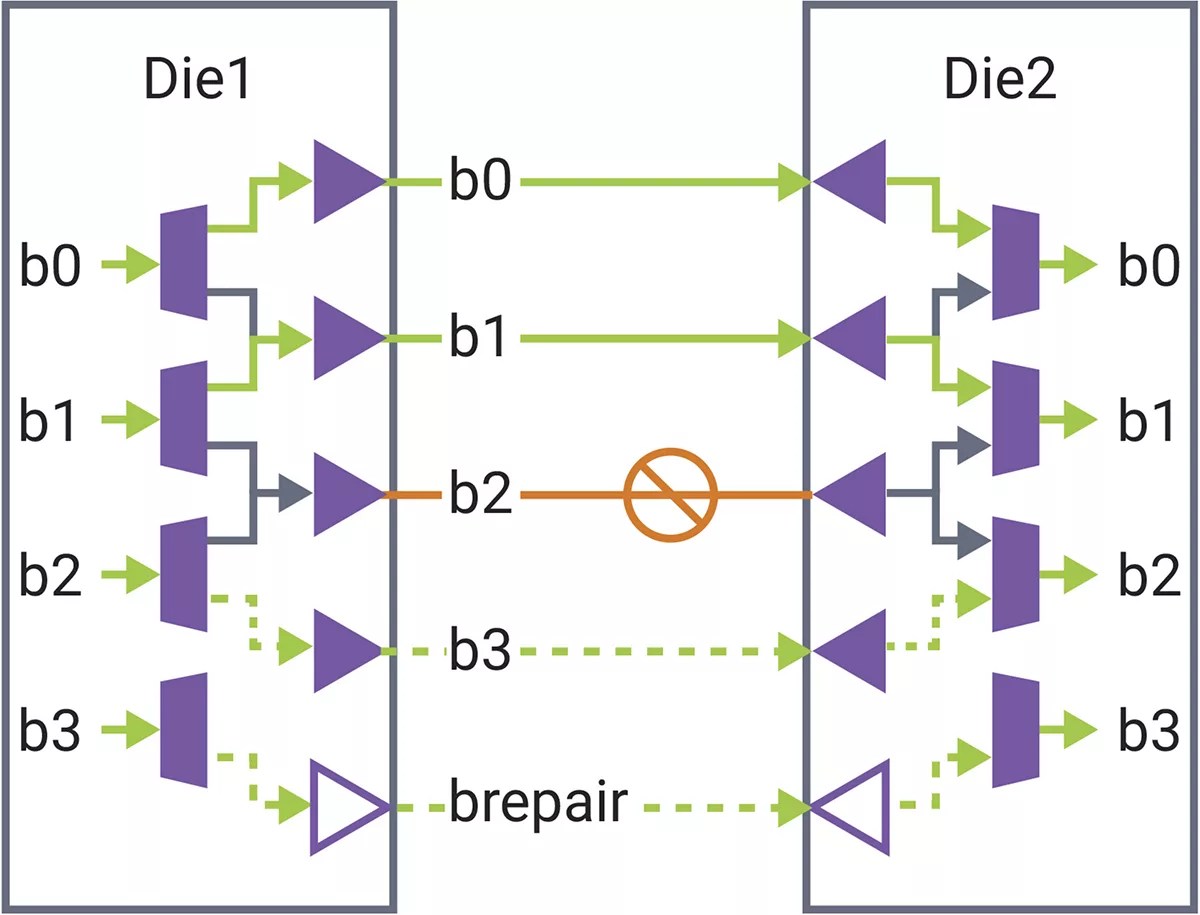

Les packages avancés permettent un routage haute densité avec un micro-bumping à pas fin et un routage sur des interposeurs en silicium ou RDL. Pendant le processus d'assemblage, certaines connexions micro-bosses peuvent ne pas être bien formées et peuvent se briser. UCIe offre la possibilité de tester et de réparer ces connexions après assemblage de manière à récupérer la perte de rendement potentielle.

Le test et la réparation UCIe sont exécutés pendant le test de production et lors de l'initialisation de la liaison. Lors de la phase de test, chaque liaison individuelle est vérifiée à faible vitesse pour déceler les défauts. Les liens défectueux sont réparés en réacheminant les données vers des liens de rechange prédéfinis par la norme UCIe.

Les configurations UCIe ciblant les packages avancés incluent jusqu'à 8 broches de rechange par direction (TX et RX) pour permettre la réparation de tous les liens fonctionnels :

- Quatre broches de rechange pour la réparation des broches de données, 2 broches pour chaque groupe de 32 broches de données

- Une goupille de rechange pour la réparation d'horloges et de goupilles de piste.

- Trois broches de rechange, chacune pour la réparation d'une broche valide, d'une broche de données de bande latérale et d'une broche de données d'horloge.

L'exécution du test et de la réparation a lieu lorsqu'il n'y a pas de trafic valide sur la liaison die-to-die. Une fois la réparation terminée et la liaison initialisée, elle est supposée être bonne et que le trafic peut être acheminé sans problème. La configuration PHY résultante, appelée signature de réparation PHY, est stockée dans des registres internes aux deux extrémités du lien.

La dégradation, due au vieillissement ou autre, des caractéristiques des microbosses pendant le fonctionnement peut avoir un impact sur les performances de la liaison. Cela sera détecté au niveau du protocole par une augmentation du taux d'erreurs binaires (BER) ou, pire encore, par une perte de données. Dans ce cas, la liaison devrait être interrompue et une nouvelle étape de test et de réparation effectuée.

Cependant, certaines applications ont des exigences strictes en termes de continuité du trafic sur la liaison die-to-die : elles ne peuvent tolérer une interruption du trafic pendant le fonctionnement. Pour ces cas, une solution de testabilité ajoute des moniteurs d'intégrité du signal (SIM) à chaque broche du récepteur UCIe.

Fig. 1 : Réparation de liens à l'aide de liens de rechange intégrés.

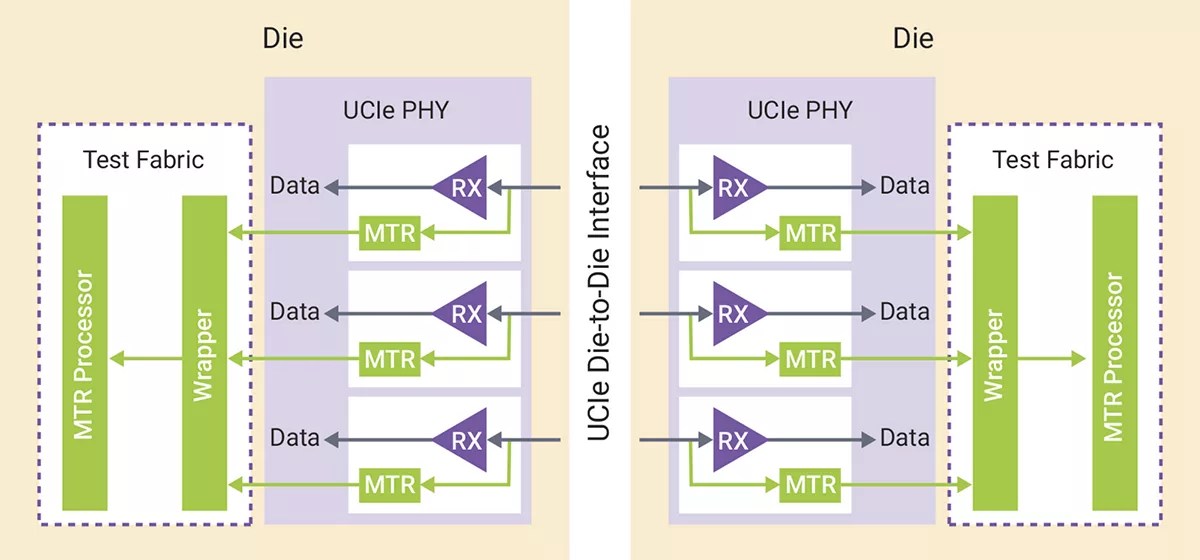

Moniteurs d'intégrité du signal

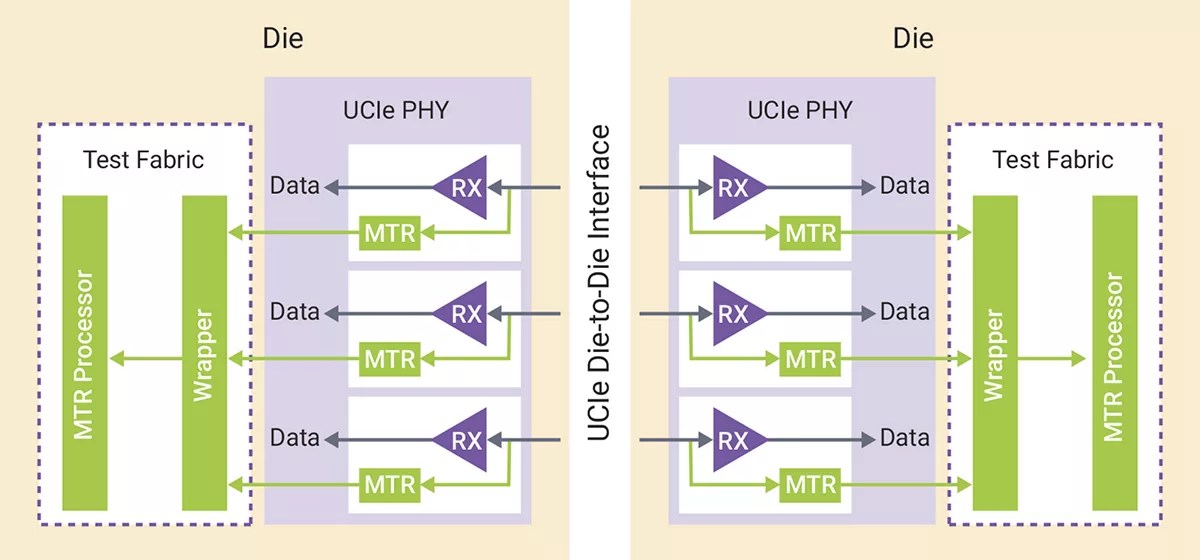

Les moniteurs SIM sont de petits blocs intégrés au récepteur. Ils détectent constamment le signal au niveau de la broche du récepteur, pendant le fonctionnement normal, pour identifier les variations dans les caractéristiques du signal qui peuvent avoir un impact sur les performances de la liaison ou indiquer que la liaison n'est plus saine et pourrait se rompre dans un avenir proche.

Les données collectées par les capteurs individuels sont collectées dans un contrôleur de surveillance, de test et de réparation (MTR), en dehors de l'interface, pour un traitement ultérieur. L'agrégation des données de plusieurs liaisons UCIe peut fournir des informations instantanées sur l'état du système multi-matrices et permettre une maintenance prédictive des liaisons.

Si une liaison spécifique présente un risque de dysfonctionnement grâce à cette procédure, elle peut être désactivée et les données réacheminées vers l'une des liaisons de rechange, en tirant parti du mécanisme de réparation UCIe PHY, même sans interruption du trafic.

Fig. 2 : Solution de surveillance de l'état des liens UCIe.

Accélération du temps de réveil

Alors que le modèle de trafic pour la plupart des cas d'utilisation de l'interface à la mort, par exemple dans le fractionnement ou la mise à l'échelle du serveur, est supposé être stable pendant le fonctionnement, dans certains cas d'utilisation, le trafic peut présenter un comportement par rafales. Dans de tels cas, il est souhaitable de mettre l'interface en mode basse consommation pour économiser de l'énergie lorsqu'il n'y a pas de trafic. La réinitialisation du lien peut être accélérée en évitant le processus de test et de réparation et en s'appuyant sur la signature de réparation UCIe PHY créée lors de l'initialisation PHY précédente.

Ce concept peut être étendu aux situations dans lesquelles la puce est complètement hors tension. Dans ces cas, la signature de réparation PHY est récupérée du PHY et stockée sur une mémoire permanente sur puce (eFuse ou flash). La mémoire pourrait éventuellement stocker plusieurs signatures, couvrant différents cas ou conditions d'utilisation, permettant une flexibilité supplémentaire à l'utilisateur.

Accélérer les tests de puces avec UCIe

Le temps de test est une denrée coûteuse. Il est possible d'accélérer le temps de test en partitionnant la stratégie de test de manière hiérarchique pour exécuter des tests sur différentes matrices en parallèle. La hiérarchie peut être étendue sur plusieurs matrices dans un système multi-matrices en connectant hiérarchiquement l'infrastructure de test des deux matrices. Une telle approche permet d'accéder à toutes les puces du système multi-puces à partir d'une seule interface de test JTAG (ou similaire) dans la puce principale.

Souvent, la limitation de la durée du test est le temps nécessaire pour charger ou lire les vecteurs de test dans les matrices. Les interfaces JTAG peuvent devenir un goulot d'étranglement en termes de vitesse. Pour surmonter cette limitation, les concepteurs peuvent utiliser des interfaces haut débit existantes telles que PCI Express (PCIe) ou USB, etc. comme interfaces avec l'équipement de test. Les vecteurs de test et les commandes sont mis en paquets pour cette interface et dépacketisés sur la puce pendant la phase de test de production.

De nombreuses puces ne disposent pas d'une interface haute vitesse. Cependant, l'interface puce-à-puce UCIe peut être utilisée, pendant le test, pour transporter de grands vecteurs de test et des commandes entre les puces à grande vitesse. L'interface die-to-die UCI étend l'accès DFT haut débit à l'ensemble du système multi-puces sans augmenter le nombre de broches, ce qui est particulièrement important pour les puces d'E/S et à zone limitée.

Résumé

Outre l'interface die-to-die UCIe, le dénominateur commun qui permet toutes ces fonctionnalités de test et d'amélioration de la fiabilité est une structure de test, de réparation et de surveillance capable de connecter tous les blocs internes. Le tissu de test, de réparation et de surveillance couvre les différentes matrices du système multi-matrices, fournissant une infrastructure hiérarchique structurée qui remplit les fonctions importantes suivantes :

- Gère les tests des matrices individuelles dans le système multi-matrices

- Optimise la planification des tests pour réduire la durée des tests

- Prend en charge l'accès aux tests à grande vitesse sur les matrices, via l'interface UCIe

- Collecte des informations à partir des interfaces de surveillance de l'état intégrées dans l'interface UCIe et permet un traitement ultérieur au niveau du système.

- Gère le stockage de la signature de réparation PHY dans une mémoire non volatile

- Et plus encore

Synopsys fournit une solution système multi-puces complète et évolutive, comprenant EDA et IP, pour une intégration hétérogène rapide. Pour une connectivité die-to-die sécurisée et fiable, Synopsys propose une solution complète de contrôleur UCIe, PHY et IP de vérification. Dans le cadre de la famille Synopsys SLM & Test, une solution complète de surveillance, de test et de réparation (MTR) UCIe est disponible ainsi que la solution STAR Hierarchical System (SHS). La solution MTR comprend un moniteur d'intégrité du signal pour mesurer la qualité du signal sur les voies UCIe, un BIST pour l'auto-test et une logique de réparation pour l'attribution de voies redondantes, tandis que la solution SHS sert de tissu de connectivité prenant en charge les normes industrielles IEEE 1687, IEEE 1149.1 et IEEE 1838. interfaces. Cette solution complète permet une surveillance efficace et rentable de l’état de l’UCIe pendant toutes les phases du cycle de vie du silicium, ce qui est essentiel pour un fonctionnement fiable des systèmes multi-puces.

Ressources:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoAiStream. Intelligence des données Web3. Connaissance Amplifiée. Accéder ici.

- Frapper l'avenir avec Adryenn Ashley. Accéder ici.

- Achetez et vendez des actions de sociétés PRE-IPO avec PREIPO®. Accéder ici.

- La source: https://semiengineering.com/from-known-good-die-to-known-good-system-with-ucie-ip/

- :possède

- :est

- :ne pas

- :où

- $UP

- 1

- 8

- a

- capacité

- accélérer

- accéléré

- accès

- atteindre

- atteint

- Atteint

- à travers

- ajout

- Supplémentaire

- Ajoute

- Avancée

- Après

- anti-âge

- Tous

- allocation

- permettre

- permet

- le long de

- an

- il analyse

- ainsi que

- applications

- une approche

- SONT

- article

- AS

- d'aspect

- aspects

- assemblé

- Assemblée

- assumé

- At

- disponibles

- en évitant

- Bande passante

- basé

- BE

- devenez

- before

- va

- qui ne s'occupent pas de leur chez-soi.

- jusqu'à XNUMX fois

- Au-delà

- Block

- Blocs

- tous les deux

- Pause

- ponts

- apporter

- construit

- intégré

- by

- appelé

- CAN

- ne peut pas

- maisons

- cas

- chaîne

- Chaînes

- caractéristiques

- vérifié

- puce

- horloge

- Horloges

- marchandise

- Commun

- complet

- complètement

- complexe

- complet

- concept

- conditions

- configuration

- NOUS CONTACTER

- Connecter les

- Connexions

- Connectivité

- constamment

- contrôleur

- Prix

- rentable

- pourriez

- couverture

- couvrant

- engendrent

- créée

- critique

- données

- défini

- densité

- designers

- Avec nos Bagues Halo

- détecté

- J'ai noté la

- différent

- numérique

- direction

- handicapé

- divisé

- do

- down

- deux

- pendant

- chacun

- efficace

- éliminé

- intégré

- émergé

- permettre

- permet

- permettant

- se termine

- Ce renforcement

- assurer

- assurer

- l'équipements

- etc

- Ether (ETH)

- Pourtant, la

- évolué

- exemple

- exécution

- exposer

- existant

- attendu

- cher

- express

- étendre

- les

- supplémentaire

- œil

- .

- non

- famille

- RAPIDE

- plus rapide

- défectueux

- Fonctionnalités:

- champ

- fin

- Prénom

- Flash

- Flexibilité

- Abonnement

- Pour

- formé

- de

- fonction

- fonctionnel

- fonctions

- plus

- avenir

- recueillies

- générateurs

- Go

- Bien

- Réservation de groupe

- main

- Vous avez

- Santé

- la santé

- aider

- hiérarchie

- Haute

- augmentation

- Cependant

- HTTPS

- identifier

- IEEE

- if

- Impact

- la mise en œuvre

- important

- in

- comprendre

- inclut

- Y compris

- Améliore

- croissant

- indiquer

- individuel

- industrie

- d'information

- Infrastructure

- idées.

- instantané

- l'intégration

- intégrité

- Interfaces

- interfaces

- interne

- interrompu

- développement

- IP

- IT

- lui-même

- clés / KEY :

- connu

- Voie

- gros

- Droit applicable et juridiction compétente

- poules pondeuses

- Niveau

- les leviers

- en tirant parti

- vos produits

- limitation

- LINK

- Gauche

- charge

- logique

- plus long

- perte

- perdu

- Faible

- LES PLANTES

- Entrée

- facile

- Marché

- Match

- assorti

- largeur maximale

- Mai..

- mesure

- mécanisme

- Mémoire

- Mode

- Surveiller

- Stack monitoring

- moniteurs

- Monolithique

- PLUS

- (en fait, presque toutes)

- MTR

- plusieurs

- must

- Près

- Besoins

- Nouveauté

- aucune

- nœud

- nœuds

- Ordinaire

- nombre

- of

- Offres Speciales

- on

- ONE

- uniquement

- opération

- à mettre en œuvre pour gérer une entreprise rentable. Ce guide est basé sur trois décennies d'expérience

- or

- Autre

- ande

- au contrôle

- Overcome

- paquet

- emballé

- Forfaits

- l'emballage

- Parallèle

- partie

- particulièrement

- passé

- chemin

- Patron de Couture

- motifs

- performant

- permanent

- phase

- broches

- Emplacement

- Platon

- Intelligence des données Platon

- PlatonDonnées

- possible

- peut-être

- défaillances

- l'éventualité

- power

- alimenté

- prédit

- précédent

- Avant

- probabilité

- d'ouvrabilité

- procédures

- processus

- traitement

- Produit

- Vidéo

- protocole

- fournir

- fournit

- aportando

- qualité

- Tarif

- Lire

- récemment

- Récupère

- réduire

- réduire

- registres

- fiabilité

- fiable

- réparation

- exigent

- Exigences

- résultant

- Analyse

- routage

- Courir

- RX

- même

- Épargnez

- évolutive

- mise à l'échelle

- ordonnancement

- sécurisé

- segments

- choisi

- capteur

- Séquence

- grave

- sert

- plusieurs

- devrait

- côté

- Signal

- Signatures

- Silicium

- OUI

- similaires

- unique

- situations

- lent

- Le ralentissement de la

- petit

- sur mesure

- quelques

- travées

- spécialisé

- groupe de neurones

- vitesse

- stable

- Standard

- Étoile

- state-of-the-art

- étapes

- Étapes

- storage

- Boutique

- stockée

- de Marketing

- structuré

- succès

- tel

- Support

- Appuyer

- combustion propre

- Système

- ciblage

- Les technologies

- Technologie

- conditions

- tester

- Essais

- tests

- qui

- La

- Les

- puis

- Là.

- Ces

- l'ont

- this

- Avec

- fiable

- à

- top

- suivre

- circulation

- transportant

- deux

- TX

- usb

- utilisé

- d'utiliser

- Utilisateur

- en utilisant

- divers

- Vérification

- via

- était

- Façon..

- webp

- WELL

- Quoi

- quand

- qui

- tout en

- sera

- avec

- dans les

- sans

- pire

- Rendement

- zéphyrnet