Les chiplets ont simplifié un domaine de conception mais ont ouvert la boîte de Pandore sur un autre front. La complexité de simulation de chacun chiplet est inférieur, mais l'interconnexion chiplet à chiplet est désormais devenue complexe. Les gens expérimentent différents protocoles d'interconnexion, variantes d'UCIe, modifiant les paramètres UCIe, les vitesses d'interface, le nombre de couches physiques, etc. Ajoutez désormais des normes héritées comme AXI, de nouveaux protocoles comme PICe6.0 et la cohérence du cache à l'ensemble.

Dans l’ensemble, cela crée un tout nouvel ensemble d’expériences. Celui pour lequel l’émulation traditionnelle et la modélisation RTL ne fonctionneront pas. Vous devez d’abord faire un effort sur le compromis architectural, et pas seulement sur la sélection des composants. Cela signifie que vous devrez effectuer une analyse du trafic, le partitionnement des applications, le dimensionnement du système et l'impact des différents types de couche physique. De plus, selon l'application, le benchmark sera très différent.

La spécification UCIe est nouvelle et il n’existe pas de références claires. De plus, la spécification UCIe ne fournit que des indications sur la latence et la puissance. Ces deux exigences sont strictes. Cela signifie qu’une étude puissance-performance-zone est inévitable. Comme vous disposez d'une conversion protocole-protocole-protocole telle que PCIe 6.0 vers UCIe vers AXI, la configuration de modélisation est complexe.

Une solution consiste à étudier la modélisation du système en utilisant VisualSim De Mirabilis Conception. Ils ont récemment lancé un modèle IP au niveau du système UCIe et démontreront un certain nombre de cas d'utilisation de l'interconnexion au Sommet des Chiplets. Pour guider les concepteurs, ils ont publié un guide présentant de nombreux cas d'utilisation, les résultats attendus en termes de performances énergétiques et d'options d'optimisation. Ils ont à la fois une présentation papier et un stand au Sommet. J'espère te voir là-bas!

Voici également le lien vers un article que les gens peuvent obtenir : Modélisation des performances d'un système informatique hétérogène basé sur l'architecture d'interconnexion UCIe

Résumé:

Les conceptions de puces complexes d'aujourd'hui sur les nœuds de pointe se composent généralement de plusieurs puces (ou chiplets). L’approche permet d’utiliser des matrices provenant de différents fabricants ou processus, ainsi que des IP réutilisables. Les concepteurs ont besoin d'un modèle au niveau du système pour évaluer différentes implémentations de situations aussi complexes.

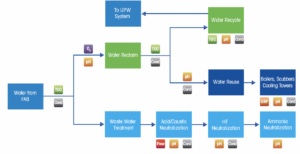

Un exemple de système est constitué d'un chiplet d'E/S, d'un chiplet central à faible consommation, d'un chiplet central hautes performances, d'un chiplet audio-vidéo et d'un chiplet analogique, interconnectés à l'aide de la norme Universal Chiplet Interconnect Express (UCIe).

Notre équipe a envisagé plusieurs scénarios et configurations, notamment des packages avancés et standard, des profils de trafic et des ressources variés, ainsi qu'un retimer pour étendre la portée et évaluer les événements en cas d'expiration. L'identification des forces et des faiblesses de l'interconnexion UCIe pour les applications de mission nous a aidé à obtenir la configuration optimale pour chaque sous-système afin de répondre aux exigences de performances, de puissance et de fonctionnalité.

À propos de Mirabilis Design Inc.

Mirabilis Design est une société de logiciels de la Silicon Valley qui fournit des logiciels et des solutions de formation pour identifier et éliminer les risques liés aux spécifications du produit, prédire avec précision les ressources humaines et temporelles nécessaires au développement du produit et améliorer la communication entre les différents ingénieurs.

équipes.

VisualSim Architect combine la propriété intellectuelle, la modélisation au niveau du système, la simulation, l'analyse de l'environnement et les modèles d'application pour améliorer considérablement la construction, la simulation, l'analyse et la vérification RTL des modèles. L'environnement permet aux concepteurs de converger rapidement vers une conception qui répond à un ensemble diversifié d'exigences interdépendantes en matière de temps et de puissance. Il est utilisé très tôt dans le processus de conception en parallèle (et comme aide à) la spécification écrite et avant une mise en œuvre (par exemple, RTL, code logiciel ou schéma) du produit.

Lisez aussi:

Mappage de SysML à l'architecture matérielle

Cours de conception basée sur des modèles pour étudiants

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/ip/mirabilis-design-ip/341339-chiplets-open-pandoras-box/

- :possède

- :est

- :ne pas

- a

- Avec cette connaissance vient le pouvoir de prendre

- avec précision

- atteindre

- ajouter

- Avancée

- Aide

- permet

- le long de

- aussi

- an

- selon une analyse de l’Université de Princeton

- ainsi que le

- Une autre

- Application

- applications

- une approche

- architecture

- SONT

- Réservé

- AS

- At

- basé

- BE

- devenez

- before

- référence

- repères

- jusqu'à XNUMX fois

- tous les deux

- Box

- mais

- cachette

- CAN

- Peut obtenir

- cas

- puce

- clair

- code

- moissonneuses-batteuses

- Communication

- Société

- complètement

- complexe

- complexité

- composants électriques

- informatique

- Conduire

- configuration

- considéré

- consiste

- construction

- converger

- Conversion

- Core

- cours

- crée des

- démontrer

- Selon

- Conception

- procédé de design

- designers

- Avec nos Bagues Halo

- développer

- différent

- plusieurs

- pendant

- chacun

- "Early Bird"

- effort

- éliminé

- émulation

- permet

- Environment

- évaluer

- événements

- exemple

- attendu

- l'expérimentation

- expériences

- express

- étendre

- Prénom

- Pour

- De

- avant

- fonctionnel

- généralement

- obtenez

- l'orientation

- guide

- Matériel

- Vous avez

- a aidé

- ici

- haute performance

- d'espérance

- Comment

- How To

- HTTPS

- humain

- i

- identifier

- identifier

- Impact

- la mise en oeuvre

- implémentations

- améliorer

- in

- Y compris

- intellectuel

- propriété intellectuelle

- interconnecté

- Interfaces

- IP

- IT

- jpg

- juste

- Latence

- lancé

- couche

- poules pondeuses

- Legacy

- Niveau

- comme

- LINK

- Style

- beaucoup

- Faible

- baisser

- Fabricants

- largeur maximale

- signifier

- veux dire

- mesures

- Découvrez

- Se rencontre

- Mission

- mélanger

- modèle

- modélisation statistique

- la modélisation

- plusieurs

- Besoin

- Nouveauté

- aucune

- nœuds

- maintenant

- nombre

- obtenir

- of

- on

- ONE

- uniquement

- ouvert

- ouvert

- optimaux

- à mettre en œuvre pour gérer une entreprise rentable. Ce guide est basé sur trois décennies d'expérience

- Options

- or

- Forfaits

- Papier

- Parallèle

- performant

- Physique

- Platon

- Intelligence des données Platon

- PlatonDonnées

- Post

- power

- prévoir

- présentation

- processus

- les process

- Produit

- Profils

- propriété

- protocoles

- fournit

- aportando

- publié

- rapidement

- nous joindre

- Lire

- récemment

- conditions

- Exigences

- Resources

- Résultats

- réutilisable

- Analyse

- scénarios

- sur le lien

- la sélection

- set

- Paramétres

- installation

- plusieurs

- de façon significative

- Silicium

- Silicon Valley

- simplifié

- simulation

- situations

- So

- Logiciels

- sur mesure

- Solutions

- spécification

- vitesses

- passer

- Standard

- Normes

- forces

- strict

- Étude

- tel

- Sommet

- combustion propre

- équipe

- modèles

- qui

- La

- Là.

- l'ont

- this

- fiable

- à

- traditionnel

- circulation

- Formation

- types

- Universel

- us

- utilisé

- d'utiliser

- en utilisant

- Vallée

- variations

- Vérification

- très

- via

- faiblesses

- WELL

- qui

- sera

- comprenant

- activités principales

- code écrit

- you

- zéphyrnet