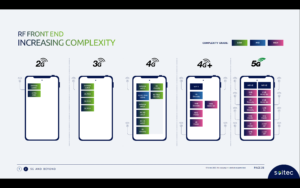

در راهپیمایی به سوی سیستمهای توانمندتر، سریعتر، کوچکتر و کمتر، قانون مور به نرمافزار یک سواری رایگان برای بیش از 30 سال یا بیشتر، صرفاً بر روی تکامل فرآیند نیمهرسانا داد. سختافزار محاسباتی هر سال معیارهای بهبود عملکرد/منطقه/قدرت را ارائه میدهد، که به نرمافزار اجازه میدهد پیچیدگی خود را گسترش دهد و قابلیتهای بیشتری را بدون هیچ جنبه منفی ارائه دهد. سپس بردهای آسان کمتر آسان شدند. فرآیندهای پیشرفته تر به ارائه تعداد گیت های بالاتر در واحد سطح ادامه دادند، اما افزایش عملکرد و قدرت شروع به کاهش یافت. از آنجایی که انتظارات ما برای نوآوری متوقف نشد، پیشرفتهای معماری سختافزار در برداشتن این سستی اهمیت بیشتری یافته است.

محرک هایی برای افزایش تعداد هسته

در گام اولیه در این مسیر، از CPUهای چند هستهای برای تسریع توان عملیاتی کل با استفاده از رشته یا مجازیسازی ترکیبی از وظایف همزمان در هستهها استفاده میشود، و در صورت نیاز با خاموش کردن یا خاموش کردن هستههای غیرفعال، توان را کاهش میدهد. امروزه چند هستهای استاندارد است و روند در چند هستهای (حتی پردازندههای بیشتر روی یک تراشه) از قبل در گزینههای نمونه سرور موجود در پلتفرمهای ابری از AWS، Azure، Alibaba و دیگران مشهود است.

معماریهای چند هستهای/چند هستهای یک گام به جلو هستند، اما موازیسازی از طریق خوشههای CPU درشت دانه است و به لطف قانون Amdahl محدودیتهای عملکرد و قدرت خاص خود را دارد. معماری ها ناهمگن تر شدند و شتاب دهنده هایی برای تصویر، صدا و سایر نیازهای تخصصی اضافه کردند. شتابدهندههای هوش مصنوعی همچنین موازیسازی ریزدانهای را پیش بردهاند و به سمت آرایههای سیستولیک و سایر تکنیکهای خاص حوزه حرکت کردهاند. که تا زمانی که ChatGPT با 175 میلیارد پارامتر با GPT-3 تبدیل به GPT-4 با 100 تریلیون پارامتر - مرتباً پیچیده تر از سیستم های هوش مصنوعی امروزی - ظاهر شد - ChatGPT با XNUMX میلیارد پارامتر ظاهر شد.

از جنبه ای دیگر، سیستم های چند سنسوری در برنامه های خودرو اکنون در حال ادغام در SoC های منفرد برای بهبود آگاهی محیطی و بهبود PPA هستند. در اینجا، سطوح جدید استقلال در خودرو به ترکیب ورودیهای چندین سنسور در یک دستگاه واحد، در زیرسیستمهایی که با 2X، 4X یا 8X تکرار میشوند، بستگی دارد.

به گفته Michał Siwinski (CMO در Arteris)، نمونهبرداری بیش از یک ماه از بحث با تیمهای طراحی متعدد در طیف گستردهای از برنامهها نشان میدهد که این تیمها فعالانه به سمت تعداد هستههای بالاتر روی میآورند تا اهداف توانایی، عملکرد و قدرت را برآورده کنند. او به من می گوید که آنها نیز شاهد شتاب گرفتن این روند هستند. پیشرفتهای فرآیند هنوز به تعداد گیتهای SoC کمک میکند، اما مسئولیت رسیدن به اهداف عملکرد و قدرت اکنون کاملاً در دست معماران است.

هسته های بیشتر، اتصال بیشتر

هسته های بیشتر روی یک تراشه به معنای اتصال داده های بیشتری بین آن هسته ها است. در یک شتاب دهنده بین عناصر پردازش همسایه، به حافظه پنهان محلی، به شتاب دهنده ها برای ماتریس پراکنده و سایر پردازش های تخصصی. اتصال سلسله مراتبی بین کاشی های شتاب دهنده و اتوبوس های سطح سیستم را اضافه کنید. برای ذخیره وزن روی تراشه، فشرده سازی، پخش، جمع آوری و فشرده سازی مجدد، اتصال اضافه کنید. اتصال HBM را برای حافظه پنهان اضافه کنید. در صورت نیاز یک موتور فیوژن اضافه کنید.

خوشه کنترل مبتنی بر CPU باید به هر یک از آن زیرسیستمهای تکراری و به همه عملکردهای معمول متصل شود - کدکها، مدیریت حافظه، جزیره ایمنی و ریشه اعتماد در صورت لزوم، UCIe در صورت پیادهسازی چند تراشه، PCIe برای I/O با پهنای باند بالا. و اترنت یا فیبر برای شبکه.

این ارتباط بسیار زیادی است که پیامدهای مستقیمی برای بازارپسندی محصول دارد. در فرآیندهای زیر 16 نانومتر، زیرساخت NoC اکنون 10 تا 12 درصد در منطقه مشارکت دارد. مهمتر از آن، به عنوان بزرگراه ارتباطی بین هسته ها، می تواند تأثیر قابل توجهی بر عملکرد و قدرت داشته باشد. این خطر واقعی وجود دارد که یک پیادهسازی زیر بهینه، عملکرد معماری و قدرت مورد انتظار را هدر دهد، یا بدتر از آن، منجر به ایجاد حلقههای طراحی مجدد متعدد برای همگرایی شود. با این حال، یافتن یک پیادهسازی خوب در یک پلان پیچیده SoC همچنان به بهینهسازیهای آهسته آزمون و خطا در برنامههای طراحی از قبل فشرده بستگی دارد. ما باید به طراحی NoC آگاه از لحاظ فیزیکی جهش کنیم، تا عملکرد کامل و پشتیبانی قدرت از سلسله مراتب پیچیده NoC را تضمین کنیم و باید این بهینهسازیها را سریعتر انجام دهیم.

طراحی های NoC آگاه از نظر فیزیکی، قانون مور را در مسیر خود نگه می دارد

قانون مور ممکن است مرده نباشد، اما پیشرفتها در عملکرد و قدرت امروزه به جای فرآیند، از معماری و اتصال NoC ناشی میشود. معماری هستههای شتابدهندههای بیشتری، شتابدهندههای بیشتر در شتابدهندهها و تکثیر زیرسیستمهای بیشتری روی تراشه را فشار میدهد. همه پیچیدگی اتصال درون تراشه را افزایش می دهند. همانطور که طرح ها تعداد هسته ها را افزایش می دهند و به سمت هندسه های پردازشی در 16 نانومتر و پایین تر حرکت می کنند، اتصالات متعدد NoC که روی SoC و زیرسیستم های آن را پوشانده اند، تنها در صورتی می توانند از پتانسیل کامل این طرح های پیچیده پشتیبانی کنند که به طور بهینه در برابر محدودیت های فیزیکی و زمان بندی - از طریق شبکه آگاه فیزیکی اجرا شوند. در طراحی تراشه

اگر شما نیز نگران این روندها هستید، ممکن است بخواهید در مورد فناوری IP Arteris FlexNoC 5 اطلاعات بیشتری کسب کنید اینجا.

اشتراک گذاری این پست از طریق:

- محتوای مبتنی بر SEO و توزیع روابط عمومی. امروز تقویت شوید.

- پلاتوبلاک چین. Web3 Metaverse Intelligence. دانش تقویت شده دسترسی به اینجا.

- منبع: https://semiwiki.com/artificial-intelligence/326727-interconnect-under-the-spotlight-as-core-counts-accelerate/

- :است

- $UP

- 100

- a

- درباره ما

- شتاب دادن

- تسریع

- شتاب

- شتاب دهنده

- شتاب دهنده ها

- در میان

- فعالانه

- پیشرفته

- پیشرفت

- در برابر

- AI

- سیستم های هوش مصنوعی

- علی بابا

- معرفی

- اجازه دادن

- قبلا

- و

- به نظر می رسد

- برنامه های کاربردی

- مناسب

- معماری

- هستند

- محدوده

- AS

- At

- سمعی

- خودرو

- در دسترس

- اطلاع

- AWS

- لاجوردی

- پهنای باند

- BE

- شدن

- در زیر

- میان

- بیلیون

- پخش

- اتوبوس

- by

- نهانگاه

- CAN

- توانا

- GPT چت

- تراشه

- ابر

- خوشه

- CMO

- بیا

- ارتباط

- پیچیده

- پیچیدگی

- محاسبه

- رقیب

- اتصال

- اتصالات

- اتصال

- عواقب

- محدودیت ها

- ادامه داد:

- کنترل

- همگرا

- هسته

- پردازنده

- خطر

- داده ها

- مرده

- ارائه

- تحویل داده

- بستگی دارد

- طرح

- طرح

- دستگاه

- مختلف

- مستقیم

- جهت

- بحث و گفتگو

- پایین

- سقوط

- هر

- در اوایل

- عناصر

- موتور

- محیط

- حتی

- هر

- تکامل

- در حال تحول

- گسترش

- انتظارات

- انتظار می رود

- سریعتر

- امکانات

- پیدا کردن

- محکم

- برای

- به جلو

- رایگان

- از جانب

- جلو

- کامل

- توابع

- ادغام

- عایدات

- اهداف

- خوب

- ضمانت

- اداره

- دست ها

- سخت افزار

- آیا

- کمک

- اینجا کلیک نمایید

- زیاد

- بالاتر

- بزرگراه

- HTTPS

- تصویر

- تأثیر

- پیاده سازی

- اجرا

- مهم

- بهبود یافته

- in

- غیر فعال

- افزایش

- افزایش

- شالوده

- ابداع

- نمونه

- ادغام

- IP

- جزیره

- IT

- ITS

- پرش

- قانون

- یاد گرفتن

- سطح

- سطح

- محدودیت

- محلی

- خیلی

- ساخت

- مدیریت

- مارس

- ماتریس

- حداکثر عرض

- دیدار

- نشست

- حافظه

- متریک

- قدرت

- ماه

- بیش

- حرکت

- متحرک

- چندگانه

- نیاز

- ضروری

- نیازهای

- شبکه

- شبکه

- جدید

- متعدد

- of

- on

- گزینه

- سفارشات

- دیگر

- دیگران

- خود

- پارامترهای

- کارایی

- فیزیکی

- از نظر جسمی

- سیستم عامل

- افلاطون

- هوش داده افلاطون

- PlatoData

- پست

- پتانسیل

- قدرت

- برق

- زیبا

- روند

- فرآیندهای

- در حال پردازش

- محصول

- صرفا

- تحت فشار قرار دادند

- هل دادن

- محدوده

- نسبتا

- واقعی

- کاهش

- تکرار شده

- تکرار

- مسئوليت

- نتیجه

- سوار شدن

- ریشه

- ایمنی

- نیمه هادی

- قابل توجه

- پس از

- تنها

- شل

- کند

- کوچکتر

- So

- نرم افزار

- ماتریس پراکنده

- تخصصی

- نور افکن

- استاندارد

- آغاز شده

- گام

- هنوز

- توقف

- ذخیره سازی

- حاکی از

- پشتیبانی

- سیستم

- سیستم های

- وظایف

- تیم ها

- تکنیک

- پیشرفته

- می گوید

- که

- La

- اینها

- از طریق

- توان

- زمان

- به

- امروز

- امروز

- جمع

- روند

- روند

- تریلیون

- اعتماد

- عطف

- انواع

- زیر

- واحد

- از طريق

- وزن

- خوب

- که

- وسیع

- دامنه گسترده

- اراده

- برنده

- با

- در داخل

- کارگر

- سال

- سال

- زفیرنت